- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种用于飞行器下高速数据采集存储系统设计

0 引言

随着遥感技术的发展,遥感图像的分辨率也越来越高。飞行器上搭载的遥感成像设备也从过去的低分辨率向现在的高分辨率在转变。遥感成像设备分辨率提高的同时,也对飞行器的数据下传链路提出了更高的带宽要求。而相应的地面数据接受设备,也需要具备对高速实时数据的存储和处理能力。同样在测试设备方面,为了对大容量存储设备进行高速数据的传输测试,相应的地面检测设备也应该具备高速数据的输出功能。因此,急需开发出具备高速实时数据接收和高速数据输出功能的高速数据采集存储系统。

从目前此类系统的技术指标来看,往往只能达到100Mbps到150Mbps的数据接收和数据输出功能。而根据目前的应用需求来看,高速数据流的数据传输速率往往在200Mbps以上甚至达到300Mbps。对于这种高速数据流,目前的系统就难以连续无错的进行存储和处理,往往会因为数据传输速率超过系统能处理的极限,导致出现丢失数据或者系统功能不正常,状态不稳定等问题。

本文中介绍的高速数据采集存储系统的设计目标就是对传输速率最高为300Mbps的数据流进行无错接收存储,并能实现最高为300Mbps的高速数据流输出,以便于对大容量存储设备进行检测。

1 系统总体介绍

高速数据采集存储系统是在32位的计算机系统上实现的,数据传输也是利用32位,33MHz的PCI总线来完成。数据存储是利用两块SATA接口的硬盘组成的RAID0磁盘阵列来实现的。整个系统的核心是数据传输接口卡,它完成外部数据到计算机内存的传输。然后运行的驱动程序再将内存中的数据存储到硬盘上。因此,整个系统的设计也就分为数据传输接口卡的设计和驱动及应用程序设计两大部分。

2 数据传输接口卡设计

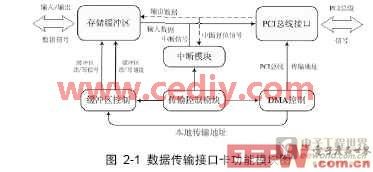

数据传输接口卡从功能上分为PCI总线接口,存储缓冲区,中断模块,传输控制模块,缓冲区控制以及DMA控制六个模块,如图2-1中所示。当工作于数据输入时,传输控制模块根据缓冲区情况启动传输,传输过程中缓冲区控制模块将数据读出送到PCI总线上,DMA控制模块控制着PCI总线上数据传输的进行。传输结束以后,中断模块发出中断信号提示驱动程序对传输到内存中的数据进行处理。下面主要介绍PCI总线接口模块,DMA控制模块,存储缓冲区模块以及传输控制模块几个核心模块的设计。

2.1 PCI总线接口模块的设计

PCI总线接口模块完成的工作主要是PCI总线命令的解码,地址以及数据的锁存。实现PCI接口常用的方法是采用现成的PCI总线接口协议芯片(PLX905X系列等),如文献[2]中数据采集板的设计就是采用的这种方法。但是由于这些协议芯片往往不是针对空间应用而专门开发的,从可靠性方面考虑,不能采用这种设计方案。在本方案中,整个接口的设计是在使用Xilinx公司提供的LogiCORE PCI v3.0的IP核(IP Core)的基础上实现的。LogiCORE PCI v3.0是Xilinx公司提供的用于PCI总线接口设计的IP 核,在它的基础上可以根据实际应用的需要很方便的定制和实现PCI总线接口。由于IP 核本身实现了配置空间以及总线命令的解码和地址的锁存,所以设计者只需要专注于PCI传输状态机和本地控制信号的设计。采用这种实现方式虽然比直接使用PCI接口专用芯片更为复杂,但是整个设计可以集成于一片高可靠性的FPGA之中,从而有效的提高了整个设计的可靠性。

2.2 DMA控制模块的设计

为了满足高速率数据传输的需要,并且在数据传输的同时不占用CPU,所以必须采用DMA的方式来传输数据。由于PCI总线上的DMA传输是通过PCI设备本身的DMA控制功能来完成的,而不是依靠总线上单独的DMA控制设备来实现,所以在设计时必须实现DMA控制模块。DMA控制模块在数据传输周期发出控制命令以及更新地址。其中传输地址控制可以依赖一组传输地址寄存器来实现,而传输的控制可以通过PCI传输状态机给出的信号来产生控制信号。

2.3 存储缓冲区模块的设计

为了保证数据的连续不间断传输,每次传输只传输半个缓冲区的数据,而外部数据总是在两个半区之间切换储存,因此不会造成数据的丢失和不连续。 [p]

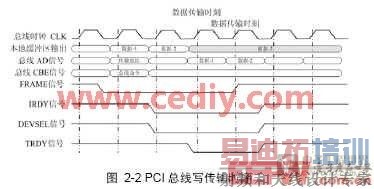

一个典型的PCI总线上的写数据传输时序如图2-2中所示。首先用于传输的数据必须要提前从本地的缓冲区中读出,然后出现在总线AD信号线上,当IRDY信号和TRDY信号同时有效时(为低电平时),被目标设备获取。当传输结束时,最后一个从本地缓冲区中预读出的数据(如图中阴影的数据3),并不会被传输到目标设备。而本地的缓冲区控制模块会认为数据已经传输,这时如果不采取措施就会导致数据丢失。

在传输结束的时候,PCI总线传输状态机会切换到备份数据的状态,在这个状态下,缓冲区的控制模块会检测是否存在已经读出而未传输的数据,如果存在这样的情况,控制模块则采取措施防止数据丢失。对于双口RAM这种存储结构而言,数据读出以后,只要没有在同一地址写入数据,那么数据是不会丢失的,因此要实现前面的功能只需要简单的修改一下读指针目前指向的地址就可以实现。

2.4 传输控制模块的设计

传输控制模块的核心是一个传输控制状态机。它通过检测存储缓冲区的情况,来控制传输的进行。当输入缓冲区中数据存储满或输出缓冲区空以后,自动请求一次数据传输,由此保证数据流的连续。

3 驱动与应用程序的开发

驱动程序的开发是采用标准的WDM(Windows Driver Model)设备驱动程序模型,利用DriverStudio的驱动程序开发工具包来进行开发的。关于WDM的驱动程序模型,限于篇幅的原因就不作详细的介绍。

一个典型的数据传输过程是这样进行的。首先驱动程序完成设备的初始化,如在内存中开辟缓冲区,硬件设备的初始化等等。完成初始化以后硬件就处于等待传输的状态。当用户通过应用程序发出传输数据的指令以后,驱动程序处理这一请求,并对硬件发出指令开始数据传输。由于数据传输的时间可能比较长,所以应用程序采用多线程的设计,传输线程会等待驱动程序在传输结束时发出的信号,而同时应用程序还能完成与用户的交互工作。当传输结束后,驱动程序向硬件写入停止指令,中止传输,并向应用程序发出传输结束信号。驱动程序对应用程序的通信是通过创建Win32事件来实现通信的。

4 设计的仿真和验证

为了验证设计的正确性,首先需要对设计进行逻辑功能仿真。为了验证设计是否能正常的工作在PCI总线上,那么就需要仿真PCI总线上的各种总线事务,验证设计是否能响应各种总线命令。仿真是在Xilinx公司提供的PCI总线接口仿真实例的基础上实现的。按照PCI总线规范设计了一个简单的总线仲裁器,用来仿真主设备申请总线占用的过程。此外还设计了一个PCI总线上的从设备,用来仿真主设备与从设备之间的数据传输过程。此外还仿真了总线上对设备的自动配置过程。通过观察仿真波形图,发现设计完全满足PCI总线的数据传输规范,而且数据传输的结果正确。

在仿真验证正确的基础上,将设计实现于Xilinx公司型号为virtexII2v1000-fg456-5的FPGA中。将数据接口卡安装于测试计算机上,利用数据接口卡的自回路数据传输功能以及单向输入输出功能,对系统进行了验证和性能测试,结果如表格1中所示。

从结果可以看出,当输入输出速率保持在160Mbps以下时,可以保证自身回路数据传输无错进行,但是当速率提高到200Mbps以后,传输就会出现数据丢失,导致接收的数据与发送数据不一致。因此,为了保证数据的无错传输,自身回路数据传输测试速率应该不高于160Mbps。

单向输入输出测试时,当输入速率或者输出速率小于300Mbps,系统的功能是完全正确的,而当工作于400Mbps的时候,则会出现数据丢失的情况。与自身回路传输测试的数据比较可以看出,当在自身回路数据传输测试速率为200Mbps的时候,由于此时系统接收和输出同时进行,共同分时使用总线,此时相当于单独接收或者单独输出测试时400Mbps的传输速率。两次测试结果的一致性也说明了测试的可靠性。

5 结语

通过对系统的测试验证,证明了本设计能够完全满足高速实时数据流对数据采集存储系统的要求。为了方便以后进一步的工作,在测试时也对缓冲区大小和传输速率之间的关系进行了简单的测试。将缓冲区大小从8KB改变到16KB以后,传输速率只是稍微有些提高,对性能的改善十分不明显。结果说明简单的扩大硬件缓冲区并不会带来数据传输速率的明显改观,同时还会占用FPGA内部宝贵的RAM资源。究其原因在于,数据传输速率主要受到32位/33MHzPCI总线带宽自身的限制,以及硬盘读写的峰值速率的限制,而并不是缓冲区大小的影响。可以预见如果采用64位/66MHz的PCI总线并采用更多的磁盘来构成RAID磁盘阵列以提高磁盘读写速率,那么整体的性能会有很大的提升。