- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

使用NI LabVIEW 的自动高电压电击测试

Author(s):

David Hakey - Medtronic, Inc.

Patrick J. Ryan - Medtronic, Inc.

Johnny Maynes - Medtronic, Inc.

Industry:

Electronics, Biotechnology

Products:

NI-VISA, LabVIEW, FPGA Module, PXI-7811R

The Challenge:

构成自动化的高电压 (HV) 电击器测试系统,以个别测试 12 组 HV 电击器模块,并可测试不同的产品类型,缩短整体测试时间。

The Solution:

使用 NI LabVIEW FPGA 软件与 NI 智能数据采集 (DAQ) 硬件,建立非同步化的环境;所有的 12 个模块均具有独立通讯埠,并可自动执行作业。

Medtronic 公司的测试工程团队必须研发自动化的 HV 电击器测试解决方桉,且共 12 个测试模块能够个别测试 1 ~ 4 种不同的产品,以缩短整体测试时间。透过 LabVIEW FPGA 与 NI 智能DAQ硬件,团队将模块通讯速度从 20 KHz (平行通讯埠) 大幅提升至 1.7 MHz (FPGA),而缩短整体测试时间。

前款手动系统即透过平行通讯埠同步执行 12 个模块,仅可测试 1 种 HV 电击器,且测试 12 组仪器需耗时 135 分钟。新的自动化系统可透过 FPGA 数位 I/O 通讯功能,非同步执行 12 个模块,并于 48 分钟内测试最多 4 种不同类型的共 12 项装置。重入码测试序列器 (Reentrant test sequencer) 与测试程式可独立控制各测试模块,因此可由自动化装置操作 (Handling) 系统引导进行各组测试作业。执行测试的主机电脑整合自动化装置操作系统,与 HV 电击器测试系统。

测试自动化

AeroSpec 测试自动化操作系统将负责从 4 组输入盘 (Input tray) 中取出待测装置 (DUT);透过光学自行辨识 (OCR) 功能读取 DUT 序号;将 DUT 载入或卸载 12 组测试模块之一;最后根据测试结果,将 DUT 置于 12 组输出盘之一。4 项不同的产品可设定于 4 组输入盘中,每输入盘可容纳 20 组装置。

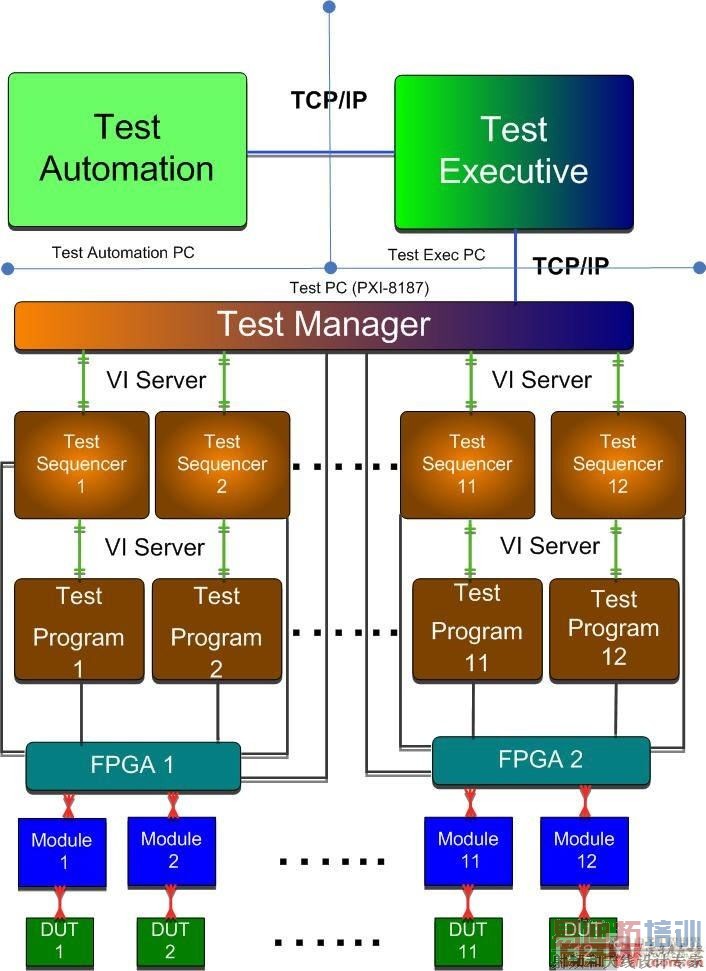

Test executive 系统为主控制器,可提供使用者界面、主导测试模块的负载与卸载程度,并让 Test manager 针对实际装置或装载于测试模块的装置,进行 HV 电击器测试。 [p]

Test manager 将决定受测产品,并将该笔资讯送至 Test executive,让操作者选择要进行测试的产品。操作者根据各系统设定以载入产品并开始测试,测试处理器接着将 DUT 载入至测试模块中。一旦载入 DUT,即开始于特定模块中进行测试。Test executive 与测试处理器将于测试期间持续载入剩下的 DUT,Test manager 将跟着测试每组 DUT 直至完毕。Test manager 可动态调用最多 12 组重入码测试序列器 (Test Sequencer),并接着动态调用重入码独立测试程序。Test manager 将依据测试执行档启动测试程序 (Test executive)。

系统将管理于 LabVIEW 图形化程式设计环境中管理所有测试模块与 DUT。各测试模块均具有静态属性集,其中数值将根据产品类型、测试阶段、硬体设定,与其他处理属性而有所变化。当目前 DUT 的测试作业结束,测试系统将关闭记忆体内的测试伫列。Test manager 将监控测试状态,并于 DUT 完成测试时通知 Test executive 测试通过/失败状态。Test executive 将接着让测试器卸载 DUT,并将之放置于输出盘 (Output tray) 中。.接着另 1 组 DUT 将载入至测试模块,以进行下个测试循环。各 12 个测试模块均独立进行 DUT 载入、测试,与卸载循环。自动化测试器则会将载入/卸载作业要求排入伫列。

共 2 组 NI PXI-7811R 模块 则透过序列通讯 (SPI) 与 JTAG,分别沟通测试模块与 DUT。此 2 个 NI PXI-7811R 模块均执行相同的 LabVIEW FPGA 程序,但具有不同的同步机制 (Semaphore) 与 NI-VISA 来源可控制该模块。

Test sequencer 将从测试程式中动态呼叫测试案例 (Test case),以控制 DUT 测试作业。由于记忆体必须容纳测试程式与最多 12 组重入码或 Test sequencer 的独立备份,因此必须牺牲些许系统效能,以囊括所有 subVI 或 subfunction 重入码。仅这些 subVI 即可形成系统瓶颈,或包含可产生重入码的总体 (Global) 功能。此解决方桉则可降低整体系统记忆体的使用率,以提升相关效能。所有 Test sequencer 与测试程式均使用相同 FPGA,因此系统使用同步机制 (Semaphore) 或称为载具 (Token),以控制各 PXI-7811R 模块。

所有 VI 均必须存取 FPGA 程序,以初始化该同步机制。各 FPGA 系统均具有独立同步机制,可让群组 A (1 ~ 6) 中的 1 个模块存取第一个 FPGA 系统;而群组 B (7 ~ 12) 的 1 个模块则几乎同步存取第二个 FPGA 系统。每组 FPGA 的互动作业极为短暂 – 约几个毫秒 (Millisecond);因此该方式适于分配 FPGA 来源程序,以支援 12 组对等程式。各模块的各个测试程序约有 600 个 FPGA 互动作业。FPGAs 可非同步高速执行 12 个模块,以处理系统可负荷的所有流量。