- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于LabVIEW的三极管老化测试系统设计

录入:edatop.com 点击:

针对一些功率器件(功率三极管、VDMOS,IGBT等),通过有规律给元器件通电和断电,循环施加电应力和热应力,可以检验其承受循环应力的能力。基于上述原理,借助可视化编程语言LabVIEW和NI系列sb RIO-9612板卡,本文设计了一种三极管老化测试系统,该系统满足国军标GJB1036的试验要求,每个工位的采样时间不大于4μs,总共64工位的采样周期不大于300μs,满足了快速控制的要求,同时还不失精准,电压和电流的采样分辨率达到了12 bit,精度达到1%,从而控制了器件结温误差。目前系统已经交付运行,实验结果达到了用户的需求,具有很高的实用价值。

随着航空,航天,能源工业等领域对电子产品质量的要求日益提高,电子产品的可靠性问题受到越来越广泛的重视。电子产品在使用过程中会遇到不同环境条件,在热胀冷缩的应力作用下,热匹配性能力差的电子元器件就容易失效,导致电子产品故障,造成巨大的人力和财力损失。电子元器件的老化测试就是仿照或者等效产品的使用状态,通过测试,将不符合器件剔除,将电子产品的质量在加工初期进行有效地控制,以保证电子产品使用的可靠性和稳定性。

针对电子元器件的这种情况,我们开发了一种老化测试系统,可以主要针对功率器件(功率三极管、VDMOS,IGBT等),通过有规律给元器件通电和断电,循环施加电应力和热应力,检验其承受循环应力的能力。

1 工作原理

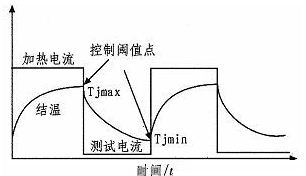

通过给晶体管通电加热,使晶体管在当前恒定功率下工作,通过一段时间后,晶体管因为发热而使得器件的结温持续升高,到达设定值后,断开恒流源和恒压源,给器件通风,使其温度降低到设定值,反复这个过程,就可以较为准确的算出该器件的加热时间和冷却时间,达到了间歇测试的目的。基本的工作原理图如1所示。

图1 间歇寿命测试循环示意图

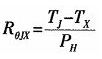

半导体器件的热阻通常定义为:

其中RθJX=器件结点到具体环境的热阻(替代符号是θJX)[℃/W];

TJ=稳定状态测试条件下的器件结温[℃];

TX=环境的参考温度[℃];

PH=设备功耗[W];

测试条件下器件结温可表示为:

Tj=TJ0+△TJ

其中TJ0=器件加热前的初始结温[℃];

△TJ=器件结温变化量

通过温度敏感参数(TSP)来表示结温变化量,公式为:

△TJ=K×△TSP

其中△TSP=温度敏感参数的变化量[mV];

K=定义TJ和TSP变化关系的常量[℃/mV];

温度敏感参数可表示为:

TSP=Ie×-4Vce

其中Ie=冷却测量时刻加的恒流源值[mV];

Vce=器件的结电压值[mV];

K系数为结温随结电压的变化关系,固定器K件系数为常量,不同器件K的系数不同,可在试验器件的资料中查出,或者厂家给出。其计算公式可表示为:

其中TJ1和TJ2为两个时刻的结温,Vce1和Vce2为结温对应的结电压。

2 系统架构

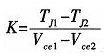

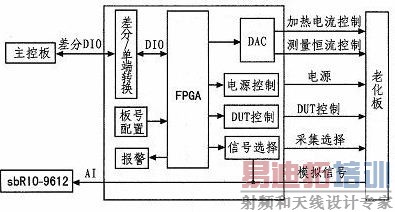

系统采用PC机+sbRIO-9612+主控板+驱动板+老化板的结构,如图2所示,PC和9612之间通过网口通信,9612与主控板之间通过数字I/O口通信,sbRIO-9612,主控板,驱动板供电都是由开关稳压电源完成,程控电源为老化板上的器件提供工作电源,16路差分AD用于采集老化板上待测器件的电流,电压以及电源温度等信号。系统使用sbRIO-9612加扩展板构成下位机,作为系统的主控板;主控板与驱动板采用总线通讯,驱动板主要功能是将主控板进来的20对差分信号转换后(硬件实现)给驱动板FPGA,用20路信号与sbRIO-9612实现通信,sbRIO-9612通过控制FPGA中的寄存器来实现电源、恒流源、漏/源的通断,从而建立功率循环及合适的采样条件,硬件示意图如3所示。

图2 系统总体构架图

图3 FPGA硬件示意图

驱动板和老化板分别采用两个对接座连接,电流电压采样信号回传到sbRIO-9612板上进行AD变换后发送到上位机。

下一页:老化测试系统工作流程及精度和切换速度的实现

3 工作流程及实现

3.1 LabVIEW简介

LabVIEW是一个程序开发环境。它使用图形化编程语言G在流程图中创建源程序,LabVIEW FPGA模块将LabVIEW图形化开发平台扩展到基于NI可重配置I/O(RIO)架构的硬件平台上的现场可编程门阵列(FPGA)。

3.2 工作流程

工作开始,上位机按照TCP/IP协议将控制命令发送给sbRIO-9612,接收到指令后,根据上位机操作,sbRIO-9612将相应指令和相关参数下发到主控板,主控板控制驱动板执行指令,进而控制老化板执行相关操作。

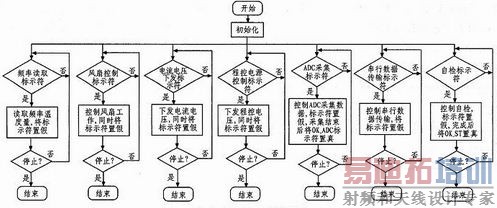

sbRIO-9612主要由两大部分组成,即FPGA部分和RT部分;在工作的划分上,由于系统对速度的要求,其中风扇控制,程控电源控制,温度频率量读取,ADC采集,DAC发数,差分数据传输等模块分配到速度很快的FPGA部分执行,而速度稍慢的RT部分主要实现的是上位机指令的解析,老化工作控制和下位机向上位机的数据传输工作的进行。LabVIEW FPGA工作流程图如图4所示。

图4 FPGA工作流程图

3.3 工作过程的实现

3.3. 1 综述

工作开始前,先连接下位机,连接成功后,调用自检模块,对将要做老练测试的老化板进行自检,自检成功后,上位机将参数下发到下位机,然后下发开始控制命令,下位机轮询每块板子的控制命令字,板子开始工作后,将工作需要的加热电流和测量电流以及程控电压等通过串行数据传输模块下发到驱动板,通过驱动板加载到相应的老化板上,给器件加热,记录此时的时间,即为加热开始时刻,当前时刻与加热开始时刻之差大于等于开时间的时候,停止加热,打开风扇,记录加热结束时刻,开始AD采集,根据采集的电流和电压计算出结温,将数值传回上位机,上位机根据温度变化绘出一条曲线。当前时刻与加热结束时刻之差大于等于关时间时,冷却完成并结束测量,进入下一次循环,循环次数到达后,将此板子置于空闲状态。

3.3.2 精度和切换速度的实现

1)高速ADC采集

SbRIO-9612上集成有AD采集芯片,16位的AD可以保证其采样分辨率达到1‰,同时,4μs的转换时间,保证了AD的采样速度;为了消除共模噪声的影响,将32路AD转换为16路的差分输入,采集时每次每个通道连续取8个数值求均值为本次采集的结果,同时配合老化板中采用的高速开关进行切换,保证了采集数据的精度要求。下图是在设定的10 mA的测量电流和12 V的程控电压,通过LabVIEW显示出当前NMOS管(型号为IRFP460)的结电压和当前时刻测量得到的管子结温,室温通过安装在每块老化板上的温度传感器得出为17.3 20 6摄氏度,从图5中看出,AD采集回来的16通道的值都在小数点三位后开始波动,保证了计算得到的△Vf的值在小数点后二位开始波动。

图5 RT工作流程图

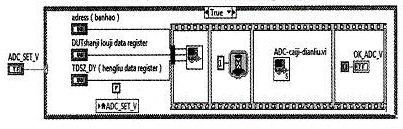

系统在加热状态切入到测量状态后20μs内可完成所有工位结电压的采集,为达到快速采集要求,编写程序时候,考虑到ADC高实时性问题,将采集部分分配到sbRIO-9612的FPGA上完成,sbRIO-9612的Onboard Clock为40 MHz,即0.025μs的周期,写FPGA程序时,将ADC采集配置(即开关的切换命令执行)和采集数据放到顺序结构的相邻的两帧之间,考虑到开关切换时间,中间加1μs的等待,保证数据的可靠性,然后开始数据采集,ADC采集部分程序如图6所示。

图6 AD采集结果在LabVIEW中显示

图7 FPGA上ADC结电压采集程序

2)差分数据传输

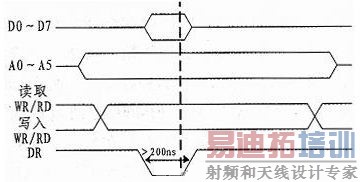

此模块实现sbRIO-9612与FPGA之间的通信,通信方式为总线异步访问的方式,通过串行DAC方式收发数据,所谓串行DAC,即在一定的时钟下(时钟周期为80 MHz),按照固定的时序进行串行发数,先将地址分配到端口,地址总共为六位,即A0-A5,高四位为地址位(控制板号),低两位为驱动板寄存器地址;然后将数据放到数据总线上,数据格式为U8,置高WR/RD,然后:DR位置低,保持两个时钟周期,DR置高,完成串行DAC写数据;同理,读数据时先设置地址总线,WR/RD置低,DR置低,保持两个时钟周期,在两个周期内完成数据的读取,DR置高,完成串行DAC读数据。整个通信模块按照通信协议,实现了SbRIO-9612对FPGA的控制。

图8 SbRIO读取和写入时序

4 实验结果

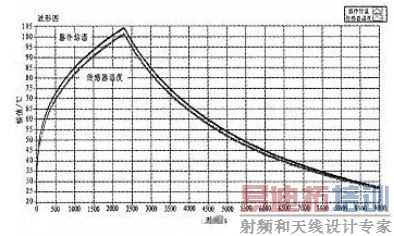

在环境温度为25℃,温升为80℃,加热恒流源设置为50 mA,恒压源设置为5 V,开时间设置为2 300 s,关时间设置为7700 s,定时模式下,每隔50 ms采样得到结温图,如图9,结束时刻温度由于周围温度升高,基本很难达到初始的25℃,但是在温度降低到了误差允许范围内。图中,红线由NMOS管背部贴的传感器测量得出的温度变化数据绘出,黑线由采集回来的数据通过结温计算公式计算出的数据描绘出来的,对比下,传感器测出数据的变化趋势和计算结果数据变化保持一致,这就说明了测量结果准确。

图9 温度曲线

5 结束语

文中介绍了一个在SbRIO-9612上,用LabVIEW实现控制一个老化测试系统工作,该系统达到了预订采集数据精度和分辨率,满足了快速采集和快速控制等要求,在实际应用中,达到了很好的效果,具有很高的实用价值。