- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

JTAG基本原理及仿真器性能比较

录入:edatop.com 点击:

JTAG(Joint Test Action Group,联合测试行动组)是一种国际标准测试协议(IEEE 1149.1兼容)。标准的JTAG接口是4线——TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

JTAG的主要功能有两种,或者说JTAG主要有两大 类:一类用于测试芯片的电气特性,检测芯片是否有问题;另一类用于Debug,对各类芯片以及其外围设备进行调试。一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器、挂在CPU总线上的设备以及内置模块的寄存器。本文主要介绍的是Debug功能。

1 JTAG原理分析

简单地说,JTAG的工作原理可以归结为:在器件内部定义一个TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试和调试。首先介绍一下边界扫描和TAP的基本概念和内容。

1.1 边界扫描

边界扫描(Boundary-Scan)技术的基本思想是在靠近芯片的输入/输出引脚上增加一个移位寄存器单元,也就是边界扫描寄存器(Boundary-Scan Register)。

当芯片处于调试状态时,边界扫描寄存器可以将芯片和外围的输入/输出隔离开来。通过边界扫描寄存器单元,可以实现对芯片输入/输出信号的观察和控制。对于芯片的输入引脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该引脚中去;对于芯片的输出引脚,也可以通过与之相连的边界扫描寄存器“捕获”该引脚上的输出信号。在正常的运行状态下,边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一种便捷的方式用于观测和控制所需调试的芯片。另外,芯片输入/输出引脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。边界扫描链可以串行地输入和输出,通过相应的时钟信号和控制信号,就可以方便地观察和控制处在调试状态下的芯片。

1.2 测试访问口TAP

TAP(Test Access Port)是一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。对整个TAP的控制是通过TAP控制器(TAP Controller)来完成的。下面先分别介绍一下TAP的几个接口信号及其作用。其中,前4个信号在IEEE1149.1标准里是强制要求的。

简单地说,PC机对目标板的调试就是通过TAP接口完成对相关数据寄存器(DR)和指令寄存器(IR)的访问。

系统上电后,TAP Controller首先进入Test-LogicReset状态,然后依次进入Run-Test/Idle、Selcct-DR-Scan、Select-IR-Scan、Capture-IR、Shift-IR、Exitl-IR、Update-IR状态,最后回到Run-Tcst/Idle状态。在此过程中,状态的转移都是通过TCK信号进行驱动(上升沿),通过TMS信号对TAP的状态进行选择转换的。其中,在Capture-IR状态下,一个特定的逻辑序列被加载到指令寄存器中;在Shift-IR状态下,可以将一条特定的指令送到指令寄存器中;在Update—IR状态下,刚才输入到指令寄存器中的指令将用来更新指令寄存器。最后,系统又回到Run—Test/Idle状态,指令生效,完成对指令寄存器的访问。当系统又返回到Run—Test/Idle状态后,根据前面指令寄存器的内容选定所需要的数据寄存器,开始执行对数据寄存器的工作。其基本原理与指令其存器的访问完全相同,依次为seIect—DR—Scan、Capture—DR、Shift—D、Exitl一DR、Update—DR,最后回到Run-Tcst/Idle状态。通过TDl和TDO,就可以将新的数据加载到数据寄存器中。经过一个周期后,就可以捕获数据寄存器中的数据,完成对与数据寄存器的每个寄存器单元相连的芯片引脚的数据更新,也完成了对数据寄存器的访问。

目前,市场上的JTAG接口有14引脚和20引脚两种。其中,以20引脚为主流标准,但也有少数的目标板采用14引脚。经过简单的信号转换后,可以将它们通用。

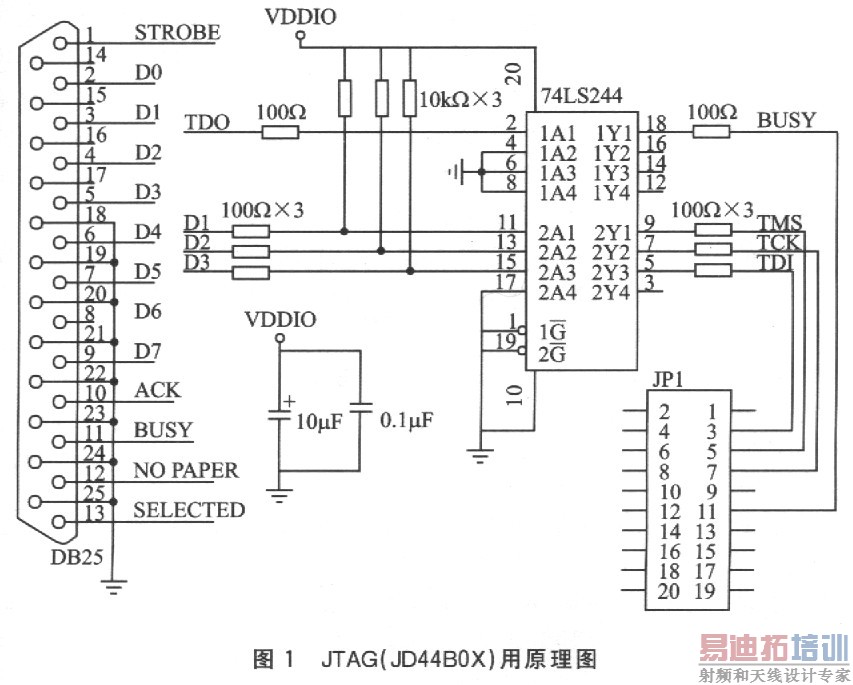

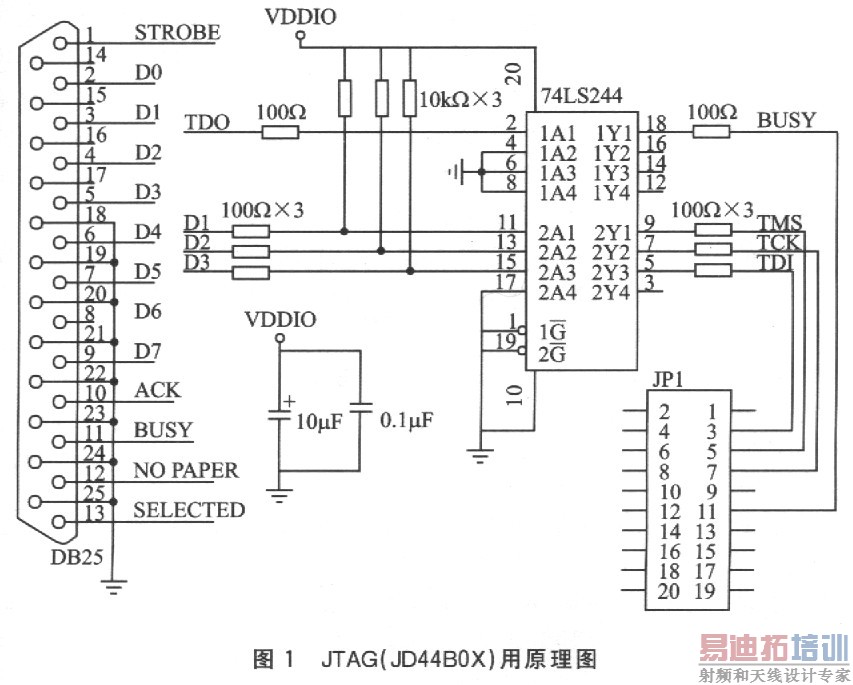

下面通过对JD44BOX实验开发板的简易JTAG的基本原理进行分析,以及对JD44BOX和STR710试验开发板主板的JTAG原理进行对比,进一步阐述JTAG的工作原理。JD44BOX实验开发板的简易JTAG的原理图如图1所示。

图1中,74LS244为三态输出的8组缓冲器和总线驱动器,其功能如表l所列。

由表1可知,在JD4480X实验板的调试过程中,这款简易JTAG的主要作用就是将PC机发出的电信号与实验板的电信号进行匹配,以实现驱动目标板的功能。

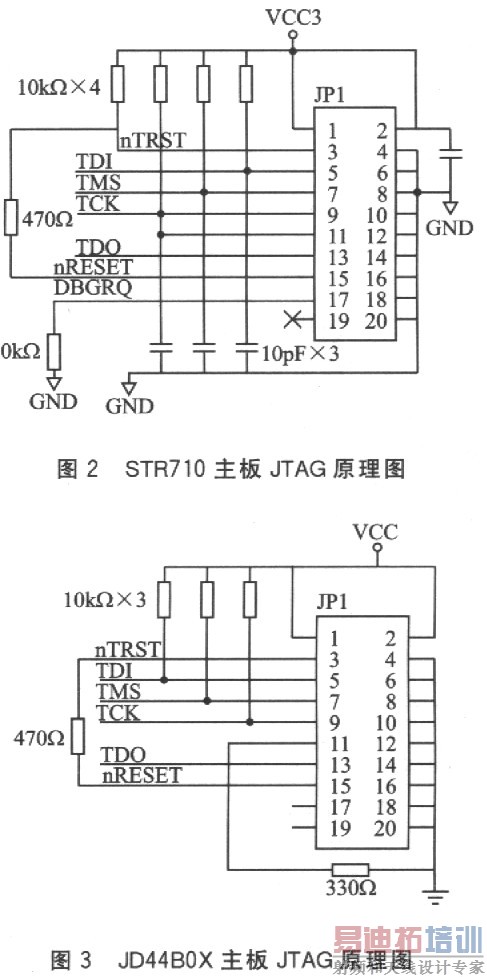

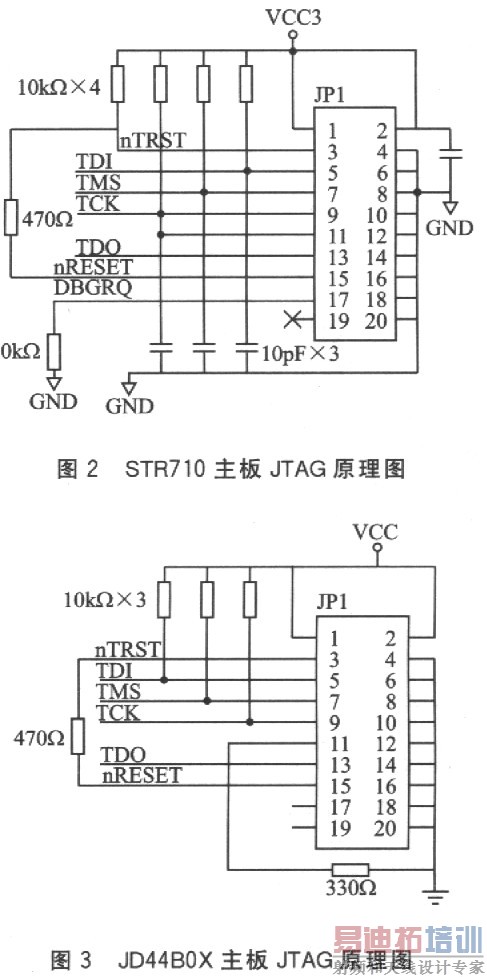

STR710和JD44BOX主板的JTAG原理图如图2和图3所示。

通过图2和图3的对比可以发现,虽然所用的仿真器有很大的差别,但是,实际上忽略一些上下拉电阻以及保护电容(这些电阻、电容对于电路功能没有意义),它们的基本原理图是十分相似的,唯一的差别就在于对RTCK信号(用于测试时钟返回)和DBGRQ信号(用于设置目标板工作状态)的处理。实际上,在IEEE1149.1标准中这两个信号都不是强制要求的。因此,在分析仿真器(JTAG)的工作原理时完全可以忽略这两个信号的情况,而仅对IFEE 1149.1标准中强制要求的4个信号进行分析。

2 仿真器与简易JTAG的性能对比

2.1 仿真器硬件连接

硬件连接如图4所示。通过主机的并口与仿真器相连接,再将仿真器与目标板的JTAG调试接口连接。

2.2 性能对比

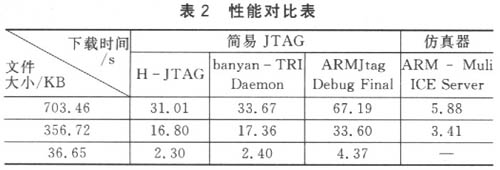

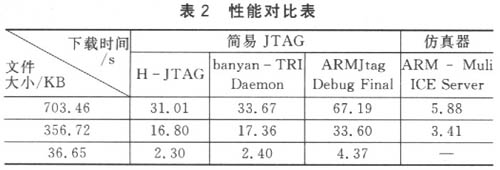

如表2所列,虽然通过不同的调试代理所需的下载时间有所不同,但是两种仿真器所存在的性能差异仍然很明显。在选用简易JTAG下载文件的过程中,效率最高的调试代理所需的时间仍将近是仿真器的6倍,这就是仿真器的优势所在。性能的提高必然要付出更多的代价,对开发者来说这个代价就是成本。经过市场的考察,仿真器的价格一般在千兀左右,而简易JTAG的价格一般在百元左右,也就是存在将近10倍的差别。另外,还需要考虑的就是其兼容性。兼容性包括与H标板的兼容和与调试代理的兼容。在与目标板的兼容方面,后面的内容中会有详细说明;在与调试代理的兼容方面也有所反映。简易JTAG能够与多个调试代理兼容,而仿真器只能使用其自带的调试代理,具有一定的局限性。

2.3 原因分析

既然所有JTAG的基本原理都是一样的,为什么这两种仿真器的速度会存在如此大的差异,而且并不是所有的仿真器都是通用的呢

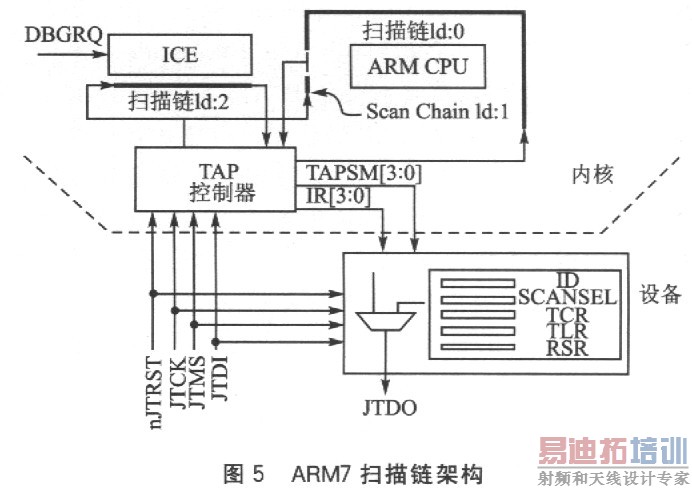

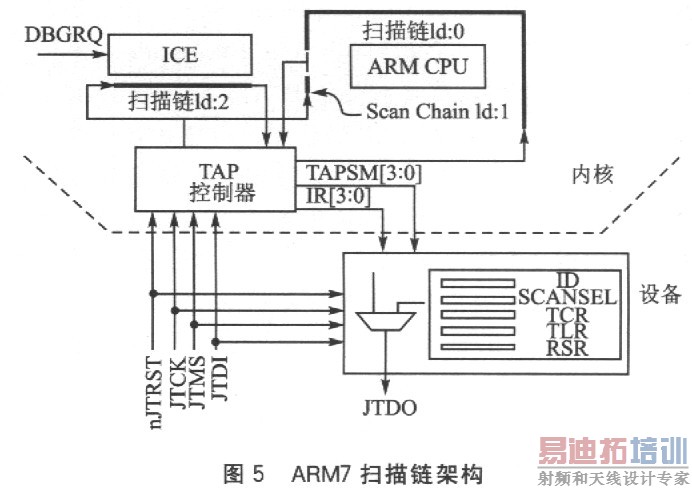

首先介绍一下ARM7扫描链架构,如图5所示。

与简易JTAG比较,在扫描过程中,STR710的仿真器为ARM7TDMI添加了一个专门的指针通道以及相应的存储空间store-multiple(STM)。因此在调试状态下,仿真器不再利用系统除了边界扣描寄存器外的任何其他资源,而是通过JTAG-style接口直接获取系统的状态信息,对系统状态进行观测以及调试,进而大大提高调试速度。

在STR7lO目标板中,ARM7TDMI可以通过外部信号和内部电路模块(ICE)进入调试状态。当目标板一旦进入调试状态后,内核就将其与存储器分离开来,这样内核就可以保证在不影响系统正常运作的状态下对系统的状况进行监测和调试。同时,ARM7TDMI内部状态的检测是通过JTAG-style接口进行的,这个接口允许指令不通过数据线直接进入到内核的扫描通道。这样在调试状态下,STM就可以直接嵌入到指令通道并存储ARM7TDMI寄存器的内容,在不影响系统工作的情况下将这些内容移位出来,使仿真器获得目标板的状态信息。

与仿真器比较,简易JTAG完成的工作就要少得多。它只是完成了对主机信号的电平转换,也就是相当于一个驱动器。上面提到的所有工作都要交给CPU去做,因此在使用简易JTAG下载文件时目标板自然会相应地降低速度。尤其是当程序相对较大时,其速度就会大大降低,对于一些开发人员来讲,这是相当致命的缺点。

关于仿真器与目标板的兼容问题,现在市场上的部分仿真器出现不同程度的不兼容问题,其产生的主要原因是对RTCK信号(DBGRQ信号极不常见,这里不作介绍)的处理情况存在一些差异(不包括周立功系列的实验开发板,它们的仿真器使用的足单片机,与大多数的仿真器都不能兼容)。例如,在STR710中是将STCK信号与TCK信号直接相连了,而在nano2410A实验开发板中是将STCK信号直接接地,因此造成了ARM JTAG Emulator在nano2410A实验开发板中的不兼容。在对nano2410A主板的JTAG进行了小小的改动后就完成了仿真器兼容性的扩展。

备注:①JD4480X为北京交通大学自控室实验开发板,STR710为北京微芯力科技有限公司实验开发板;②实验数据为秒表所测。

JTAG的主要功能有两种,或者说JTAG主要有两大 类:一类用于测试芯片的电气特性,检测芯片是否有问题;另一类用于Debug,对各类芯片以及其外围设备进行调试。一个含有JTAG Debug接口模块的CPU,只要时钟正常,就可以通过JTAG接口访问CPU的内部寄存器、挂在CPU总线上的设备以及内置模块的寄存器。本文主要介绍的是Debug功能。

1 JTAG原理分析

简单地说,JTAG的工作原理可以归结为:在器件内部定义一个TAP(Test Access Port,测试访问口),通过专用的JTAG测试工具对内部节点进行测试和调试。首先介绍一下边界扫描和TAP的基本概念和内容。

1.1 边界扫描

边界扫描(Boundary-Scan)技术的基本思想是在靠近芯片的输入/输出引脚上增加一个移位寄存器单元,也就是边界扫描寄存器(Boundary-Scan Register)。

当芯片处于调试状态时,边界扫描寄存器可以将芯片和外围的输入/输出隔离开来。通过边界扫描寄存器单元,可以实现对芯片输入/输出信号的观察和控制。对于芯片的输入引脚,可以通过与之相连的边界扫描寄存器单元把信号(数据)加载到该引脚中去;对于芯片的输出引脚,也可以通过与之相连的边界扫描寄存器“捕获”该引脚上的输出信号。在正常的运行状态下,边界扫描寄存器对芯片来说是透明的,所以正常的运行不会受到任何影响。这样,边界扫描寄存器提供了一种便捷的方式用于观测和控制所需调试的芯片。另外,芯片输入/输出引脚上的边界扫描(移位)寄存器单元可以相互连接起来,在芯片的周围形成一个边界扫描链(Boundary-Scan Chain)。边界扫描链可以串行地输入和输出,通过相应的时钟信号和控制信号,就可以方便地观察和控制处在调试状态下的芯片。

1.2 测试访问口TAP

TAP(Test Access Port)是一个通用的端口,通过TAP可以访问芯片提供的所有数据寄存器(DR)和指令寄存器(IR)。对整个TAP的控制是通过TAP控制器(TAP Controller)来完成的。下面先分别介绍一下TAP的几个接口信号及其作用。其中,前4个信号在IEEE1149.1标准里是强制要求的。

- TCK:时钟信号,为TAP的操作提供了一个独立的、基本的时钟信号。

- TMS:模式选择信号,用于控制TAP状态机的转换。

- TDI:数据输入信号。

- TDO:数据输出信号。

- TRST:复位信号,可以用来对TAP Controller进行复位(初始化)。这个信号接口在IEEE 1149.1标准里并不是强制要求的,因为通过TMS也可以对TAP Controller进行复位。

- STCK:时钟返回信号,在IEEE 1149.1标准里非强制要求。

- DBGRQ:目标板卜工作状态的控制信号。在IEEE 1149.1标准里没有要求,只是在个别目标板(例如STR710)中会有。

简单地说,PC机对目标板的调试就是通过TAP接口完成对相关数据寄存器(DR)和指令寄存器(IR)的访问。

系统上电后,TAP Controller首先进入Test-LogicReset状态,然后依次进入Run-Test/Idle、Selcct-DR-Scan、Select-IR-Scan、Capture-IR、Shift-IR、Exitl-IR、Update-IR状态,最后回到Run-Tcst/Idle状态。在此过程中,状态的转移都是通过TCK信号进行驱动(上升沿),通过TMS信号对TAP的状态进行选择转换的。其中,在Capture-IR状态下,一个特定的逻辑序列被加载到指令寄存器中;在Shift-IR状态下,可以将一条特定的指令送到指令寄存器中;在Update—IR状态下,刚才输入到指令寄存器中的指令将用来更新指令寄存器。最后,系统又回到Run—Test/Idle状态,指令生效,完成对指令寄存器的访问。当系统又返回到Run—Test/Idle状态后,根据前面指令寄存器的内容选定所需要的数据寄存器,开始执行对数据寄存器的工作。其基本原理与指令其存器的访问完全相同,依次为seIect—DR—Scan、Capture—DR、Shift—D、Exitl一DR、Update—DR,最后回到Run-Tcst/Idle状态。通过TDl和TDO,就可以将新的数据加载到数据寄存器中。经过一个周期后,就可以捕获数据寄存器中的数据,完成对与数据寄存器的每个寄存器单元相连的芯片引脚的数据更新,也完成了对数据寄存器的访问。

目前,市场上的JTAG接口有14引脚和20引脚两种。其中,以20引脚为主流标准,但也有少数的目标板采用14引脚。经过简单的信号转换后,可以将它们通用。

下面通过对JD44BOX实验开发板的简易JTAG的基本原理进行分析,以及对JD44BOX和STR710试验开发板主板的JTAG原理进行对比,进一步阐述JTAG的工作原理。JD44BOX实验开发板的简易JTAG的原理图如图1所示。

图1中,74LS244为三态输出的8组缓冲器和总线驱动器,其功能如表l所列。

由表1可知,在JD4480X实验板的调试过程中,这款简易JTAG的主要作用就是将PC机发出的电信号与实验板的电信号进行匹配,以实现驱动目标板的功能。

STR710和JD44BOX主板的JTAG原理图如图2和图3所示。

通过图2和图3的对比可以发现,虽然所用的仿真器有很大的差别,但是,实际上忽略一些上下拉电阻以及保护电容(这些电阻、电容对于电路功能没有意义),它们的基本原理图是十分相似的,唯一的差别就在于对RTCK信号(用于测试时钟返回)和DBGRQ信号(用于设置目标板工作状态)的处理。实际上,在IEEE1149.1标准中这两个信号都不是强制要求的。因此,在分析仿真器(JTAG)的工作原理时完全可以忽略这两个信号的情况,而仅对IFEE 1149.1标准中强制要求的4个信号进行分析。

2 仿真器与简易JTAG的性能对比

2.1 仿真器硬件连接

- PC机配置:1.66 GHz,256 MB内存。

- 调试软件:ADS1.2。

- 目标板:JD44BOX。

- 完成任务:文件的下载。

硬件连接如图4所示。通过主机的并口与仿真器相连接,再将仿真器与目标板的JTAG调试接口连接。

2.2 性能对比

如表2所列,虽然通过不同的调试代理所需的下载时间有所不同,但是两种仿真器所存在的性能差异仍然很明显。在选用简易JTAG下载文件的过程中,效率最高的调试代理所需的时间仍将近是仿真器的6倍,这就是仿真器的优势所在。性能的提高必然要付出更多的代价,对开发者来说这个代价就是成本。经过市场的考察,仿真器的价格一般在千兀左右,而简易JTAG的价格一般在百元左右,也就是存在将近10倍的差别。另外,还需要考虑的就是其兼容性。兼容性包括与H标板的兼容和与调试代理的兼容。在与目标板的兼容方面,后面的内容中会有详细说明;在与调试代理的兼容方面也有所反映。简易JTAG能够与多个调试代理兼容,而仿真器只能使用其自带的调试代理,具有一定的局限性。

2.3 原因分析

既然所有JTAG的基本原理都是一样的,为什么这两种仿真器的速度会存在如此大的差异,而且并不是所有的仿真器都是通用的呢

首先介绍一下ARM7扫描链架构,如图5所示。

与简易JTAG比较,在扫描过程中,STR710的仿真器为ARM7TDMI添加了一个专门的指针通道以及相应的存储空间store-multiple(STM)。因此在调试状态下,仿真器不再利用系统除了边界扣描寄存器外的任何其他资源,而是通过JTAG-style接口直接获取系统的状态信息,对系统状态进行观测以及调试,进而大大提高调试速度。

在STR7lO目标板中,ARM7TDMI可以通过外部信号和内部电路模块(ICE)进入调试状态。当目标板一旦进入调试状态后,内核就将其与存储器分离开来,这样内核就可以保证在不影响系统正常运作的状态下对系统的状况进行监测和调试。同时,ARM7TDMI内部状态的检测是通过JTAG-style接口进行的,这个接口允许指令不通过数据线直接进入到内核的扫描通道。这样在调试状态下,STM就可以直接嵌入到指令通道并存储ARM7TDMI寄存器的内容,在不影响系统工作的情况下将这些内容移位出来,使仿真器获得目标板的状态信息。

与仿真器比较,简易JTAG完成的工作就要少得多。它只是完成了对主机信号的电平转换,也就是相当于一个驱动器。上面提到的所有工作都要交给CPU去做,因此在使用简易JTAG下载文件时目标板自然会相应地降低速度。尤其是当程序相对较大时,其速度就会大大降低,对于一些开发人员来讲,这是相当致命的缺点。

关于仿真器与目标板的兼容问题,现在市场上的部分仿真器出现不同程度的不兼容问题,其产生的主要原因是对RTCK信号(DBGRQ信号极不常见,这里不作介绍)的处理情况存在一些差异(不包括周立功系列的实验开发板,它们的仿真器使用的足单片机,与大多数的仿真器都不能兼容)。例如,在STR710中是将STCK信号与TCK信号直接相连了,而在nano2410A实验开发板中是将STCK信号直接接地,因此造成了ARM JTAG Emulator在nano2410A实验开发板中的不兼容。在对nano2410A主板的JTAG进行了小小的改动后就完成了仿真器兼容性的扩展。

备注:①JD4480X为北京交通大学自控室实验开发板,STR710为北京微芯力科技有限公司实验开发板;②实验数据为秒表所测。

上一篇:导电材料电阻率的三种经典测量方法

下一篇:测试功率阶段开关特点