- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ADC和FPGA脉冲信号测量的设计方案

录入:edatop.com 点击:

1 引言

测频和测脉宽现在有多种方法。通常基于MCU的信号参数测量,由于其MCU工作频率很低,所以能够达到的精度也比较低,而基于AD10200和 FPGA的时域测量精度往往可达10 ns,频率测量精度在100 kHz以内。适应信号的脉宽范围在100 ns~1 ms之间;重复周期在0.05~100ms:频率在0.1 Hz~50 MHz。

AD10200是高速采样芯片,其中内嵌变压器,因此采样电路外部不再需要变压器,使得电路设计更为简单;最低采样速率为105 MSPS,具有3.3 V或者5 V CMOS兼容输出电平,双通道12位采样,补码形式输出,每个通道功耗为0.850W。通常可应用于雷达中频信号接收机、相位组接收机、通信接收机、 GPS抗干扰接收机等。

StratixⅡ是Altera公司的中高端主流产品,该产品采用1.2 V、90 nm、9层信号走线,全铜SRAM工艺制造。StratixⅡ内嵌RAM块、DSP块、锁相环(PLL)和外部存储器接口,同时,StratixⅡ也增加了全新的逻辑结构一自适应逻辑模块(ALM),因而增加了动态相位对准(DPA)电路和对新的外部存储器接口的支持。AD芯片可以稳定工作在100 MHz,FPGA速度可高达几百MHz,故可保证系统的测量精度。

2 测量原理

2.1 时域测量原理

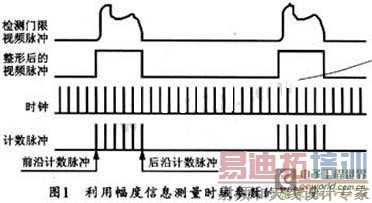

时域测量包括脉宽(PW)测量和脉冲重复周期(Pri)测量,时域测量在FPGA中可利用数字化技术实现。AD的两路输入为两路正交中频信号。经过Cordic算法,即幅相解算之后获得幅度和相位信息,其中利用幅度信息测得时域参数,其原理图如图1所示。

当脉冲信号进入FPGA后,将首先进行门限判定,以将不规则的脉冲信号进行整形并变为规则的脉冲信号。整形后,在脉冲信号上升沿启动脉宽计数器和重复周期计数器,而在该脉冲信号的下降沿锁存脉宽计数器并且在下个脉冲信号上升沿锁存重复周期计数器;由此即可得到脉宽和重复周期的量化值N和M,然后再通过工作时钟的计算,就可得出脉宽和重复周期。

2.2 频域参数测量

频域参数测量可由两路正交信号所携带的相位信息得到。对于输入正交采样I、Q两路序列,则可通过求反正切得到角度序列 θ(n)=arctg(I(n/Q(n),但此时得到的角度序列是周期性分布在(0,2π)之间的,因此需对此角度进行解模糊,可将角度序列解为递增直线,然后按照如下公式进行解模糊,并得到新的角度序列φ(n):

通过以上公式可以准确计算出脉内信号频率,从而达到测频的目的。

3 系统硬件电路设计

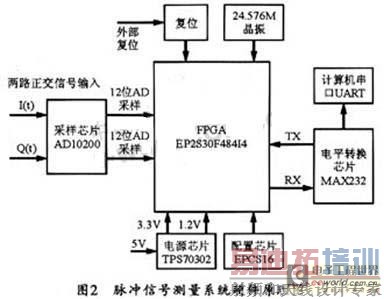

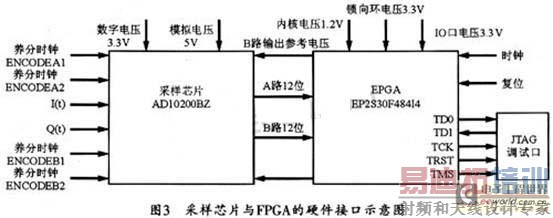

基于AD10200和FPGA芯片EP2S30F48414的脉冲信号测量系统的硬件电路原理如图2所示。此系统的输入信号要求为两路正交信号,正交信号在基带数字信号处理中经常要用到,它可以通过多种方法来实现,如模拟器件下变频或者是数字正交下变频等技术。IQ两路正交信号的特点为幅度相仿,相位相差90度。AD采样芯片负责将模拟信号转换为数字信号;电源芯片用于为AD、FPGA和MAX232供电;晶振用于提供工作时钟,选择24.576 MHz晶振的原因是因为FPGA与计算机串口通信时还要实现一个模拟串口,而选用24.576 MHz可以刚好模拟出9600 bit/s的波特率,从而可减少误码率:外部复位可为FPGA提供外部复位信号。MAX232是一个常用的电平转换芯片,可以将FPGA输出的LVTTL 3.3 V电平转换为串口电平,以便被计算机UART口所识别和接收。由以上芯片组成的系统工作频率为100 MHz,可实现快速、高精度地脉宽和频率测量。其中采样芯片和FPGA的硬件连接图如图3所示。

4 FPGA软件设计

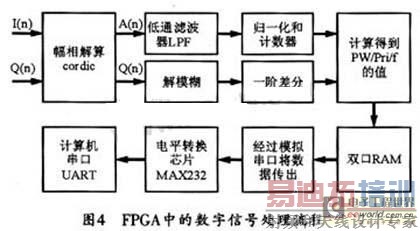

本系统中的时域参数测量和频域参数测量工作由FPGA担任,其输入为正交信号两路序列,输出分别为脉宽(PW)、重复周期(Pri)和频率(f)。FPGA中的数字信号处理流程如图4所示。

图中,I(n)和Q(n)为两路正交信号序列;A (n)为幅度信息序列;为相位信息序列。

两路正交信号I(n)和Q(n) 序列经过幅相解算后,即可得到幅度序列和相位序列。对于幅度序列,经过低通滤波和归一化,可得到规则脉冲,再按时域参数测量原理得到PW和Pri;对于相位序列,按照频率测量原理可得到频率f;然后将PW、Pri及f值存人双口RAM,再将所存数据通过模拟串口从FPGA的通用I/O口传出,经MAX232电平转换后输入到计算机串口中,最后通过上位机显示出来,以实现人机通信。

5 结束语

本系统的输入信号要求为正交信号,通常可用于通信和雷达信号的后端数字信号处理。本系统采用相位差分算法来计算频率,运算简单,FPGA速度可以优化到200 M本系统利用了采样芯片和FPGA的高速性,从而实现了很高的测量精度和实时检测的目的;由于采用模拟串口进行传输,故其抗干扰性能较好。

测频和测脉宽现在有多种方法。通常基于MCU的信号参数测量,由于其MCU工作频率很低,所以能够达到的精度也比较低,而基于AD10200和 FPGA的时域测量精度往往可达10 ns,频率测量精度在100 kHz以内。适应信号的脉宽范围在100 ns~1 ms之间;重复周期在0.05~100ms:频率在0.1 Hz~50 MHz。

AD10200是高速采样芯片,其中内嵌变压器,因此采样电路外部不再需要变压器,使得电路设计更为简单;最低采样速率为105 MSPS,具有3.3 V或者5 V CMOS兼容输出电平,双通道12位采样,补码形式输出,每个通道功耗为0.850W。通常可应用于雷达中频信号接收机、相位组接收机、通信接收机、 GPS抗干扰接收机等。

StratixⅡ是Altera公司的中高端主流产品,该产品采用1.2 V、90 nm、9层信号走线,全铜SRAM工艺制造。StratixⅡ内嵌RAM块、DSP块、锁相环(PLL)和外部存储器接口,同时,StratixⅡ也增加了全新的逻辑结构一自适应逻辑模块(ALM),因而增加了动态相位对准(DPA)电路和对新的外部存储器接口的支持。AD芯片可以稳定工作在100 MHz,FPGA速度可高达几百MHz,故可保证系统的测量精度。

2 测量原理

2.1 时域测量原理

时域测量包括脉宽(PW)测量和脉冲重复周期(Pri)测量,时域测量在FPGA中可利用数字化技术实现。AD的两路输入为两路正交中频信号。经过Cordic算法,即幅相解算之后获得幅度和相位信息,其中利用幅度信息测得时域参数,其原理图如图1所示。

当脉冲信号进入FPGA后,将首先进行门限判定,以将不规则的脉冲信号进行整形并变为规则的脉冲信号。整形后,在脉冲信号上升沿启动脉宽计数器和重复周期计数器,而在该脉冲信号的下降沿锁存脉宽计数器并且在下个脉冲信号上升沿锁存重复周期计数器;由此即可得到脉宽和重复周期的量化值N和M,然后再通过工作时钟的计算,就可得出脉宽和重复周期。

2.2 频域参数测量

频域参数测量可由两路正交信号所携带的相位信息得到。对于输入正交采样I、Q两路序列,则可通过求反正切得到角度序列 θ(n)=arctg(I(n/Q(n),但此时得到的角度序列是周期性分布在(0,2π)之间的,因此需对此角度进行解模糊,可将角度序列解为递增直线,然后按照如下公式进行解模糊,并得到新的角度序列φ(n):

通过以上公式可以准确计算出脉内信号频率,从而达到测频的目的。

3 系统硬件电路设计

基于AD10200和FPGA芯片EP2S30F48414的脉冲信号测量系统的硬件电路原理如图2所示。此系统的输入信号要求为两路正交信号,正交信号在基带数字信号处理中经常要用到,它可以通过多种方法来实现,如模拟器件下变频或者是数字正交下变频等技术。IQ两路正交信号的特点为幅度相仿,相位相差90度。AD采样芯片负责将模拟信号转换为数字信号;电源芯片用于为AD、FPGA和MAX232供电;晶振用于提供工作时钟,选择24.576 MHz晶振的原因是因为FPGA与计算机串口通信时还要实现一个模拟串口,而选用24.576 MHz可以刚好模拟出9600 bit/s的波特率,从而可减少误码率:外部复位可为FPGA提供外部复位信号。MAX232是一个常用的电平转换芯片,可以将FPGA输出的LVTTL 3.3 V电平转换为串口电平,以便被计算机UART口所识别和接收。由以上芯片组成的系统工作频率为100 MHz,可实现快速、高精度地脉宽和频率测量。其中采样芯片和FPGA的硬件连接图如图3所示。

4 FPGA软件设计

本系统中的时域参数测量和频域参数测量工作由FPGA担任,其输入为正交信号两路序列,输出分别为脉宽(PW)、重复周期(Pri)和频率(f)。FPGA中的数字信号处理流程如图4所示。

图中,I(n)和Q(n)为两路正交信号序列;A (n)为幅度信息序列;为相位信息序列。

两路正交信号I(n)和Q(n) 序列经过幅相解算后,即可得到幅度序列和相位序列。对于幅度序列,经过低通滤波和归一化,可得到规则脉冲,再按时域参数测量原理得到PW和Pri;对于相位序列,按照频率测量原理可得到频率f;然后将PW、Pri及f值存人双口RAM,再将所存数据通过模拟串口从FPGA的通用I/O口传出,经MAX232电平转换后输入到计算机串口中,最后通过上位机显示出来,以实现人机通信。

5 结束语

本系统的输入信号要求为正交信号,通常可用于通信和雷达信号的后端数字信号处理。本系统采用相位差分算法来计算频率,运算简单,FPGA速度可以优化到200 M本系统利用了采样芯片和FPGA的高速性,从而实现了很高的测量精度和实时检测的目的;由于采用模拟串口进行传输,故其抗干扰性能较好。

上一篇:风力发电行业的完整测试解决方案综述

下一篇:电网谐波的产生及谐波干扰其检测方法分析