- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

信号完整性基础系列之十三——ISI和ISI Plot

一,关于ISI的文章典籍有哪些?

关于ISI,有两本比较有名的SI著作中有提到。在Intel的三位工程师合著的《高速数字系统设计——互连理论和设计实践手册》(p65-p66)中,对ISI的解释是:“当信号沿传输线传播时,总存在反射、串扰、或其它噪声源引起的噪声。这些噪声会影响发送到传输线上的信号,降低时序容限和信号完整性容限。这种现象称为ISI”。 在另外一个著名美籍华人SI专家李鹏(Mike Peng Li)的著作《高速系统设计——抖动、噪声和信号完整性》(p6-p7)中,有下面的描述,“在有损媒质中,(较高频率的)比特流可能会造成跳变时序和信号幅度偏离理想值。……由于容性效应,每次电平跳变都要有一定的电荷充放电时间。如果前次跳变的电平在达到预定电平之前,紧接着发生又一次跳变,那么当前比特就可能产生时间和电平量级的偏差,这种效应会级联累积” ,于是产生了ISI。 可能是由于翻译的原因,上段文字令人难以透彻理解ISI。我运用强大的google,但未能google出能帮助我写完此文的参考文献。 本文将从力科示波器测量的眼图特点来帮您识别什么是ISI,并介绍力科示波器分析ISI的一个重要工具ISI Plot及其对调试的实际帮助。

二、力科示波器“眼”中的ISI

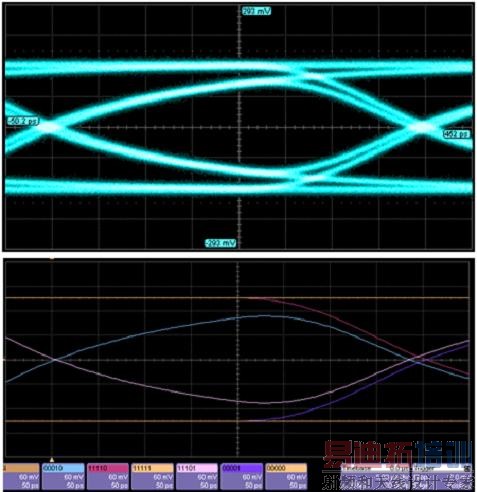

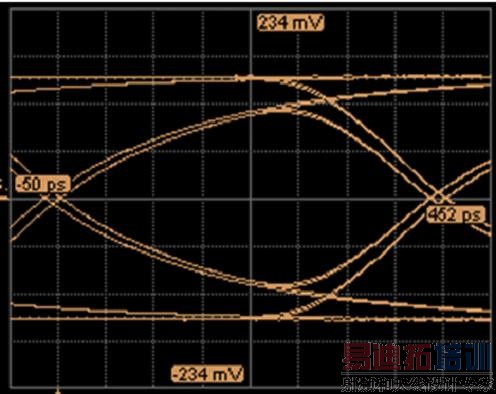

简单地说,ISI(intersymbol interference,码间干扰)是一种信号的失真,一种码型对相临的码型产生干扰。ISI是固有抖动(Dj)的主要来源。我们可以通过眼图的特点来判断是否有ISI存在。在力科示波器“眼”中,ISI表现为两种典型特征,分别如图一、二所示。不完美的“眼图”总是能说明点问题的,特别是这种不完美的“眼图”表现出这么强烈的规律时! 图一上图表示没有ISI时测量出的3.125Gbps信号的眼图,下图表示有ISI测量出的3.125Gbps的眼图,ISI带来的数据相关性抖动DDj(Dj的一部分)如红色区间所示。图二的上升沿产生了负向的凹脉冲,下降沿产生了正向的凸脉冲。

图一 上图表示没有ISI的3.125Gbps信号眼图,下面表示有ISI的眼图测量

图二 阻抗不匹配带来的ISI问题

三、基于力科串行数据分析仪的ISI Plot功能

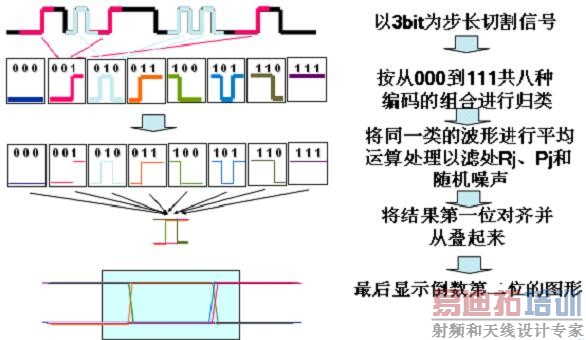

力科的串行数据分析SDA系列有一种独特的ISI Plot功能,可以将数据流中的相同次序的比特位组合起来进行平均从而消除掉噪声的影响,如图三所示。

图三 ISI Plot

ISI Plot是力科的一种专利方法,该方法利用历史上捕获到的波形的很多比特位来确定对某一给定的比特位的跳变沿的影响。用户可以选择屏幕上的比特位个数(3-10个)来测量。捕获的波形按选择的比特位个数来分段处理。譬如选择4个比特位,那么4 UI长度的数据段就会被扫描,总共有2的4次方16种组合的码型被定位和平均。譬如下面的数据流中共出现18次0010被平均,9次1101被平均,3次0001被平均。平均处理的过程中随机抖动,噪声和周期性抖动被去掉了。这些波形段叠加显示,最终2的4次方个平均后的波形都显示在ISI Plot上。 如图四所示。图五以3 UI长度图示了ISI Plot的实现原理。

图四 4 UI的ISI Plot

图五 3 UI的ISI Plot

四、引起ISI的原因及ISI Plot对分析ISI问题的帮助

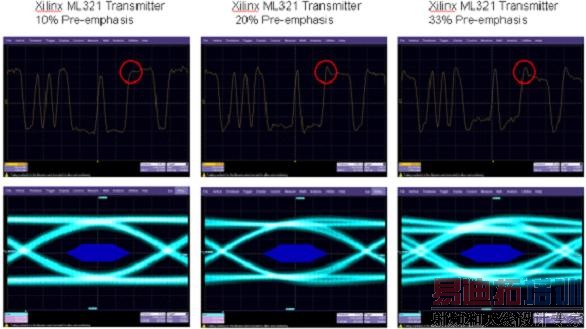

1,预加重过大

预加重过大会产生ISI。图六分别表示在10%、20%、33%三种预加种时的眼图测量结果。在33%预加重时的ISI明显增大。

图六 不同预加重时的眼图

2,数据码型的特点和传输通道对串行数据不同频率的码型频率响应

数据码型中包括有连续跳变沿(如101010……)的码型包括的频率成分是有些码型(如11001100……)的频率的两倍,更是另外一类码型(如111000111000……)的频率的三倍。 PCB传输介质的低通特性会过滤掉高频成分,其结果是会使高频码型幅值衰减,相位偏移。

3,数据比特位出现的次序

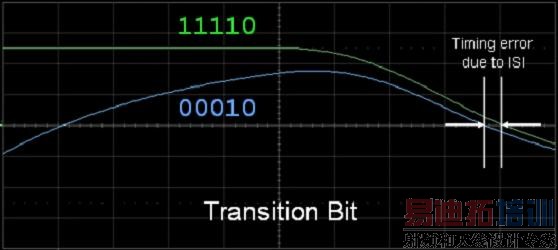

数据比特位出现的次序影响到数据跳变沿的时序。如下所示的串行数据流包含有码型00010 和11110,其中1->0 的跳变导致的过零点时刻不一样,于是带来了ISI问题,如图七所示,利用ISI Plot可以定位出这种时序上的差别。

图七 不同的比特位次序产生的ISI

4,阻抗不匹配

阻抗不匹配会导致容性传输线产生反射。含有高频能量的上升沿被反射,该反射会“拉低”电平。反之亦然。这通常意味着部分传输线有附加的电容或较低的阻抗。这种阻抗不匹配带来的ISI问题可以用ISI Plot的方法来定位,也可以用眼图模板失败定位功能来验证。阻抗不匹配带来的跌落出现在距离跳变沿的固定距离。 图八用ISI Plot揭示出的码型相关性是传统的眼图方法不能实现的。所有的上升沿都造成了负向的凹脉冲并且所有的下降沿造成了正向的凸脉冲,这意味着部分传输线有附加的电容,或较低的阻抗。

图八 ISI Plot揭示了码型相关性

利用眼图的模板失败跟踪功能也能从另外的角度分析这种阻抗不匹配问题。可以逐个观察每个被侵犯的模板码型查看边沿和跌落之间的关联性。如图九所示,还通过测量沿与脉冲之间的时间间隔可以估算出不匹配点的大致距离。

图九 模板失败跟踪功能可用来查看反射

五、如何降低ISI的影响

在《高速数字系统设计——互连理论和设计实践手册》一书中,提出了下面的一些降低ISI的经验方法,现摘录如下:

1.通过消除阻抗不连续,并使走线分支长度和较大的寄生效应(源自封装、插槽、或连接器)最小化,使得总线上的反射降为最小。

2.使互连通路尽可能短。

3.避免耦合紧密的弯曲走线。

4.合理选择线长,使得总线上传输信号时的同时,不会发生信号完整性问题(即振铃、信号突起、信号过冲等)。

5.使串扰影响最小化。