- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

SoC测试技术面临的挑战和发展趋势

录入:edatop.com 点击:

中国是全球半导体市场成长最快的区域,预计每年增长率超过25%,原因在于中国已经成为全球集成电路消费的中心、电子产品巨大的消费市场和整机制造基地,为了贴近终端市场和IC用户,SoC测试中心和实验室在中国的布局已经悄然展开,本文将向您介绍SoC测试技术领域面临的挑战和最新的测试技术趋势。

目前,IC消耗量的主要增长集中在消费电子、数据处理和通信三大领域,其中消费电子包括显示器、数码相机、数字电视和视频游戏机,数据处理包括CPU和存储器、闪存卡、平面监视器和移动PC,通信领域则以数字蜂窝电话和无线/有线网络为增长驱动力。IC复杂度的日益提高,迫使设计人员采用更为先进的工艺技术,将更多的功能集成到单芯片内,系统级芯片(System on Chip, SoC)因此受到广泛应用,目标是进一步降低整机系统设计、测试和制造的成本。

目前,0.25和0.18um工艺技术占据主导地位,0.13um以下工艺技术已经在一些高端产品中得到应用,并呈现急速增长的趋势。采用先进设计工艺的结果,是造成设计、掩膜费用在NRE中的比例逐年上升,已经由1995年的13%激增为2003年的62%,推出新型芯片受到降低成本需求的强劲驱动,但是设计和制造新型芯片的总成本却因新工艺技术的应用而急剧增加。

而另一方面,新型电子产品的生命周期越来越短已经是不争的事实,它们从切入市场到实现百万台的量产规模,时间通常不到一年,因此,业界流传这样的说法:90%的利润是产品上市后头六个月产生的,“Time-To-Market”是整个半导体产业仅次于芯片复杂度面对的第二大挑战。

在紧迫的上市时间和芯片复杂度日益提高的双重压迫下,半导体行业被迫构建新的外包链条,并力图结成更多的技术联盟,共同推进技术和市场的发展,其中一个重要趋势就是代工厂更倾向于提供一揽子解决方案,帮助集成电路设计公司更快地推出芯片,而业界占据领先地位的厂家更倾向于采用先进的测试技术,本文试图对SoC测试领域面临的挑战和技术发展趋势做一个初步探讨。

传统的测试方法和流程面临的挑战

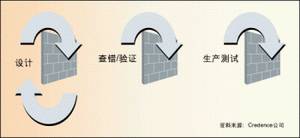

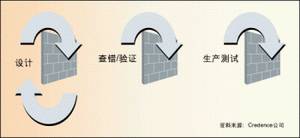

传统的设计和测试方法将设计、调试/验证、生产测试三个环节孤立起来进行,其突出的问题是除非首颗芯片制造出来,否则芯片测试不可能真正完成,如图1所示。传统的测试方法和流程由于需要多次反复,因而不能适应复杂的SoC大规模量产的需要,更难降低成本。对于SoC测试来说,人们需要开发更为有效的测试程序,以满足一次性流片对验证工具以及生产测试环节对更具有成本效益的测试软件的需要。

目前,人们开发测试程序通常沿着设计、测试程序开发、芯片原型验证的思路进行,各部分孤立地进行任务分配、需求分析,然后分别执行,测试的过程还要不断完善测试软件。测试程序开发完成之后,还要对测试程序本身进行调试,通常需要多次反复修改测试程序,时间上也需要几个月的时间。这对于“6个月赢得90%利润”的市场法则来说是难以接受的,解决测试程序本身调试需要较长时间这个问题,迫使人们进一步改进设计和测试的流程。

一体化测试流程

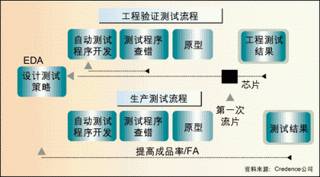

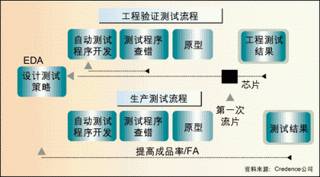

为了解决上述问题,图2所示是一种新的测试流程。它将工程设计验证测试流程与生产测试流程并行处理。其核心思想是利用虚拟原型对测试工程和IC设计过程所需要的测试程序(本身)进行查错和调试,同时,也将虚拟原型应用到生产测试流程之中,完成面向生产的测试程序的查错和调试。

为此,首先要根据工程测试结果,进行设计中的测试策略规划,目的是改进测试方法,降低测试的复杂性,并根据测试成本和复杂性对测试任务进行定义。而生产测试流程中,测试程序查错和调试的主要任务是提高成品率。

FPGA和PLD在搭建虚拟原型,完成对测试程序调试的过程中扮演着重要作用。通过利用虚拟环境,可以极大地降低对测试程序进行调试所花费的时间,减少掩膜次数,节省大量、昂贵的掩膜费用,提高成品率,并在加快产品上市时间的同时,达到芯片利润的最大化。

然而,尽管上述方法解决了缩短测试程序调试时间的问题,但是,需要在设计和生产两条线上同时对测试程序进行调试,因而资金投入上并没有显著降低,为此,Credence公司提出了利用光子进行SoC测试的新技术。

基于光子探测的SoC测试技术

随着芯片复杂度的增加,SoC采用倒装、打线和多层金属封装的方式也越来越多,许多地方采用传统的电测手段已经相当费时费力,因此,Credence利用固态浸入透镜方法实现0.25um的成像分辨率,来完成对SoC关键节点的性能进行分析。通过测试系统配备的高速采集和数据处理能力,半导体制造商能够快速进行设计查错、故障分析和特征提取,从而极大地缩短产品上市时间并降低SoC开发的成本。

基于光子探测的SoC测试技术的基本原理是,利用脉冲信号切换产生的能量,激发半导体电路内部的电子被激发出光子,然后通过高速采集和数据处理系统,将采集的光子转化为电子信号,通过对这些电信号来分析时序特征,从而达到对SoC关键节点进行测试的目的。其目的是加速产品的上市,消除不必要的多次设计修改和不必要的流片循环。

本文小结

SoC技术是21世纪初以来迅速发展起来的超大规模集成电路的主流技术,是电子器件持续集成的最高境界。SoC采用先进的超深亚微米CMOS工艺技术,从整个系统的角度出发,将处理机制、模型算法、嵌入式软件等各层次电路直至器件的设计紧密结合在单个芯片上,完成整个系统的功能。

随着SoC应用的日益普及,在测试程序生成、工程开发、硅片查错、量产等领域对SoC测试技术提出了越来越高的要求,掌握新的测试理念、新的测试流程、方法和技术,是应对消费电子、通信和计算等领域SoC应用对测试技术提出的挑战,适应测试和组装外包发展趋势的必然要求。对于中国集成电路测试人员来说,了解中国目前SoC测试技术发展面临的挑战和发展方向,掌握市场的动态至关重要,表1所示为中国目前已经具备SoC测试能力的测试中心和实验室的一览表。

目前,IC消耗量的主要增长集中在消费电子、数据处理和通信三大领域,其中消费电子包括显示器、数码相机、数字电视和视频游戏机,数据处理包括CPU和存储器、闪存卡、平面监视器和移动PC,通信领域则以数字蜂窝电话和无线/有线网络为增长驱动力。IC复杂度的日益提高,迫使设计人员采用更为先进的工艺技术,将更多的功能集成到单芯片内,系统级芯片(System on Chip, SoC)因此受到广泛应用,目标是进一步降低整机系统设计、测试和制造的成本。

目前,0.25和0.18um工艺技术占据主导地位,0.13um以下工艺技术已经在一些高端产品中得到应用,并呈现急速增长的趋势。采用先进设计工艺的结果,是造成设计、掩膜费用在NRE中的比例逐年上升,已经由1995年的13%激增为2003年的62%,推出新型芯片受到降低成本需求的强劲驱动,但是设计和制造新型芯片的总成本却因新工艺技术的应用而急剧增加。

而另一方面,新型电子产品的生命周期越来越短已经是不争的事实,它们从切入市场到实现百万台的量产规模,时间通常不到一年,因此,业界流传这样的说法:90%的利润是产品上市后头六个月产生的,“Time-To-Market”是整个半导体产业仅次于芯片复杂度面对的第二大挑战。

在紧迫的上市时间和芯片复杂度日益提高的双重压迫下,半导体行业被迫构建新的外包链条,并力图结成更多的技术联盟,共同推进技术和市场的发展,其中一个重要趋势就是代工厂更倾向于提供一揽子解决方案,帮助集成电路设计公司更快地推出芯片,而业界占据领先地位的厂家更倾向于采用先进的测试技术,本文试图对SoC测试领域面临的挑战和技术发展趋势做一个初步探讨。

传统的测试方法和流程面临的挑战

传统的设计和测试方法将设计、调试/验证、生产测试三个环节孤立起来进行,其突出的问题是除非首颗芯片制造出来,否则芯片测试不可能真正完成,如图1所示。传统的测试方法和流程由于需要多次反复,因而不能适应复杂的SoC大规模量产的需要,更难降低成本。对于SoC测试来说,人们需要开发更为有效的测试程序,以满足一次性流片对验证工具以及生产测试环节对更具有成本效益的测试软件的需要。

目前,人们开发测试程序通常沿着设计、测试程序开发、芯片原型验证的思路进行,各部分孤立地进行任务分配、需求分析,然后分别执行,测试的过程还要不断完善测试软件。测试程序开发完成之后,还要对测试程序本身进行调试,通常需要多次反复修改测试程序,时间上也需要几个月的时间。这对于“6个月赢得90%利润”的市场法则来说是难以接受的,解决测试程序本身调试需要较长时间这个问题,迫使人们进一步改进设计和测试的流程。

一体化测试流程

为了解决上述问题,图2所示是一种新的测试流程。它将工程设计验证测试流程与生产测试流程并行处理。其核心思想是利用虚拟原型对测试工程和IC设计过程所需要的测试程序(本身)进行查错和调试,同时,也将虚拟原型应用到生产测试流程之中,完成面向生产的测试程序的查错和调试。

为此,首先要根据工程测试结果,进行设计中的测试策略规划,目的是改进测试方法,降低测试的复杂性,并根据测试成本和复杂性对测试任务进行定义。而生产测试流程中,测试程序查错和调试的主要任务是提高成品率。

FPGA和PLD在搭建虚拟原型,完成对测试程序调试的过程中扮演着重要作用。通过利用虚拟环境,可以极大地降低对测试程序进行调试所花费的时间,减少掩膜次数,节省大量、昂贵的掩膜费用,提高成品率,并在加快产品上市时间的同时,达到芯片利润的最大化。

然而,尽管上述方法解决了缩短测试程序调试时间的问题,但是,需要在设计和生产两条线上同时对测试程序进行调试,因而资金投入上并没有显著降低,为此,Credence公司提出了利用光子进行SoC测试的新技术。

基于光子探测的SoC测试技术

随着芯片复杂度的增加,SoC采用倒装、打线和多层金属封装的方式也越来越多,许多地方采用传统的电测手段已经相当费时费力,因此,Credence利用固态浸入透镜方法实现0.25um的成像分辨率,来完成对SoC关键节点的性能进行分析。通过测试系统配备的高速采集和数据处理能力,半导体制造商能够快速进行设计查错、故障分析和特征提取,从而极大地缩短产品上市时间并降低SoC开发的成本。

基于光子探测的SoC测试技术的基本原理是,利用脉冲信号切换产生的能量,激发半导体电路内部的电子被激发出光子,然后通过高速采集和数据处理系统,将采集的光子转化为电子信号,通过对这些电信号来分析时序特征,从而达到对SoC关键节点进行测试的目的。其目的是加速产品的上市,消除不必要的多次设计修改和不必要的流片循环。

本文小结

SoC技术是21世纪初以来迅速发展起来的超大规模集成电路的主流技术,是电子器件持续集成的最高境界。SoC采用先进的超深亚微米CMOS工艺技术,从整个系统的角度出发,将处理机制、模型算法、嵌入式软件等各层次电路直至器件的设计紧密结合在单个芯片上,完成整个系统的功能。

随着SoC应用的日益普及,在测试程序生成、工程开发、硅片查错、量产等领域对SoC测试技术提出了越来越高的要求,掌握新的测试理念、新的测试流程、方法和技术,是应对消费电子、通信和计算等领域SoC应用对测试技术提出的挑战,适应测试和组装外包发展趋势的必然要求。对于中国集成电路测试人员来说,了解中国目前SoC测试技术发展面临的挑战和发展方向,掌握市场的动态至关重要,表1所示为中国目前已经具备SoC测试能力的测试中心和实验室的一览表。

上一篇:让每位电子工程师都能拥有专业级的测试测量仪器

下一篇:产品聚焦:手持测试设备