- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的虚拟DPO设计方案

1.1项目背景

示波器(Oscilloscope)是一种能够显示电压信号动态波形的电子测量仪器。它能够将时变的电压信号转换为时域上的曲线,原来不可见的电气信号,转换为在二维平面上直观可见光信号,由此能够分析电气信号的时域性质。

目前,全球主要的示波器生产厂商都集中在美国,而高端示波器更是被美国Tektronix公司、Agilent公司和LeCory公司所垄断。如Agilent公司的高性能90000系列Infiniium示波器在4个通道上均达到40-GSPS采样率,并同时提供超低噪声的13 GHz全实时示波器带宽,存储深度也达到了1Gpts。

而国内方面,由于在高速模数转换器和专用集成电路方面与发达国家的差距,市场上同类示波器的最高采样率、模拟带宽和存储深度等主要指标还落后很多。本课题是开发具有自主知识产权的数字荧光示波器的采集与存储系统。为高性能采集存储技术积累开发经验。同时填补我国数字荧光示波器的空白以及缩小与国外同类示波器发展水平的差距。

1.2数字荧光示波器

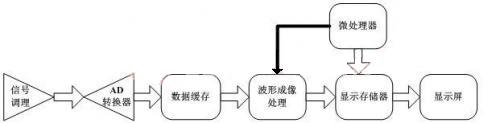

数字荧光示波器(DPO)是Tektronix公司推出的一种示波器平台,它具有数字存储示波器的各种传统优点,如数据存储和先进的触发功能等。同时,它也具有模拟实时示波器的明暗显示和实时特性,能以数字形式产生显示效果优于模拟示波器的亮度渐次变化的荧光效果。其结构如图1所示。

图1 数字荧光示波器原理框图

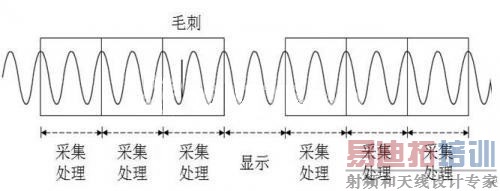

数字存储示波器因需要微处器理显示数据,导致在显示两幅波形之间有一定毫秒级的停滞时间;模拟示波器在回扫时间内也不能捕捉波形信息。而DPO的数据采集和显示模块并行运行,使得DPO能够在处理显示数据的同时,继续采集信号数据。同时,与DSO不同的是,DPO是在连续进行多次采集与处理后再进行一次显示。由于DPO一般采用专用硬件电路进行采集波形的数字荧光处理,不再受限于微处理器对数据的低速处理,使得波形的更新率有了质的提高。所以DPO能够连续不断得捕捉波形的绝大部分细节,可以完整的反映波形信息,同时也为后续的分析处理提供了完整的数据。如图2所示。

数字荧光显示技术的应用使DPO能以不同的亮度或色彩显示信号在某一特定位置出现的频率,频率越高,则亮度越高。数字荧光处理器一般由专用的硬件电路(高速FPGA或ASIC)构成。与DSO一样,输入信号首先经放大和A/D变换后得到信号的采样值,采样值经过数字荧光处理单元的处理后形成一幅包含波形三维信息的完整波形图,在不中断采集过程的情况下,数字荧光处理单元每秒向波形显存储器传输约30幅完整的具有荧光显示效果的波形图像,在微处理器的控制下,将波形图像显示在示波器的荧光屏上,达到模拟示波器的荧光显示效果。与此同时,微处理器可以并行方式执行自动测量及运算等各种功能。

图2 数字荧光示波器采集示意图

DPO每秒钟捕获的波形数可以高达到几十万帧,比一般的DSO高几千倍甚至上万倍。这种快速波形捕获速率结合超强的显示能力,使DPO具有分析信号任何细节的性能。同时由于采用了数字处理,又具备数字存储示波器的优点。

1.3项目特点

本项目的数字荧光示波器(DPO,Digital Phosphor Oscilloscope)是最新一代的示波器,它集成了数字存储示波器和模拟示波器的优点,既有数字存储示波器的波形存储,瞬态捕获,负延时触发和高级触发等功能,又有模拟示波器的实时捕获,高波形更新率和亮度渐次变化的显示效果等特性。

利用FPGA丰富的逻辑资源和强大的数据处理能力,在FPGA模块中实现主要的DPX模块,即数字荧光处理模块,同时,利用USB接口将处理后的数据传到PC机处理,利用PC机进行进一步的分析处理与显示。由于采用FPGA设计,系统的复杂度大为降低,也方便升级与更新,同时,可通过USB口对FPGA模块进行供电,极大的方便了工程师的调试,使该DPO具有很好的便携性。

总体方案设计与论证

虚拟数字荧光示波器可以简单描述为这样一个系统:用户通过PC机菜单设定采集触发参数,示波器根据用户的设定采集数据,并将采集到的数据做数字荧光处理,生成波形图像经DPX处理后经USB传送到PC机最后在液晶屏上显示出来,同时,采集到的数据还可以做进一步的分析处理。因此,示波器可以分成两大部分,一部分负责监控命令和波形、菜单的显示;另一部分负责高速数据采集和数字荧光成像。 [p]

2.1总体框图

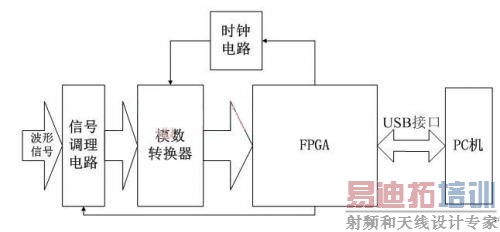

根据上述分析,制定以下设计方案:该示波器采用FPGA架构,FPGA作为系统控制核心负责监控PC机上发送过来的按键命令并根据当前的工作状态发送相应的采集控制命令给采集模块,同时还控制着数字荧光处理模块生成的波形图像和控制菜单,另一方面,由于其高速的特点,用于实现高速数据采集系统以及数字荧光处理器。整体实现框图如图3所示。其中模数转换器、时钟电路和FPGA共同构成了示波器的采集系统,FPGA内部实现DPX模块,最后通过USB上传到PC机处理显示。

图3 虚拟DPO组成框图

2.2信号调理电路

信号调理电路主要由衰减放大电路、耦合控制电路和直流偏置电路组成,由FPGA控制。

衰减放大电路调整输入波形的幅度范围,把不同幅度的信号进行衰减或放大以适应屏幕的显示范围,便于观察和测量。

耦合控制电路控制输入信号的耦合方式,分别为交流耦合和直流耦合,在直流耦合方式时,信号的所有分量(交流和直流)都被采集显示出来,而在交流耦合方式时,信号的直流分量被阻断,只有交流分量被采集显示出来。

直流偏置电路给信号加入直流分量,可以控制信号在屏幕中上下移动。另外,示波器的输入阻抗和模拟带宽也由信号调理电路所决定。在本项目中,信号调理电路的输入阻抗为50欧姆和1M欧姆可选。模拟带宽为500MHz。

2.3数据采集系统

数据采集系统由到模数转换器(Analog Digital Convertor, ADC)、时钟芯片和FPGA中相关采集控制模块组成。

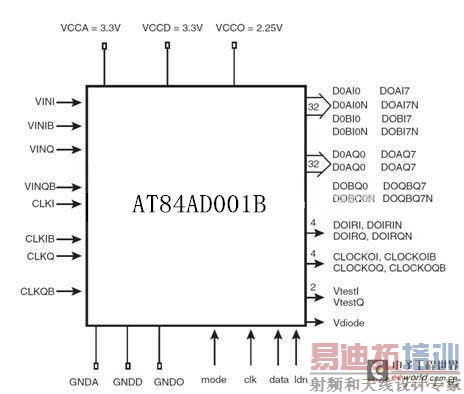

2.3.1模数转换

本设计选用e2v公司的AT84AD001B模数转换器。其接口如图4所示。该ADC为并行比较结构,速度快,但功耗大。其将两路ADC集成在一个芯片中,每路ADC最高采样率达1GHz,量化精度八比特,另外该芯片还支持交织采样的功能,即同一芯片中的两路ADC同时采集同一路模拟信号,并且其采样时钟相位相反,将这两路ADC的抽样数据拼接起来可获得2GSPS的最高采样率。AT84AD001B的主要特性如下:

◇双路ADC,每通道采样率1GSPS,交织采样模式下可达2GSPS;

◇输出编码为格雷码和二进制编码可选,支持1:1和1:2复用输出;

◇支持模拟输入切换选择,采样时钟选择;

◇支持增益控制和零电平调节;

◇采样率1GSPS时误比特率不超过;

◇串行配置工作模式,源同步时钟数据输出;

图4 模数转换器AT84AD001B接口框图

2.3.2时钟电路

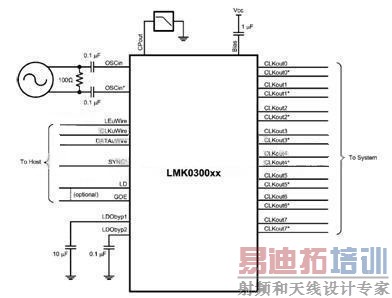

在本项目中,采用了National Semiconductor公司的高精度时钟管理芯片LMK03033C.其时钟抖动的均方根值为500飞秒。该芯片内置低噪声锁相环并且支持8路时钟同步输出,支持串行配置。每路输出时钟都带有可编程的分频比、延迟调整和输出选择模块,最高输出时钟频率1GHz,且可在0 至2.25ns 的范围内调节输出延时,步进为150ps.该芯片为高速ADC采集数据提供了精确的采样时钟。接口如图5所示。

图5 时钟管理芯片接口图

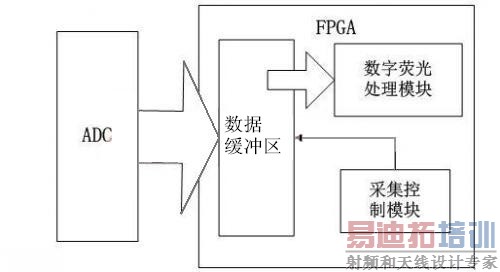

2.3.3采集控制和数据缓冲

模数转换器输出的高速数字信号在采集控制模块的控制下写入数据缓冲区,之后进行数字荧光处理。如图6所示。对于高速数字信号的控制和缓冲一般采用高速数字电路实现。一种方案是采用专用集成电路(ASIC)实现高速控制和数据缓冲。但是,专用集成电路成本极高,而且不能修改,一般用于经过充分验证的,成熟的数字电路设计。另一种方案是采用高速FPGA。 [p]

图6 采集控制框图

现场可编程门阵列(Field Programmable Gate Array, FPGA)是一种含有可编程元件的设备,其速度一般比专用集成电路慢,但仍快于通用微处理器,适合做高速数据控制器。并且FPGA的可编程特性和低廉的价格适合项目初期开发阶段的原型验证。

示波器的采集控制和数据缓冲模块是在FPGA中完成的,该模块根据用户设定的触发条件,从无限长的波形信号中截取用户感兴趣的部分来显示。数据存储系统的存取控制模块也在FPGA中实现。

2.4数字荧光处理模块

数字荧光处理单元的主要工作有如下几个方面:

(1) 进行波形的荧光显示,达到模拟示波器的荧光显示效果

数字荧光示波器将采集到的波形进行荧光显示,通过波形亮度显示长时间内信号出现的频度情况,完整地保留了多个通道波形显示的亮度层次信息,达到模拟示波器的荧光显示效果。在某一点的出现频度越大,该点在荧光屏上显示的亮度就越大;在某一点的出现频度越小,该点在荧光屏上显示的亮度就越小。

(2) 网格的调节控制

当利用数字荧光示波器观测信号时,为了观测精确,需要荧光屏在显示波形信号的同时显示网格。

(3) 波形荧光显示亮度的调节控制

当利用数字荧光示波器观测信号时,显示的波形亮度会直接影响到观测效果,过亮或者过暗的波形,会使波形的细节分辨不清,都不利于用户观测。因此,需要加入波形荧光显示亮度的调节功能,使用户可以调节荧光屏上显示的波形亮度,有利于波形观测。

(4) 波形消隐百分比的调节控制

当利用数字荧光示波器观测信号时,有时需要使波形在屏幕上滞留一定的时间后再消失,或者有时需要将出现的波形永远显示在荧光屏上,如毛刺等偶发信号。因此,需要加入波形消隐百分比的调节功能,使用户可以调节波形在荧光屏上显示的持续时间。

(5) 多通道波形的荧光显示及通道优先级的控制

当示波器同时观测多个通道时,不同的通道应该显示为不同的颜色以示区分。同时,多个通道同时显示时,应有优先级的区分,即哪一个通道应该显示在最上层。用户应该能够通过调节控制,将最关心的通道波形显示在所有波形的最上层,便于波形观测。

(6) 满足数字荧光示波器实时显示的要求

示波器是一种实时测量仪器,需要满足波形实时显示的要求。因此在进行波形的荧光显示时,要尽量提高处理速度,以提高实时性。

本章将首先详细介绍数字荧光处理单元的设计思想,并在此基础上,具体介绍数字荧光处理单元的设计及实现。

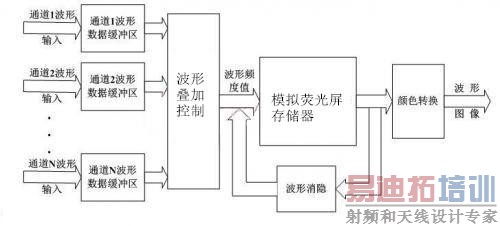

由需求分析可知,为了实现波形的荧光显示,首先需要定时一段时间,将在这段时间内采集到的若干次波形进行叠加,并记录所有波形点出现的频度。因此数字荧光处理单元内部需要设计一个存储器,以记录一段时间内所有波形点出现的频度,称之为模拟荧光屏存储器。同时,需要一个波形叠加处理模块,完成将若干次波形进行叠加后的频度存储到模拟荧光屏存储器的功能。

然后,当定时时间到时,将之前叠加储存在模拟荧光屏存储器中的所有单元信息读出,经过颜色转换形成一帧波形图像送显示器进行显示;同时将读出的模拟荧光屏存储器中的所有单元信息进行消隐处理,再写回模拟荧光屏存储器。

送到显示器进行显示的一帧波形图像是一幅和显示屏的波形显示区具有同样大小和分辨率的像素图像。它的原始信息是存储在模拟荧光屏存储器中的。模拟荧光屏存储器实际上是一个二维的动态数据库。数据库的地址单元是与波形显示区的像素点一一对应的。因此数据库的大小由数字荧光示波器的荧光屏波形显示区的总像素点确定。横轴对应于时间轴,纵轴对应幅度轴。规定显示区的左下角对应数据库的起始单元,其后的数据单元按对应屏幕从左到右,从下到上的次序排列。

由上可知,整个数字荧光处理单元应包括五个子单元协同工作:波形数据缓冲存储器、模拟荧光屏存储器、波形激活处理模块、波形消隐处理模块和颜色转换处理模块等,它们共同完成多路波形的数字荧光处理,并每隔一定时间形成一帧波形图像输出给显示器,同时进行一次消隐处理。各个子单元之间的联系如图7所示。

图7 数字荧光处理单元框图

2.5 PC机部分

PC机与FPGA经USB进行数据交互(DPX数据与控制信息),PC机通过USB给FPGA供电,DPX数据经USB传到PC机后通过LABwindows处理显示。

上一篇:基于DSP的数字存储示波卡的设计方案

下一篇:DigRF的物理层测试方法