- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA和DDS的信号源设计

录入:edatop.com 点击:

1 引言

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率高、相位可连续变化和输出波形灵活等优点,因此,广泛应用于教学科研、通信、雷达、自动控制和电子测量等领域。该技术的常用方法是利用性能优良的DDS专用器件,“搭积木”式设计电路,这种“搭积木”式设计电路方法虽然直观,但DDS专用器件价格较贵,输出波形单一,使用受到一定限制,特别不适合于输出波形多样化的应用场合。随着高速可编程逻辑器件FPGA的发展,电子工程师可根据实际需求,在单一FPGA上开发出性能优良的具有任意波形的DDS系统,极大限度地简化设计过程并提高效率。本文在讨论DDS的基础上,介绍利用FPGA设计的基于DDS的信号发生器。

2 DDS技术工作原理

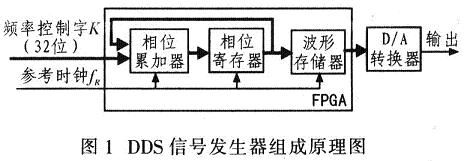

DDS是一种从相位概念出发直接合成所需波形的数字频率合成技术,主要通过查波形表实现。由奈奎斯特抽样定理理论可知,当抽样频率大于被抽样信号的最高频率2倍时,通过抽样得到的数字信号可通过一个低通滤波器还原成原来的信号。DDS信号发生器,主要由相位累加器、相位寄存器、波形存储器、D/A转换器和模拟低通滤波器组成如图1所示。fR为参考时钟,K为输入频率控制字,其值与输出频率相对应,因此,控制输入控制字K,就能有效控制输出频率值。通常情况下,K值由控制器写入。

f0=(K/2N)fR (1)

式中,K为频率控制字;fR为参考时钟,N为累加器的位宽值。

当K=l时,可得DDS的最小分辨率为:

fmin=fR/2 (2)

为了得到较小分辨率,在实际工程设计中,N一般取得较大值,该系统是N取32位设计的。

3 关键器件选型

本设计所用到的关键器件主要是可编程逻辑器件(FPGA)和D/A转换器。考虑设计成本等因素,FPGA采用Altera公司的低成本Cyclone系列EPlC6Q240C8。该器件采用逻辑阵列模块(LAB)和查找表(LUT)结构,内核采用1.5 V电压供电,是低功耗元件。此外,Cyclone系列EPlC60240C8内部资源丰富,其内部内嵌5 980个逻辑单元(LE),20个4 KB双口存储单元(M 4 KB RAM block)和92 160 bit普通高速RAM等资源,因此,能较好满足该系统设计要求。而D/A转换器则采用National Semiconductor公司的DAC0832。

4 DDS的FPGA实现

4.1 相位累加器与相位寄存器的设计

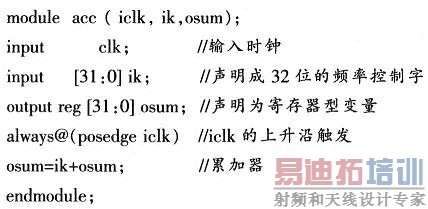

相位累加器与相位寄存器主要完成累加,实现输出波形频率可调功能。利用Quartus II可编程逻辑器件系统开发工具进行设计。首先,打开Quartus II软件,新建一个工程管理文件,然后在此工程管理文件中新建一个Verilog HDL源程序文件,并用硬件描述语言Verilog HDL编写程序实现其功能。在设计过程中,可在一个模块中描述。一个参考的Verilog HDL程序如下:

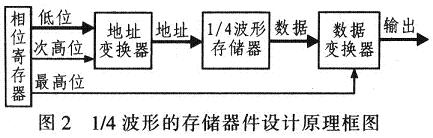

为了提高系统的分辨率和降低FPGA资源的利用率,采用基于1/4波形的存储器设计技术。利用正弦波对称性特点,只要存储[O~π/2]幅值,通过地址和幅值数据变换,即可得到整个周期内的正弦波,其设计原理如图2所示。 [p]

5 D/A转换电路

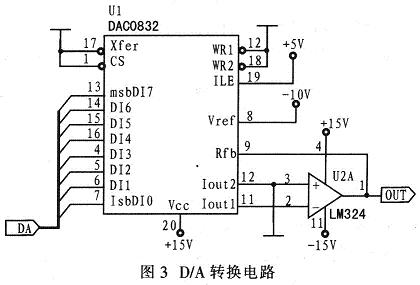

数据转换器输出的数据是数字形式的电压值,为实现数字电压值与模拟电压值之间的转换,系统还专门设计D/A转换电路,其D/A转换电路原理图如图3所示。

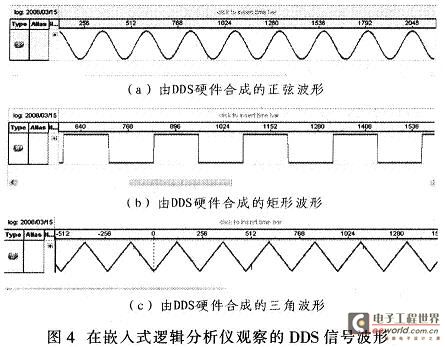

6 验证结果

为验证本系统的设计正确性,利用Ouarlus II软件的嵌入式逻辑分析仪分析信号的波形。在工程管理文件中,首先新建一个SignalTap文件,并在SignalTap文件中添加要验证的信号引脚和设置相关的参数,然后保存、编译和下载到EPlC6Q240C8中,再启动嵌入式逻辑分析仪就可实时观察到相应的引脚波形,图4为在硬件环境中应用嵌入式逻辑分析仪观察到的波形。其中,图4a为由DDS硬件合成的正弦波形;图4b为由DDS硬件合成的矩形波形;图4c为由DDS硬件合成的三角波形。观察结果表明,该系统输出的各种波形稳定,与设计要求一致,从而有效验证了该设计的正确性。

直接数字频率合成(DDS)技术属第三代频率合成技术,与第二代基于锁相环频率合成技术相比,利用DDS技术合成的输出波形具有良好的性能指标。本文在DDS技术工作原理的基础上,介绍基于FPGA实现DDS的设计方法,并给出该系统合成的波形,从测试结果可看出,该系统工作稳定、可靠,并具有较好的参考与实用价值。

直接数字频率合成DDS(Direct Digital Synthesizer)是基于奈奎斯特抽样定理理论和现代器件生产技术发展的一种新的频率合成技术。与第二代基于锁相环频率合成技术相比,DDS具有频率切换时间短、频率分辨率高、相位可连续变化和输出波形灵活等优点,因此,广泛应用于教学科研、通信、雷达、自动控制和电子测量等领域。该技术的常用方法是利用性能优良的DDS专用器件,“搭积木”式设计电路,这种“搭积木”式设计电路方法虽然直观,但DDS专用器件价格较贵,输出波形单一,使用受到一定限制,特别不适合于输出波形多样化的应用场合。随着高速可编程逻辑器件FPGA的发展,电子工程师可根据实际需求,在单一FPGA上开发出性能优良的具有任意波形的DDS系统,极大限度地简化设计过程并提高效率。本文在讨论DDS的基础上,介绍利用FPGA设计的基于DDS的信号发生器。

2 DDS技术工作原理

DDS是一种从相位概念出发直接合成所需波形的数字频率合成技术,主要通过查波形表实现。由奈奎斯特抽样定理理论可知,当抽样频率大于被抽样信号的最高频率2倍时,通过抽样得到的数字信号可通过一个低通滤波器还原成原来的信号。DDS信号发生器,主要由相位累加器、相位寄存器、波形存储器、D/A转换器和模拟低通滤波器组成如图1所示。fR为参考时钟,K为输入频率控制字,其值与输出频率相对应,因此,控制输入控制字K,就能有效控制输出频率值。通常情况下,K值由控制器写入。

f0=(K/2N)fR (1)

式中,K为频率控制字;fR为参考时钟,N为累加器的位宽值。

当K=l时,可得DDS的最小分辨率为:

fmin=fR/2 (2)

为了得到较小分辨率,在实际工程设计中,N一般取得较大值,该系统是N取32位设计的。

3 关键器件选型

本设计所用到的关键器件主要是可编程逻辑器件(FPGA)和D/A转换器。考虑设计成本等因素,FPGA采用Altera公司的低成本Cyclone系列EPlC6Q240C8。该器件采用逻辑阵列模块(LAB)和查找表(LUT)结构,内核采用1.5 V电压供电,是低功耗元件。此外,Cyclone系列EPlC60240C8内部资源丰富,其内部内嵌5 980个逻辑单元(LE),20个4 KB双口存储单元(M 4 KB RAM block)和92 160 bit普通高速RAM等资源,因此,能较好满足该系统设计要求。而D/A转换器则采用National Semiconductor公司的DAC0832。

4 DDS的FPGA实现

4.1 相位累加器与相位寄存器的设计

相位累加器与相位寄存器主要完成累加,实现输出波形频率可调功能。利用Quartus II可编程逻辑器件系统开发工具进行设计。首先,打开Quartus II软件,新建一个工程管理文件,然后在此工程管理文件中新建一个Verilog HDL源程序文件,并用硬件描述语言Verilog HDL编写程序实现其功能。在设计过程中,可在一个模块中描述。一个参考的Verilog HDL程序如下:

为了提高系统的分辨率和降低FPGA资源的利用率,采用基于1/4波形的存储器设计技术。利用正弦波对称性特点,只要存储[O~π/2]幅值,通过地址和幅值数据变换,即可得到整个周期内的正弦波,其设计原理如图2所示。 [p]

5 D/A转换电路

数据转换器输出的数据是数字形式的电压值,为实现数字电压值与模拟电压值之间的转换,系统还专门设计D/A转换电路,其D/A转换电路原理图如图3所示。

6 验证结果

为验证本系统的设计正确性,利用Ouarlus II软件的嵌入式逻辑分析仪分析信号的波形。在工程管理文件中,首先新建一个SignalTap文件,并在SignalTap文件中添加要验证的信号引脚和设置相关的参数,然后保存、编译和下载到EPlC6Q240C8中,再启动嵌入式逻辑分析仪就可实时观察到相应的引脚波形,图4为在硬件环境中应用嵌入式逻辑分析仪观察到的波形。其中,图4a为由DDS硬件合成的正弦波形;图4b为由DDS硬件合成的矩形波形;图4c为由DDS硬件合成的三角波形。观察结果表明,该系统输出的各种波形稳定,与设计要求一致,从而有效验证了该设计的正确性。

直接数字频率合成(DDS)技术属第三代频率合成技术,与第二代基于锁相环频率合成技术相比,利用DDS技术合成的输出波形具有良好的性能指标。本文在DDS技术工作原理的基础上,介绍基于FPGA实现DDS的设计方法,并给出该系统合成的波形,从测试结果可看出,该系统工作稳定、可靠,并具有较好的参考与实用价值。

上一篇:精确的频率测量和时间测量

下一篇:是德科技推出扫描速度超快的

9500原子力显微镜