- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

更快地对高速存储故障深入调试三大步骤

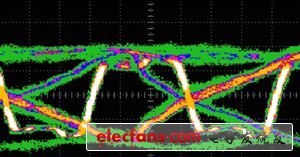

图1:DDRII激活时的高分辨率定时轨迹。

各种子系统、不同工作模式和多种循环导致的串扰和资源冲突一直是引起许多间歇性内存故障的根本原因。对于间歇性内存故障,查找其根本原因的方法分成三步:1) 确定故障是否可以重复。试着复制产生故障的条件。重复故障通常可以有效地查看故障的特点。2) 使用普通探头或插槽式分析探头把内存总线连接到逻辑分析仪上,以迅速查看:整个DDRII总线的定时关系、百万分之几概率的误码、协议错误和时钟质量。3) 用高速示波器及高带宽探头,在信号的接收端进行参数测量,包括:对于写入内存的数据在SDRAM上进行探测和对于从内存读出的数据在内存控制器上进行探测。

评估内存故障要考虑的因素

在试图重建故障条件时,记住故障的根本原因可能来自未直接连接到内存上的子系统或子应用。局域网接入、子系统上电顺序、进入或退出睡眠模式以及电源周期都是在评估内存故障时需要考虑的重要因素。

在某个特殊的测试或设置条件下隔离问题,可以使问题变的比较容易。例如,在某项测试过程中发生的故障可能会指向软件程序或信号完整性问题,如串扰或码间干扰。对可重复故障,用户可以在故障条件下进行多次测量。

重复故障条件说起来容易,但做起来要难得多。需要考虑的细节包括:

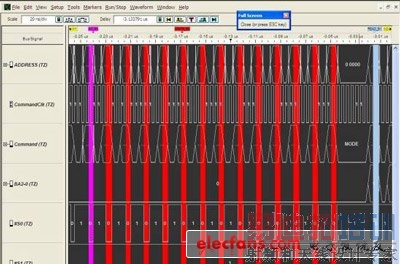

图2:CK0和S0的眼扫描(Eye Scan)。

软件:是否有错误记录?BIOS、操作系统和应用程序是否在测试时运行?

环境:在系统出现故障时室内温度是多少?在故障期间,被测系统的空气流动情况如何?系统供电是否在技术规范之内?

硬件:采用同一设计的其他系统是否已经通过验证测试?其它系统也有故障?还是只有这个系统发生这种故障?故障系统的电路板、DIMM、处理器等是什么版本?故障系统与工作系统有什么区别?制造中最新的元器件有什么变化?

如果条件可以重复,那么在这些条件下进行测试;如果条件不能重复,那么选择最好的内存进行测试,并按顺序改变测试条件(如温度极限和电源极限)。 [p]

用逻辑分析工具缩小问题区域

在调试 DDR系统时,逻辑分析有效地补充了高速示波器的限制。使用DDR探头或插槽分析探头进行逻辑分析,可以迅速查看系统中的问题区域。通过使用逻辑分析工具迅速缩小问题区域,然后使用高性能示波器检查可疑的信号,工程师可以节约大量的时间。

逻辑分析仪系统提供了下列优势:

通过简单的连接,对全部 DDR总线进行64K深的高分辨率定时分析。64k深度信号可以从触发前的100%调节到触发后的100%。

独特的高分辨率眼图,可以识别百万分之几概率的故障信号。

可以从搜索功能中自动设置全局标尺(最多1024个)。

着色滤波功能可以识别轨迹的码型,协助观察内存访问情况。

协议解码转换命令,用于进行功能性验证。

全局标尺可以跟踪波形和列表窗口。

对于使用同一时钟的所有信号,使用眼图测量可以一目了然地查看所有信号。

图1中感兴趣的测量包括:

时钟周期测量。图1中的系统是DDRII_400,时钟周期是5ns。

使用标尺测量数据有效窗口,或使用鼠标在轨迹上移动,确定转换宽度的分布情况。

从有效命令(指令时钟 (CK0)的上升沿,其中CS低,位于WRITE/ READ命令期间)到数据脉冲期间第一个数据选通的上升沿,测得的RAS/CAS等待时间。

从有效激活(指令时钟的上升沿,S0 = 0,其中命令 = Activate)到有效WRITE/CAS测得的RAS/CAS时延。

刷新速率。

预充电间隔。

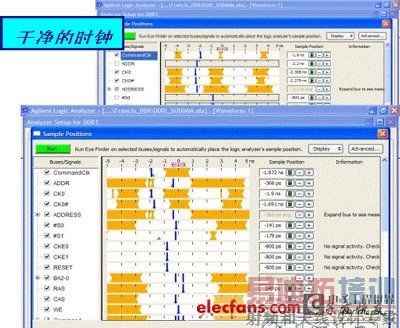

图3:着色滤波器使工程师能够迅速识别表明内存访问问题的码型。

在图1中,用标尺标出的明显问题区域中,S0 (片选)偶尔会在CK0 (指令时钟)上升沿的250ps范围内启动。

这可能要超出DDRII 400 建立/保持时间(Ts/Th)》600ps的指标。为正确检验建立时间和保持时间,我们必需使用高速示波器和探头探测SDRAM上的CK0/CK0#和片选。如果Ts/Th对任何信号处于边际状态,那么它可能会导致间歇性的或持续的内存故障。

在我们连接示波器探头,检定S0的Tsetup /Thold之前,我们可以使用逻辑分析仪上的眼图测量功能,进一步评估边际定时关系。请看图2中所示的眼图:1. CK0是方形波。2. S0是三角形波,构成了与CK0的上升沿有关的眼图。3. S0上升时间慢可能是这个系统中间歇性系统故障的根本原因。边沿慢使得眼图变差,减少了建立时间(Tsetup)。4. 从百万分之几概率的故障信号中识别潜在问题。百万分之几的故障信号会在眼图内部显示为绿色的斑点。在本例中,没有证据表明存在故障信号。边沿慢是主要问题。

图4:逻辑分析仪上的眼测量功能可以一目了然地了解内存总线信号关系。

图2中的系统要求使用示波器,最终确定片选信号的建立时间(Tsetup)。下面使用逻辑分析仪快速查看内存系统的实例将介绍,增加着色滤波的独特方法如何通过码型识别了解内存访问的概貌,从而迅速发现协议错误。 [p]

在实例中逻辑分析仪上设置了着色滤波器,以帮助定位关闭页面超限,在这种情况下,针对一个存储区(Bank)的READ或WRITE命令没有与激活启动存储区的命令同步。着色滤波器设置成为存储区bank0(B0)提供红色阴影,为存储区bank1(B1)提供蓝色阴影。粉红色=B0激活,红色=B读,青绿色=B激活,浅蓝色=B1读。着色滤波使得工程师能够使用码型标识,同时查看波形,识别要求进一步检测的区域。

在图3中,B0激活(粉红色)在一系列B0 READ(红色)命令之间前 。但是,屏幕左边B1读(浅蓝色)之前,没有B1激活(青绿色)。如果B1最后激活没有落在允许的规定时间范围内,则表明发生了问题。

使用逻辑分析仪的最后一个实例,介绍如何使用逻辑分析仪上的眼测量功能。眼图测量工具提供了相对于时钟边沿参考点为0s,从+5ns到-5ns的信号的单一电压门限眼图。

眼图测量一目了然地提供了:时钟占空比、噪声和信号完整性问题、数据有效窗口和眼图闭合和通道间时滞。

眼图测量是校准逻辑分析仪取样位置的最快速的方法。在图4中,上面的屏幕显示了采用干净的差分时钟的DDRII系统上的眼定位(Eye Finder)结果。从眼定位(Eye Finder)结果中,我们注意到:1. 从T=0任一侧同等尺寸的白色区域(眼)中可以看出,指令时钟的占空比是50%。

2. T=0时,指令时钟细长的转换区域 (黄色)表明了干净的时钟边沿。

下面的屏幕是采用非纯净(有噪声)时钟的DDRI系统。我们通过查看Eye Finder结果,发现时钟是不纯净的:1. 指令时钟的转换区域很宽。2. CK0和CK0#取样的单端眼不对称。不对称的眼也可能表明逻辑分析仪门限不正确。

用高速示波器和探头进行测量

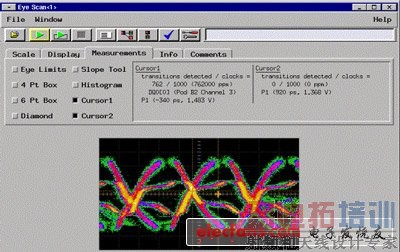

图5:READ和WRITE选通图取决于探测位置。

为确定故障的根本原因,通常要求使用高速示波器和探头进行参数测量。对DDRII测量,使用配有7GHz探头的20Gs/s采样、6GHz带宽的示波器可以为系统特性验证提供精确的测量功能。需要在示波器上测量的参数包括:建立保持时间Ts/Th、上升时间、时钟过冲、频率和抖动分析软件。

探头位置对在信号特性验证中进行精确的参数测量至关重要。最重要的是:1. 在内存控制器上探测READ数据和选通;2. 在 SDRAM上探测WRITE数据和选通。图5是T=0时相对于DQS5上升沿和下降沿的逻辑分析仪眼扫描(Eye Scan)测量结果。测量结果是在DIMM插槽中使用插槽分析探头获得的。

在图5中,WRITE选通的眼图很大,形状很好。插槽分析探头上的探头位置与SDRAM足够近,因此信号中没有反射。插槽分析探头上的反射使READ选通劣化。眼图足以对选通偏移和脉宽进行相对测量。但是,总线上的位置不足以实际检定READ业务的特征。

图5还说明了探头位置的重要性,因为在插槽分析探头上查看时,READ信号的幅度失真,与内存控制器上的实际眼图几乎没有类似之处。为精确地查看内存控制器看到的READ数据,示波器探头必需放在内存控制器上。微型探头前端使这一任务成为可能。许多技术领导者使用本文中介绍的工具和技术,来验证和调试高速内存系统。许多工程师已经采用节约时间的工具,他们可以更快地调试及更好地查看系统性能。

上一篇:泰克推出第一个基于网络的实验室仪器管理解决方案

下一篇:是德科技MultiScope应用软件支持40通道的高速多链路系统测试