- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高精度便捷式全数字示波器设计

示波器是一种用途十分广泛的电子测量仪器。电子技术的日新月异,使各类电信号越来越复杂,在工程应用中对信号实时采样率和波形捕获率也有较高的要求,数字示波器成了各个岗位的硬件开发和测试人员必不可少的工具。针对当前柔性工业测量系统的需要,本文给出DSP+CPLD的方案,实现了一种高精度、高集成的便捷式数字化存储示波器的设计,系统尽可能地采用数字集成电路,结构简单,测量结果可靠性高,具有友好的人机界面,同时具有高采样率、高分辨率及低误差等特点。

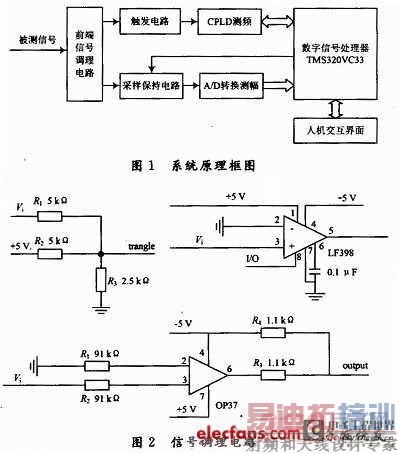

1 系统设计方案

该数字示波器主要由测量控制和显示输出两部分组成。输入信号在测量电路前端,经由信号变换电路处理成各次级单元能处理的等效信号,主要是由比较电路处理输出正方波和峰-峰值为2.5 V的等效运算放大输出信号。方波信号作为记数脉冲,触发可编程逻辑器件CPLD来实现频率值的测量。同时,经运算放大器输出的信号输入至采样保持器,由主控制器DSP向其相关引脚发出锁存信号来实现对待测信号的采样和锁存输出的功能切换。

当控制端置“1”时为锁存输出,这时,输出的信号可供A/D转换器件进行数据采集;置“0”时实现对信号的采集。A/D采集回来的数据送给DSP,再由DSP先把外部数据存储在外部存储器中,然后进行分析,最后,把经过处理的数据通过RS 422标准接口以数据包的形式发送给液晶显示器显示输出。系统原理框图如图1所示。

系统硬件部分由信号输入变换电路、采样保持电路、主控制电路、智能终端设备等部分组成。

2.1 信号输入变换及采样保持电路

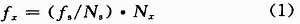

信号输入变换电路主要用于实现信号的等效变换。设计中采用高速的OP37进行信号变换、采样保持,是数据采集系统的重要部件,对信号起隔离缓冲作用。如果要对变化速度高的模拟信号进行A/D转化,转换精度要求比较高,为了防止A/D转换过程中信号发生变化,就必须采用S/H电路。S/H电路和A/D配合,可以消除A/D的输出脉动,并通过MUX实现多路采样控制。

在这里采用高性能单片采样/保持器LF398,具有很高的直流精度、很快的采样时间和很低的下降速度,器件的动态性能和保持性能可通过合适的外接保持电容达到最佳。信号调理电路如图2所示。

2.2 测频电路

示波器对信号的测频是根据等精度频率计的原理设计的。由可编程逻辑器件EPF10K50V完成,100 MHz的标准频率信号直接进入EPF10K50 V。器件采用信号输入变换电路输出的方波脉冲作为计数器的时钟输入信号,用标准的100 MHz进行记数,最后算出输入信号的频率。

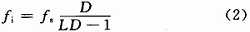

通过图形法和VHDL语言对EPF10K50V编程,本设计中,CPLD完成对信号频率的测量。频率测量原理如下:在单位测量时间Tp中被测信号计数值为Nx,对标准信号的计数值为Ns,在已知标准频率fs的基础上,被测信号频率值fx满足:

2.3 幅度信号采集

为了满足对高频率信号的采集,选用ADI公司推出的AD7667来实现对被测信号的幅值测量。AD7667是16位A/D转换芯片,内部2.5 V参考电压,工作范围为0~2.5 V,LSB小于±2 b,转换速率为800 Kb/s,转换时间小于1μs,采用单+5 V电源供电。由信号变换电路把被测信号转化成工作范围内的有效值,进行精确测量。

2.4 人机交互部分设计

示波器的显示及指令输入由智能终端设备LJD-ZN-3200K来实现。LJD-ZN-3200K是集输入、输出为一体的智能图形化界面输出设备分辨率为640×480,能满足系统设计的要求。该设备终端通过串行接口与主控制器通信,完成数据传输。

将设计好的图形界面加载到智能终端存储单元,然后按设定对坐标值进行识别,即可实现触摸式控制输入。示波器共有9个功能键,分别为:3个垂直区分度选择按钮,用于垂直灵敏度选择;3个水平区分度选择按钮,用于水平扫描速度选择;采样方式切换按钮,用于选择实时采样和等效采样;波形存储按钮和波形调出按钮,用于当前的波形采集存储及调出;单次触发按钮,能对满足触发条件的信号进行单次采集与存储。

3 信号采集及处理分析

3.1 信号采集原理

对不同的频率信号进行测量时选取合理的采样手段将直接影响系统的测量精度,在数字信号分析技术中,常用的信号采样方法有两种:实时采样和等效采样。

实时采样(Real Sampling)通常是等时间间隔的,其最高采样频率是奈奎斯特极限频率,特点是,取样一个波形所得脉冲序列的持续时间等于输入信号实际经历的时间,所以取样信号的频谱比原信号还要宽。在本设计中采用A/D转换器件频率为400 kHz,根据采样特性可计算出该数字示波器能对不大于50 MHz的输入信号进行采样输出。

等效采样(Equivalent Sampling)是指针对周期信号的时域重复的特点,在不同的时间段进行多次较低采样率的采样,然后将这些低采样率的样本复合成高采样率的数据样本,从而真实重构出原始信号波形的数据采集方法。它利用信号的周期性,以增加采集时间为代价,降低对高速采样电路的压力,通过重组恢复原始信号。 [p]

本文采用提取等效采样时间采样,它是用信号的重复频率fi与采样率fs的特殊关系,使等效的采样率增加D倍。

首先,适当选取输入信号的重复频率fi,采样D个周期的信号波形,然后把记录的数据通过一个简单的算法重新排列组合,以获得一个完整的输入信号波形,这样等效采样率是实际采样率的D倍。

实际实现时,D的选取取决于所需要的等效采样率fe,使得fe=Dfs即可。而L是单个周期实际采样点的个数,L=int(M/D),M是记录的采样数据的总和。输出信号的重复频率为:

提取等效时间采样的方法可以提高采样率,但要求输入信号的重复频率fi要受到精确度的控制,而等效采样率为Dfs,与输入信号无关,当输入信号的重复频率偏离式(2)中所给的值,等效采样度变最大时间偏差为:

等效于展宽了频带,此时频带的宽度与A/D转换的速度和微处理器的速度几乎无关,用这种方法结合设计的数字示波器,较容易地测量高频信号的频率和幅值。

最后,把采样得到的数据进行存储,然后进行统一的分析,复现出信号的函数曲线,可计算得到幅值。

由于在设计过程当中对电压信号采样分析采用的是等效方式,采集到的是以时间为自变量的离散序列,这些采样数据反映了被测参数的变化过程,但带有一定程度的误差,势必会引起采集数据失真的现象。为了避免非误差允许范围内的值对测量结果造成干扰,采用软件对测量结果进行曲线拟合的方式对数据进行修正,以保证测量结果的相对精度。

3.2 显示分辨率计算

设计的波形显示窗口一共有354x446像元素,能满足设计要求,统一分析采集的数据,采用正弦内插算法进行处理,形成相应的输出,复现被测信号波形。

4 系统软件设计

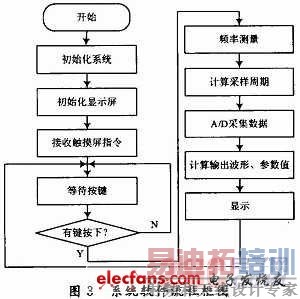

编程逻辑器件CPLD采用硬件描述语言VHDL为底层支撑,用原理图输入的方式来实现系统软件部分的设计。DSP软件编程采用C语言与汇编语言混合编程,程序主体用C语言编写,对于占用处理器时间较多的算法程序和I/O接口操作则采用汇编语言编程,汇编代码可以用C语言可调用的函数或内联代码的形式出现,把C语言和汇编语言的优点有机结合起来。系统软件完成数据收集分析,把采集到的曲线坐标经处理后由RS 422标准接口传输给智能终端,同时也能接收到智能终端的输入信息,执行相应的功能,系统程序流程图如图3所示。

5 测试结果

(1)系统能对10 Hz~20 MHz的任意周期信号进行测量,对大于20 MHz的信号,由于输入信号调理电路器件带宽的限制,导致用于测量输入信号频率的方波失真,致使示波器的测量信号频率精度降低。对相同频率的信号,等效采样方式的波形比实时采样方式的波形要好,其原因是同一个信号周期内前者的采样点比后者的采样点多。

(2)示波器的显示屏刻度垂直方向有354个像元,水平方向有446个像元,显示分辨率较高。

(3)示波器的垂直灵敏度分辨率包含1 V/div,0.1 V/div及2 mV/div三档,对比专用数字示波器测试结果,信号在显示屏上显示明显,波形失真小。

(4)示波器实时采样速率为400 kHz,等效采样速率可达200 MHz。

(5)系统在扫描速度包含了20 ms/div,2 μs/div及100 ns/div三档。

(6)系统具有存储和调出显示信号波形的功能。

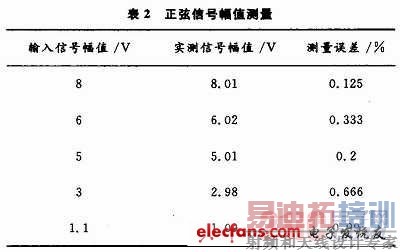

用所设计的示波器,分别对多种信号的不同频率、幅值进行测试,同时对比高精度数字示波器测量结果,具体测试数据如表所示。

6 结语

样机测量结果表明,系统频率测量误差小于0.05%,信号幅值测量误差小于1%,系统精度较高,能满足一般的工业要求,并且可以在显示模块上对被测信号进行很好的复现。系统重量小于0.5 kg,体积为:20 cm×15 cm×10 cm。

它克服了同类产品使用时操作复杂,精度低的缺点,并且所设计的数字示波器集成度高,工作过程受外界环境的干扰小,测量数据可视化,界面友好,可复现被测信号波形,故可作为一种内嵌式设备,嵌入到一些柔性工业测量系统当中,这在工业自动化领域和测试领域有广泛的应用前景。

上一篇:示波器的选择原则

下一篇:采样率对示波器带宽的影响