- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

M4K块移位寄存器数据读进方式的逻辑分析仪设计

本文以三星的SDR SDRAM(K4S64632)作为存储器,通过FPGA内部的M4K块作为移位寄存器不断的进行读进数据的方式,在不中断程序运行的情况下实现有效数据不间断的读进,设置3种采样模式,结果表明该设计提高了数据的分析范围和质量。

1 逻辑分析仪总体方案

逻辑分析仪包括:数据采样、数据存储、显示控制3大部分。由于Cyclone芯片EP1C3T144C8理想情况下最大频率可达到275 MHz,在实际设计中考虑到其误差,该设计的信号捕获精度定位在100 MHz。最多16路信号捕获输入通道,1路信号触发通道,可调的采样时钟/周期,3种信号采样模式,使用计算机的的显示器作为波形显示屏幕。

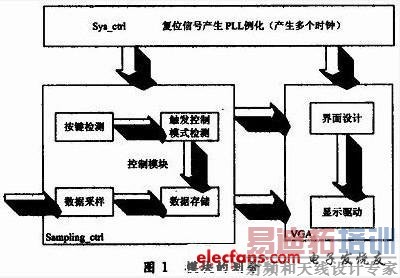

模块整体上是根据数据流的方向划分的,如图1所示。sys_ctrl模块对系统复位信号进行异步复位、同步释放,并且通过Cyclone芯片EP1C3T 144C8内部的PLL例化得到多个稳定可靠的时钟信号。Sampling_ctrl模块包含按键检测、触发控制、数据采样、数据存储等多个功能是采集控制的核心模块。VGA显示模块包含界面设计、字模数据寻址送显方式和显示驱动的时序控制。

2 复位信号产生PPL例化

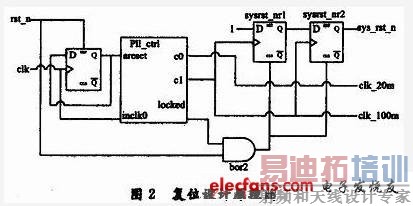

逻辑分析仪的复位设计如图2所示,这个模块设计里,先用FPGA的外部输入时钟clk将FPGA的输入复位信号rat_n异步复位、同步释放处理,然后将复位信号输入PLL,同时clk也输入PLL。在PLL输出时钟有效前,系统的其他部分都保持复位状态。PLL的输出locked信号在PLL有效输出之前一直是低电平,等PLL输出稳定有效之后拉高该信号。FPGA外部输入复位信号rst_n和locked信号相与作为整个系统的复位信号。从PPL输出端得到时钟不仅频率和相位上比较稳定,而且网络延时也相比内部的逻辑产生的分配时钟要小得多。

3 控制模块

通过FPGA内部的M4K块配置移位寄存器不断地读进新的采样值,数据采样回来后先经过SDRAM放入缓存FIFO中,然后把该FIFO中的数据上传到显示器。该模块的时钟是由PLL电路对FPGA输入的25 MHz晶振时钟倍频得到的。通过FPGA外部一组拨码开关控制输入电平为高或者低,从而设置不同的触发和采样模式。

3.1 SDRAM数据存储模块

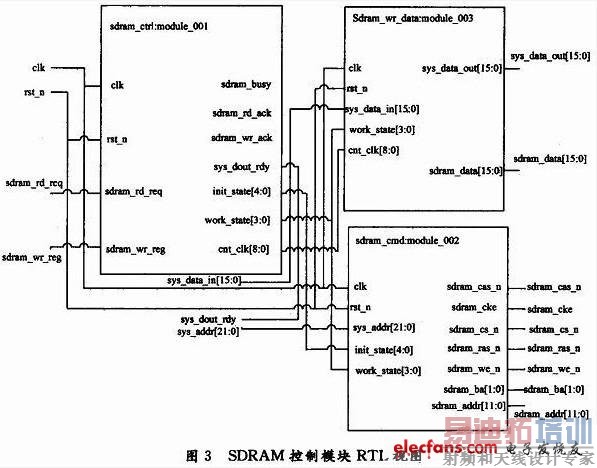

将这个存储模块划分为多个子模块来实现。如图3所示。sdram_ctrl是SDRAM状态控制模块,该模块主要完成SDRAM的上电初始化以及定时刷新、读/写控制等状态的变迁。内部设计了两个状态机,一个用于上电初始化的状态控制,另一个月用于正常工作时的状态控制;sdram _cmd是SDRAM命令模块,该模块根据sdram_ctrl模块的不同状态指示输出相应的SDRAM控制命令和地址,sdram_wr_data是SDRAM数据读/写模块,该模块同样是根据sdram_ctrl模块的状态指示完成SDRAM数据总线的控制,SDRAM的数据读/写都在该模块完成。数据读/写借助了两个存储器(异步FIFO)如图4所示。其中wrfifo用于写SDRAM数据,rdfifo用于读SDRAM数据。在设计中SDRAM读/写都是以8个字(16 b)为单位,使用FIFO中的当前数据量作为操作SDRAM的状态指示。当wrfifo数量超过8个则发出写SD]RAM请求,读出wrfifo中的数据。同样,在rdfifo数据少于256 B(rd-fifo半空)时发出读SDRAM请求,读出8个新的数据写入rdfifo中,以保证后续电路总是持续的传输。SDRAM信号采集模块在上电延时后从SDRAM的0地址开始写入递增数据,随后通过内部FIFO依次送入SDRAM。SDRAM的所有地址写完数据后,启动SDRAM读逻辑,从0地址开始读出SDRAM内的数据放入缓存FIFO中,然后把该FIFO中的数据上传到显示器。

基于M4K的移位寄存器连续且可变频的采样模块#e#3.2 基于M4K的移位寄存器连续且可变频的采样模块

为了实现有效效据的精确捕获在不中断程序运行的情况下,有效数据长时间实时读进,提高嵌入式软件性能分析的范围和质量。利用Cyclone芯片内部M4K结构配置移位寄存器对数据实时采样,并且设置2个按键调节控制采样频率。

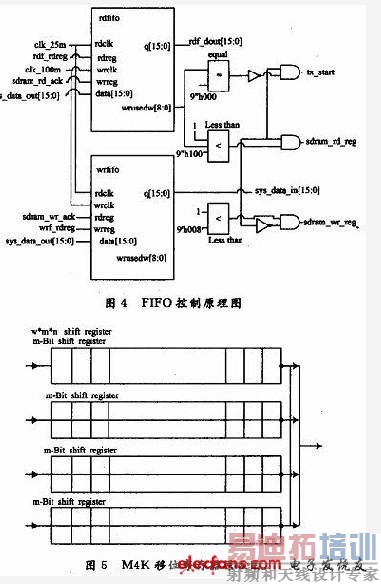

图5为M4K移位寄存器原理图。配置输入/输出的数据位宽w,移位寄存器的一个taps位宽m,总的taps数量n。这三个参数乘积就是占用的M4K存储大小。从图5中可看出,每个clk输入一个移位数据,同时输出一个数据,而M4K内部则是每个clk周期移位一次,每个tap的输出直接移位到下一个tap的输入,配置后的输出中可看到每个tap的最后一个w位宽的数据。

VGA界面设计主要完成对结果的显示。可以对测试对象的数目、采样模式、触发信号的模式、采样频率进行控制,并且将结果显示成为波形图以便使用者进行观察。在设计中需要的字符是通过取模软件PCtoLCD2002,把定义的字模数据存储在FPGA的M4K块生成的ROM里,显示的时候从ROM读数据进行显示。

5 FPGA仿真及调试

实时数据采集分析数据量大,时序复杂,以10 kHz~100 MHz的采样频率进行数据传输时,使用QuartusⅡ自带的仿真工具生成的激励,花费的时间长,而且与实际处理结果有一定的偏差,无法有效的验证整体模块的功能,同时也赡以对其进行实时模拟。本文在使用QuartusⅡ自带仿真工具的基础上,将综合后得到的结果导入Modesim 6.0中,编写Testbench提供仿真激励对逻辑分析仪的顶层模块进行仿真。通过比较整体功能进行验证。图6为逻辑分析仪顶层模块仿真波形。

由图6看出,3种采样模式分别为001,010,100。001采样模式被触发后显示后64个采样数据;010采样模式触发后显示前32个采样数据和后32个采样数据;100采样模式触发后显示前64个采样数据。清除采样信号低有效,开始一个新的采样触发。经过调试,该逻辑分析仪采样频率为100 MHz。在输入采样信号的情况下,能够得到比较不错的波形。图7是在该采样频率下观察到的波形。

6 结语

结果表明,该逻辑分析仪以每8个像素为单元作为一个采样数据的显示长度,最多16路信号捕获输入通道,1路信号触发通道,3种信号采样模式,数据的分析范围和质量得到提高,可方便科研、教学使用。