- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

高速串行总线无源通道建模及校准

吴 均1,陈德恒1,庄哲民2

(1.深圳市一博科技有限公司,广东 深圳518057;2.Cadence深圳分公司,广东 深圳518000)

摘 要: 高速串行总线无源通道建模的效率及准确性,一直是行业关注的重点。Cadence Sigrity的POWER SI 3D-EM工具,实现了效率与精度的较好结合。本论文先从工具的精度出发,采用精度较高的TRL校准模式来进行仿真测试校准,验证仿真结果的准确性。同时考察工具的分布式并行计算能力,看看在保持足够精度的前提下建模效率的提升。

关键词: 高速串行总线;无源通道;建模;TRL校准;分布式并行计算

0 引言

高速串行总线的速率越来越高,从前几年大家关心的10Gbase-KR到现在更高速率的2528G传输,高速串行总线带来的设计挑战也越来越多。

从传输通道来说,挑战主要来自于信号的波长和通道上各元素的物理尺寸越来越接近。

无源通道的性能对高速串行总线的信号传输至关重要,而我们要优化无源通道的性能,就需要能对通道进行准确的建模。而要验证通道建模的准确性,我们就得先对通道进行准确的测试,然后通过仿真测试校准来验证仿真建模的准确性。

1 TRL技术简介

我们可以通过网络分析仪来得到待测物(DUT)的通道特性(S参数)。但如果DUT是非同轴接口的元器件,如PCB板上的一段走线、各种表贴器件等,则需要通过夹具将被测物与网络分析仪的同轴接口进行连接。

图1中,测试的结果是图中所示区域,而我们最终想要得到的数据是真实DUT的数据。从测到的区域数据最终得到DUT的参数,这个过程,我们就叫做去嵌。严格来说,去嵌也是校准的一种,只不过通常的仪器校准,是去掉仪器本身与线缆的影响;而去嵌,则是去掉仪器本身、线缆以及夹具的影响。

去嵌的方法很多,TRL是相对来说精度比较高,也具备一定难度的一种方法,也是行业里面普遍认可的一种方法,可以用来研究走线的细节差异。

1.1 TRL技术及原理简介

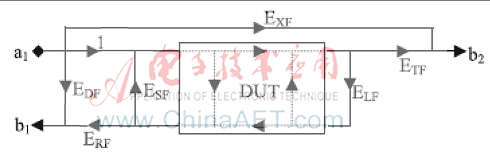

现在的校准技术中,通常是对传输参数、反射参数、隔离参数进行测量,确定一些误差模型,再通过这些模型进行矩阵计算。误差模型如图2所示。

图2 误差模型示意图

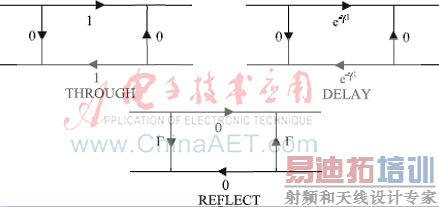

TRL校准方式通过测量2个传输标准件(Thru、Line/match)和一个反射标准件(Reflect)来确定10项误差模型,从而进行校准,并且可以通过load的测量将误差模型增加至12个。使用不同频段的多条延时线来避免了低频与高频不一致所带来的误差,所以在大部分情况下TRL比SOLT的校准效果更好。但由于不同场景下使用的测试夹具不同,所以通常需要根据测试夹具的情况设计相应的TRL校准件。TRL误差模型示意图如图3所示。

图3 TRL误差模型示意图

1.2 测试精度展示

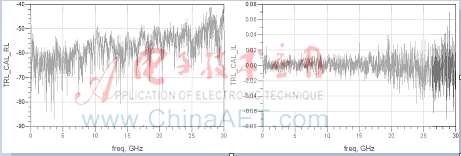

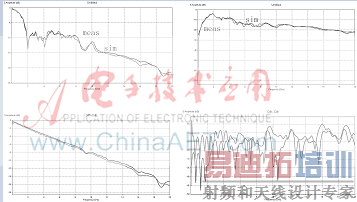

TRL校准的第一个指标就是TRL校准的精度,通过校准完后测量直通校准件来验证。由于夹具已经被去嵌,此时测量直通件的插损应该无限趋近于0,回损应该尽量小。图4为一博科技某款测试板的校准精度。

图4 测试结果示例

可以看到,回损基本小于-50 dB,插损在20 GHz内也小于±0.02 dB,属于较好的校准结果。

2 仿真介绍及仿真测试校准

除了测试的方式,我们还可以通过仿真来取得无源通道的参数,Cadence的Power SI及Power SI 3D-EM就是这样的仿真工具。

2.1 三维场仿真算法简介

2.1.1 FEM算法简介

(1)3D-EM使用有限元算法求解,支持零阶和一阶的有限元网格边界条件。

①零阶:电场在网格各边上保持恒定,在网格内部线性变化。

②一阶:电场在网格各边上线性变化,在网格内部以多阶趋势变化(相同网格条件下,一阶精度比零阶更高)。

(2)支持自适应网格,确保求解收敛性和精度。

(3)使用先进的频率扫描方法,比传统方法求解快一个量级。

(4)典型的有限元求解表达式如下所示:

其中,[A]表示已知的有限元系数矩阵;{E}表示需要求解的电磁场矩阵;{f}标识激励向量。

如上所示,系数矩阵通常可以分成4组随频率变化的参数,如下:

:角频率(angular frequency)

:角频率(angular frequency)

μ:磁导率(permeability)

σ:电导率(conductivity)

Z:表面阻抗(surface impedance)

ε:介电常数(permittivity)

n:表面的外方向法向量(outer normal of a surface)

W:有限元基函数(finite element basis function)

Eport:端口位置添加的激励(port excitation)

2.1.2 自适应网格剖分算法

(1)3D-EM使用自适应网格剖分算法以保证仿真精度和更好的内存利用效率;

(2)自适应网格剖分算法根据上一次的网格结果求解得到的电磁场,对关键区域的网格进行更精细的划分;

(3)迭代直至得到收敛的网格。

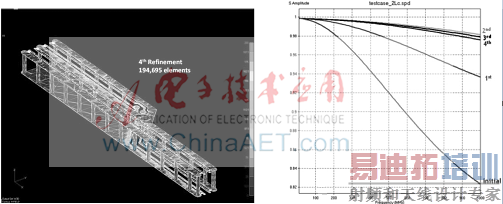

自适应网格剖分次数对插入损耗结果的影响示例如图5所示。

图5 自适应网格剖分次数对插入损耗结果的影响

在这个例子中,自适应网格剖分算法在第3次迭代时,求解频率(1 000 MHz)对应的S参数与前一次网格剖分的结果差异小于设定的收敛判断依据(0.01),到达收敛要求,网格剖分完成。

2.2 仿真测试校准结论

2.2.1 跨分割结构

该结构的难点在与分割区域的谐振对传输性能的影响,以及旁边区域的过孔个数以及分布都会影响回流的分布,从而影响谐振的幅值。结构示意图如图6所示。

图6 跨分割结构示意图

跨分割结构仿真结果如图7所示,这样的仿真结果较为精确。

图7 跨分割结构仿真结果

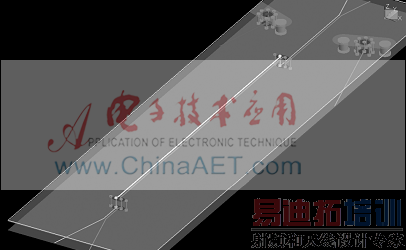

2.2.2 走线与过孔结构

过孔在仿真中天然就是比较难的部分,并且在该模型中有微带线的存在,微带线仿真比带状线仿真更加不容易做准确。该结构示意图如图8所示。

图8 走线与过孔结构示意图

走线与过孔结构仿真结果如图9所示,仿真精度较高,与业界标杆区别不大。

图9 走线与过孔结构仿真结果

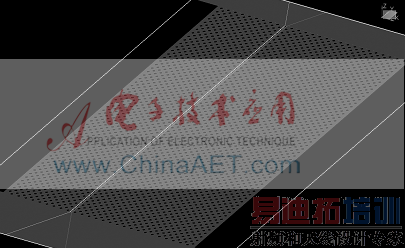

2.2.3 20*20网格铜

由于网格铜的存在,对于信号回流的计算更加复杂,该仿真难度较大。网格铜结构示意图如图10所示。网格铜结构仿真结果如图11所示,可以看到,仿真精度也非常高。

图10 网格铜结构示意图

图11 网格铜结构仿真结果

3 提高仿真效率

仿真除了精度之外,仿真所用的时间与资源也是一个重要的指标。3D-EM提供了cut-and-stitch 流程,可以将一个长链路切分成若干段分别进行求解,再自动合并成一个完整的S参数,而且可以选择每段分别用3D-EM的3D算法或者PowerSI的2.5D算法求解,可以极大的提高仿真效率。

另外,3D-EM还支持多机分布式计算,可以进一步提高仿真效率。本例由于资源限制,没有使用分布式计算。

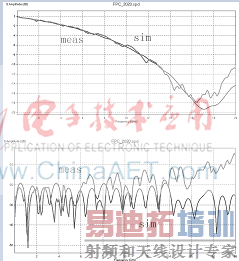

使用cut-and-stitch 流程和直接求解整个链路的仿真结果和仿真效率对比如图12所示。

图12 仿真结果及仿真效率对比

可以看到,使用cut-and-stitch流程仿真结果和整个链路直接求解的精度非常接近,但是仿真时间可以从8个多小时减少到2个小时,如果某几段均匀传输线部分使用2.5D算法求解,总的仿真时间可以进一步减小到35分钟,大大提高了效率。

4 结论

本文得出以下主要结论:

(1)精确的测试才能对设计与仿真提供真正有指导意义的结果。使用TRL校准可以大幅提高测试结果的精度。

(2)精确的仿真可以大大提高设计的效率,使用PowerSI 3D-EM可以得出精确的仿真结果。

(3)3D-EM的cut-and-stitch流程可以大大提高仿真的效率,并且保证结果的精度。

参考文献

[1] 吴均,王辉,周佳永.Cadence印刷电路板设计:Allegro PCB Editor设计指南[M].北京:电子工业出版社,2012.

[2] 钟章民,肖定如,王辉.Cadence高速电路设计:Allegro Sigrity SI/PI/EMI设计指南[M].北京:电子工业出版社,2014.

[3] MORGAN C W.Obtaining accurate device-only S-parameter data to 15-20 GHz using In-Fixture measurement techniques.DESIGNCON 2004.

[4] Liu Di.How to design and verify TRL cal kit also implementation of TRL calibration.

[5] An-Yu Kuo.PowerSI-3DFEM Theory, Accuracy & Performance.

上一篇:多时钟域并行测试控制器的设计

下一篇:一种探测刹车片厚度的方法