- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于NiosII的 形用户接口的设计

随着大规模集成电路技术的不断发展,嵌入式计算机系统开始从MCU逐步过渡到SOC的新阶段。SOPC是一种灵活、高效的SOC解决方案。其集成了处理器、存储器、各种外围设备等系统设计需要的部件,构建成一个可编程的片上系统,设计方式灵活,可裁减、可扩充、可升级,并具备软硬件在系统可编程的功能。

1 系统总体结构设计

系统主要由以下4部分组成:

(1)VGA控制器、SDRAM控制器、SRAM控制器等外设接口的设计。

(2)NIos II软核SOPC系统的配置。

(3)Nios II处理器与外设模块的融合。

(4)GUI函数库的建立。系统主要分为硬件和软件两部分,部分硬件采用DE2上的硬件电路,其中有些电路的控制器采用硬件描述语言生成;软件则采用Nios II编译器书写。

2 VGA时序控制模块设计

由于要实现VGA的实时显示,便需要给VGA一个显存,使得VGA显示的信息能够缓存和切换。出于速度的考虑,显存模块的读写速度要求较高,否则会出现卡壳现象。可采用的存储器分别有Flash,SRAM,SDRAM,其中SRAM的速度较快,可以选用。是一种具有静止存取功能的内存,无需刷新电路即能保存其内部存储的数据,具有较好的存储性能。

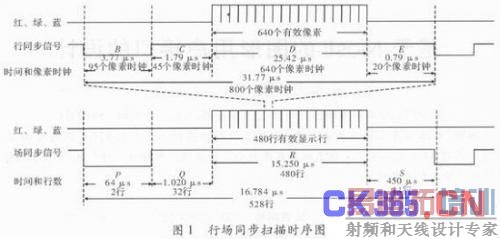

常见的VGA彩色显示器,通常由CRT(阴极射线管)构成。彩色由红、绿、蓝三基色构组成。显示是用逐行扫描的方式解决,一般把要显示的数据存放于存储器单,如果要把存储器里的图像显示在VGA显示器上,以640×480,59.94 Hz(60 Hz)为例。具体行场同步时序要求如图1所示。

根据上述的时序参数以及目标板上的时钟频率,对其行频和场频的时序控制采用点和行计数的方法,场信号和行信号按照时序图设计,当像素或行数达到相应的状态后即改变场信号和行信号的值。系统所需的像素时钟可以用锁相环实现。

3 VGA数据缓存模块设计

数据缓存模块式通过Altera提供的SOPC工具中,Avalon总线上挂的一个SRAM控制器来实现数据的读写功能,Avalon总线与SRAM的接口对用户是透明的。只需编写Avalon主端口模块,用于控制Avalon总线的主端口信号,从而实现数据的读写。Avalon总线同时被2个主外设共同使用,Nios II处理器将需要显示的数据通过主端口写入到SRAM,VGA显示模块通过主端口将数据从SRAM中读出到VGA接口显示器上显示。当系统中存在多个主外设时,SOPC系统会自动进行总线仲裁,产生一个优先级,控制对Avalon总线的使用情况。

当某主外设要发起总线请求时,可能Avalon总线不能马上作出响应而处于等待状态。Nios II处理器将准备显示的数据发送后要求立即存入到存储器中,否则到下一个周期数据将会更新,从而导致数据丢失,此时Avalon总线需将信号设置为等待状态。因此必须将数据暂时存储在缓冲区中,待Avalon总线响应写传输时再将其从缓冲区中读出写入到存储器中。用一个先进先出的FIFO作为缓冲器能够满足以上条件,通过时钟来控制FIFO的写入和读出。

4 结束语

试验结果证明,运行在FPGA中的SOPC系统可以控制VGA显示器,并将VGA成功驱动,而且能够进行画点、画线、画矩形、画圆以及16×16汉字和8×16 ASCII字符混排的显示,同时达到了图像的彩色显示要求。