- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

一种基于SDR SDRAM的视频数据逻辑分析存储器设计

0 引言

在传统硬件调试系统中,通常采用SIGNALTAPII软件进行数据抓取和采集,但是这种调试工具具有一定的弊端,对高速传输的数据中具有某种特征的整段数据需要反复触发抓取,同时很难对采集的数据进行实时观测。音视频数据是一种高速传输的数据,具有数据量大、网络带宽占用量大等特点。要对这种数据进行系统调试,需要系统能够对数据进行实时处理、采集和观测,采用SIGNALTAPII很难实现这一功能。同时,在网络音视频数据传输系统中,接收端除了接收音视频数据外,还会接收到网络中传输的一些控制信息等数据,这些数据对音视频数据的分析无用,应首先进行识别和过滤。

针对音视频数据传输采集分析的要求,本文设计了一种具有新型结构的音视频数据逻辑分析存储器,这种系统能够针对具有TS数据流结构的网络多媒体数据进行实吋的数据结构、数据速率的监控,能够通过程序对网络数据包的帧头、协议号等信息进行分析,监控网络中音视频数据流量,并针对这种结构的数据包进行存储采集,导入SD卡,或在PC平台上进行实时监控、播放或是仿真处理。

1 视频数据逻辑分析存储器的结构和工作原理

音视频数据逻辑分析存储器的结构如图1所示。硬件开发平台接收到的网口测试数据由路由器发出,同时由某一台PC机通过流媒体服务器向硬件开发平台所连接的PC机发送音频和视频数据。流媒体服务器发送的音、视频数据是封装成UDP数据包的TS传输流。此时由MII接口与FPGA进行通信的网络数据协议类型非常丰富,例如TCP、UDP、DNS、NRP、HTTP等。不同网络协议数据包,都具有其特定的数据帧结构。对封装成UDP数据包的TS传输流的数据帧格式进行分析,从而将其过滤出来,实现对音视频数据的提取、监控以及存储功能。UDP/非UDP过滤模块实现TS流的分流和提取,网口数据速率监控模块可以对单位时间的数据量进行实时监控。

音视频数据经FIFO缓存模块、锁存模块后由SDRAM驱动模块将数据高速地写入SDRAM存储器中,SDRAM驱动模块、SDRAM接口模块、SDRAM控制器完成数据的读写、缓存和封装。经过一段时间后,根据UDP帧长度缓存模块的输出值将输出数据打包成帧,转存至SD card中,可保存、携带或将SD card中的数据导入PC平台,对采集到的数据进行各种分析、仿真操作。

2 视频数据逻辑分析存储器可编程模块的设计

2.1 可编程模块的结构和工作原理

可编程模块包括:UDP/非UDP过滤模块、双网口异步传输模块、网口速率监控模块、输入/输出FIFO缓存模块、SDRAM驱动模块、SDRAM接口模块、SDRAM控制器、数据帧封装模块等。在可编程模块的设计中,SDRAM控制器、输入/输出FIFO模块、SDRAM驱动模块、SDRAM接口模块是整个系统的核心处理模块,该部分采用分层状态机的设计模式,实现主状态机与具体操作控制状态机的分离,能有效提高读写操作效率,模块设计结构清晰,提高了系统设计的可读性,也使程序具有更高的通用性。

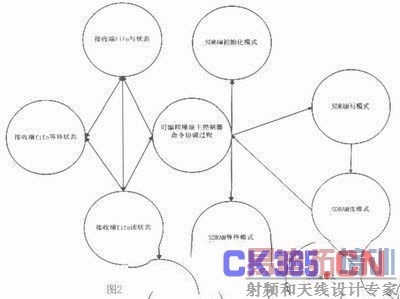

SDRAM控制器、输入/输出FIFO缓存模块、SDRAM驱动模块、SDRAM接口模块等核心模块的设计原理如图2所示。

在系统上电后,SDRAM控制器模块首先跳转至初始化进程,对SDRAM发出初始化命令,分别对SDRAM的各种参数进行配置。初始化完毕后,SDRAM驱动模块开始进行状态跳转判定,判定结果将使SDRAM控制器由开始的空闲状态跳转至其他工作状态。在控制器第一次进入写状态时,SDRAM驱动模块对SDRAM接口模块发送命令信号,使SDRAM接口模块的工作进程跳转至写进程。进入写进程的SDRAM接口模块向SDRAM控制器发送数据、地址和写命令。SDRAM控制器根据接收到的命令将FIFO中缓存的数据以突发模式写入SDRAM中。SDRAM完成写操作后,SDRAM驱动模块将再一次进行状态跳转判定,如此反复。在整个过程中,SDRAM驱动模块根据判定结果进行状态跳转,并发出不同的命令,SDRAM接口模块根据接收到的命令,相应地进入不同的工作进程。在不同的工作进程中,SDRAM接口模块对SDRAM控制器发送不同的操作命令,从而完成对SDRAM的初始化、读、写、刷新等各种操作。最后将需要分析、存储的数据从输出FIFO中导入SD卡。这一操作由开关模块进行控制。

其中,SDRAM控制器的程序编写是本系统设计的另一个重要的部分,SDRAM控制器主要包括命令监控、命令译码以及数据传递等几部分,SDRAM控制器根据接收到的命令,将数据和地址分别送入相应模块进行处理。

2.2 SDRAM控制器的实现

SDRAM控制器由4个可编程模块组成,分别为命令监控模块、命令译码模块、数据传输模块和时钟模块等,支持1、2、4、8和全页突发等突发模式。

首先需要对SDRAM进行初始化,系统的时钟和电源稳定后,在发起读、写、预充电、刷新等命令前,需要100 μs的上电延时。从100 μs内某点开始到100μs结束的过程中,需要发出至少一次NOP或是COMMAND INHIBIT命令。在系统上电结束后,发出PRECHARGE命令,对SDRAM中的所有bank进行预充电,使其至于空闲状态中。在完成SDRAM初始化过程中,还需要接口模块对SDRAM控制器里面的配置存储器进行编码,本设计中写入配置寄存器中的值为0x33,表明SDRAM采用8bit突发读写模式。

SDRAM存储器初始化完成后,SDRAM中的所有bank处于空闲状态。根据系统需求,SDRAM驱动模块向SDRAM控制器发送读、写、刷新等命令。根据命令的优先级进行判断,优先处理哪一个命令,正在执行的命令优先级最高,其次为刷新命令,再次为其他命令,这种命令优先级的机制能够有效提高SDRAM的工作效率。

SDRAM进行的主要操作为读写操作,本系统设计中SDRAM采用的是非全页的8bit突发读写模式,数据宽度是16bit,由于接收的数据为网口数据,仅使用其中的4bit宽度,这是由网口数据线宽度决定的。系统中,接收FIFO接收的数据深度由SDRAM接口模块写入,当接收FIFO接收到规定数值的写入数据后,SDRAM接口模块向SDRAM控制器发出写命令,命令监控模块接收命令和地址,并将接收到的命令进行译码。命令译码模块从命令监控模块获得写地址和译码后的命令,并将其变为适合SDRAM接收的命令。数据传输模块负责数据传输路径和写入。

当SDRAM存储器中的数据大于等于8个时,控制器跳转至读进程,与写进程相似,命令监控模块获得读命令和地址,将命令进行译码,传输给命令译码模块,译码为适合SDRAM的命令,SDRAM将数据从接收地址处开始读出,以8bit突发读的形式将数据打入输出FIFO中。

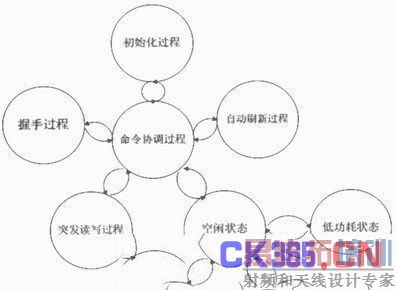

SDRAM开始工作后在不同的工作状态和过程中进行跳转,这些工作状态和过程主要包括空闲状态、初始化过程、读过程、写过程、刷新过程等,状态或过程的跳转通过命令协调过程完成,SDRAM工作状态转移如图3所示。需要注意的是,如果SDRAM设置为自动刷新模式,由于刷新命令的优先级在读写命令之前,SDRAM在状态跳转时会优先跳转至自动刷新过程中。

3 硬件测试结果

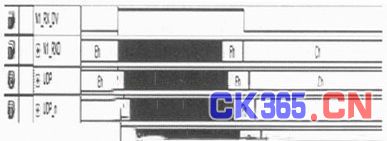

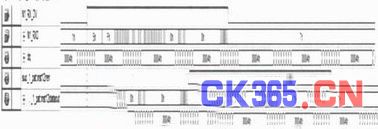

本系统在altera公司的QuartusII平台上搭建完成,硬件上采用了双网口设计,芯片型号为DP83848,SDR SDRAM芯片为Micron半导体公司生产的MT48LC16M16A2,FPGA芯片为CycloneIII系列的EP3C120F484C8,采用Modelsim SE 10.1a完成前期软件仿真,在QurtusII自带的嵌入式逻辑分析仪完成硬件仿真。测试结果仿真波形图如图4、5所示。

N1_RXD为网口接收数据,经过系统对数据包的判定,该数据包是具有TS流帧结构的音视频数据,UDP模块输出UDP数据与输入数据完全一致,而非UDP模块输出为0,实现了音视频数据的过滤和分流。

N1_RXD是整个系统最初网口输入数据,dataout为系统输出数据,dq是SDRAM双向数据总线。由图5可见,系统输出数据与输入数据一致,符合设计要求。其中输出数据最后将导入SD卡,或直接在PC平台上进行各类仿真处理。

4 结论

系统硬件测试结果表明,SDRAM突发存储的操作特点能够满足对高速传输的大量音视频数据的采集和实时处理,能够实现系统对音视频数据进行识别过滤、采集、检测以及存储的需求,从而代替SIGNALTAPII完成对采集下来的数据进行观测和调试的功能,可靠性高,符合系统设计的要求。