- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的以太网音频广播系统

1、课题背景:

课题来源:传统的广播系统从传送音频信号到广播点,都须铺设专门的线路且传送的事模拟音频信号,模拟音频信号抗干扰能力弱,长距离的信号传输势必造成信号的衰减,很难保证声音质量。同时为了对广播的方式进行控制,控制信号必须通过另外的控制线来传送,布线复杂,成本高,施工及维修困难。采用互联网技术和音频流技术实现在以太网上以数字化方式传输多路音频信号,使广播点可以连续、实时地收听高品质声音,实现零布线设计。以太网数字音频广播系统定位于公用广播系统,主要应用于车站、机场、码头等广场和学校、大型商场等场合的广播。主要采用以太网络技术,将音频信号以TCP/IP协议形式在以太网上进行传送和接收,解决了传统广播系统存在的音质不佳、易受干扰、维护管理复杂、互动性能差等问题。

需求分析:以太网数字音频广播系统可广泛应用于车站、机场、学校、大厦等场合,具有低失真度、传输距离远、高可靠性、易于安装布线等优点,可实现实时广播、自由点播、多路分区播音,具有广阔的应用前景。以太网作为一种比较成熟的网络已经广泛应用于各个领域,其TCP/IP协议也成为事实上的标准网络协议。传统以PC机为中心的互联网应用现已开始转向以嵌入式为中心。利用FPGA来实现嵌入式系统设计,可以克服定制电路的不足,系统设计更加灵活,易于依不同的需要进行修改。引入软处理器和嵌入式操作系统,并结合使用LwIP协议栈,能够降低系统平台的设计复杂度,可缩短开发周期,提高系统的稳定性和可靠性,软硬件系部分可分离的设计架构,使得对系统进行修改和重构非常方便。

国内外研究现状:以太网数字音频广播系统定位于公用广播系统,主要应用于车站、机场、码头等广场和大厦等场合的广播。主要特点采用当今世界最广泛使用的以太网络技术,将音频信号以TCP/IP协议形式在以太网上进行传送和接收,彻底解决了传统广播系统存在的音质不佳容易受到干扰,维护管理复杂,互动性能差等问题。现有的广播系统可采用多路定向寻址等技术实现对广播节目播出、接收的智能化管理,安装在不同区域的广播终端可以实时接收广播数据,突破了传统广播系统只能对全部区域进行公共广播的局限,并且广播终端可以是移动的(在局域网范围内),并涵盖了传统广播系统的所有功能,包括音乐播放、实时讲话、播送通知和转播电台节目等。以太网广播系统具有良好的可靠性、稳定性、低失真度、易于安装布线等优点,有着广阔的发展及应用前景,目前已广泛应用于校园广播、大型商场及公司内部广播。以太网数字音频广播系统可实现的功能有:多路分区播音、自由点播、实时插播、移动播音,并可实现远程管理及监控。

2、功能描述:

功能:本系统将实时录制的音频文件利用以太网,以UDP传输方式实现实时的信号的发送、接收与播放。

实况音频流服务器:完成模拟语音信号的采集,将模拟信号转换为数字信号,通过以太网上,发送到终端进行接收和播放,满足用户播放实时声音的需求;

基于FPGA的广播终端:实时接收以太网传送的数字音频信号,存储并转发至音频D/A转换器,将所接收到的数字信号解码转换成模拟信号,并输出到音响设备进行播放。

扩展功能:实现多个广播终端的同时工作;广播先前已存储的音频文件数据。

技术指标:实时传输并播放语音信号,可用于远程管理,具有低失真度,高可靠性的特征。

3、总体设计:

以太网数字音频广播系统分为两个部分:音频数据采集发送端和音频数据接收播放端,通过以太网发送实时语音信号实现远端实时接收和播放功能。

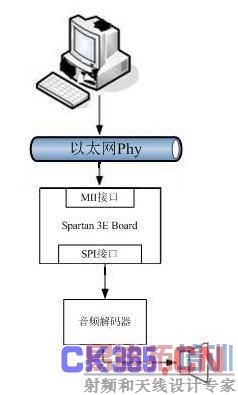

系统硬件结构框架:

图1以太网音频广播系统框图

数据流程:

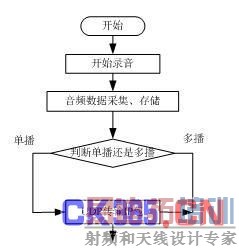

图2音频数据采集与发送模块数据流程图

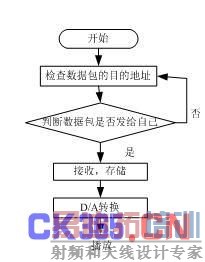

图3音频数据接收与播放模块流程图

各模块功能:

①音频数据采集与发送模块:通过编程实现语音信号的采集、存储,根据接收端的IP地址,将语音信号压缩成广播包以UDP传输方式发送出去。

②音频数据接收与播放模块:由Spartan3E FPGA开发板接收以太网传来的IP包,进行存储,转发到音频D/A转换器进行解码,送交音响设备播放。

4、方案论证:

设计思想:采用FGPA模块接收以太网传来的数字语音信号,并进行存储,再通过音频D/A转换器将数字信号转换为模拟信号在音响设备上进行播放。分为两个部分实现:语音信号采集与发送部分和信号接收与播放部分。①语音信号采集模块(编程实现)在PC机上进行,然后采用UDP传输方式以IP广播包方式通过以太网发送出去。②接收端是在FPGA开发板上实现语音数据包的接收,并将数据处理后送给音频解码芯片进行解码,转换成模拟信号进行播放。

方案论证:本系统采用服务器端和广播终端的架构,由音频流服务器采集、处理语音信号,通过以太网进行传输,然后由Spartan 3E作为广播终端来接收以太网传输的数据,并进行D/A转换处理后输送到播放设备。

服务器端的设计:服务器端在PC机上实现,主要完成语音数据的采集、存储和发送。其中,语音数据的采集和存储采用WAVE音频函数来实现。使用WAVE低级音频函数,可直接与音频驱动程序交互,通过窗口消息或回调函数来管理音频数据块的录入和存储,并提供了一个设备无关接口。在使用音频设备之前,必须打开设备驱动程序,确定系统音频设备的能力,用完之后必须关闭音频设备。具体流程如下:

①查询设备数目。使用waveInGetNumDevs函数来获取波形输入设备的个数。只有确定设备存在,才能打开、使用设备。

②打开波形输入设备。使用waveInOpen函数,该函数打开与指定设备ID相关联的设备,并以给出指定内存句柄的方法放回打开波形设备的句柄。需要在waveInOpen中指定的一个回调函数或者线程,其作用是在一个数据缓冲区被录满后被调用,以对这些数据进行处理,和其他一些相关的操作。

③准备音频数据块。在音频数据录入之前,必须准备好音频数据块。将数据块传送给设备驱动程序就可以开始录音了。使用waveInPerpareHeader函数为输入缓冲区准备头部,使用waveInAddBuffer函数添加一个输入用的数据缓冲区。在用完数据块后,必须用waveInUnprepareHeader函数来清除对音频数据块的准备。

④开始录音。使用waveInStart函数。

⑤停止录音,关闭设备。调用waveInReset和waveInClose函数。结束录音时,在waveInClose之前先调用waveInReset,以清除尚在等待录音的缓冲区。

录音过程中,若缓冲区已满,但录音还在继续,为防止语音数据丢失,就需要再加入一个缓冲区进去。考虑到添加缓冲区的处理是有时间延迟的,而音频对时间很敏感,所以要预先设置好至少两个数据缓冲区。当一个缓冲区满时,就调用另外一个,即可保证所录得的音频数据不会有断开的间隔。录制波形音频时如果缓冲区已满,系统将发送MM_WIM_DATA消息给应用程序,程序接收到这个消息后,就可以从消息带回的参数中得到缓冲区的指针,从而读出缓冲区的数据,或对数据进行处理,并且该缓冲区的数据读完后要用waveInAddBuffer函数将缓冲区重新送入设备,循环利用。在本设计中采用两个缓冲区来存放语音数据。

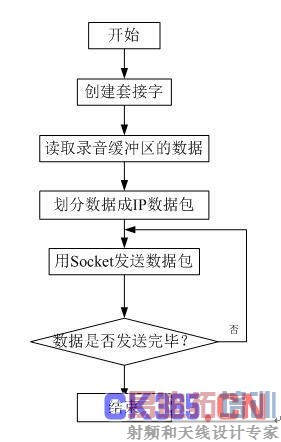

音频数据的发送:数据发送采用MFC的CSocket类来实现。CSocket类是由CAsyncSocket类继承而来,与CSocketFile类和CArchive类一起工作来发送和接收数据。软件实现:当数据缓冲区满时,需要将已采集到的语音数据通过以太网发送出去,这就要用到Socket网络传输。利用CSocket类创建一个套接字,然后将录音缓冲区中采集到的语音数据依次封装成IP包进行发送。语音数据发送流程图如图4所示:

图4 数据发送流程图

要实现语音信号的实时播放,必须对语音信号进行实时传输,所以在以太网上传输数据采用UDP传输方式。虽然TCP提供一种面向连接的、可靠的字节流服务,可以实现数据的可靠传输与出错重传,但是这也导致了TCP协议对资源的占用更多。TCP主要适用于对数据的完整性要求很高的网络传输的应用。UDP不一定提供可靠的数据传输,它只是把应用程序传给IP层的数据报发送出去,并不保证它们能到达目的地。由于UDP在传输数据报之前不用在客户和服务器之间建立连接,没有超时重发机制,所以传输速度很快。当某个程序的目标是尽快地传输尽可能多的信息,强调传输性能而不是传输的完整性时,如音频和多媒体应用,UDP是最好的选择。

录音缓冲区的大小为1024个字节,这样才能避免语音信号丢失,但是在系统终端对语音数据包进行处理的时候,如果数据包过大,则产生严重的噪音,因此系统终端要求接收到的语音数据IP包不能过大,设计中终端处理IP包的大小为128个字节,这样当服务器端录音缓冲区满时,需要对数据进行分割,封装成IP数据包,然后再发送。这里要采用广播地址。在局域网内实现广播,只需将IP地址中主机部分设为全1,本设计中IP广播地址设为192.168.1.255。

广播系统可以有多个广播终端,既可实现全区域的广播,还可以实现局域广播,即对指定的终端进行广播。要实现对指定的终端的广播,服务器端必须知道各个终端的IP地址,然后才能实施对应的广播。考虑到终端数量不多而且是在相对固定的局域网中,采用静态IP地址分配,其特点是IP地址对每一台计算机都是固定的。可以将各个终端的IP地址写入一个配置文档,如:“IPADDR.txt”。服务器首先读取配置文档中的IP地址,将终端IP地址与服务器端的终端号进行绑定,然后每次选定广播终端时也得到了对应终端的IP地址,即可实现区域广播了。另一方面,也必须使终端能够判断出所接收到的IP包是不是发给自己的。是则存储并转发给音频解码器;不是则丢弃。可以在IP包头进行设置,广播终端根据IP数据包包头来判断数据是否发给自己。IP数据包采用广播包的形式进行数据传输。

可以将广播的内容保存下来以便在以后可以使用。本设计对每次广播的内容进行了存储,存储文件设置为Record.wav。每次录音缓冲区满时,即将IP广播包发送出去,同时对其进行存储,在文件末尾将数据写入文件,并改变文件的长度。

广播终端的设计:要实现FPGA与以太网的通信,可以将FPGA终端设计为一个嵌入式系统,即采用基于FPGA的嵌入式系统实现以太网的互联。可以利用Xilinx的MicroBlaze微处理器软核和相应的外设,通过Xilinx EDK搭建系统所需的软硬件平台,完成嵌入式系统的设计。FPGA控制着以太网物理层的操作,内置一个符合MII标准的以太网控制器MAC,FPGA通过MII连接到开发板上的LAN83C185 Ethernet PHY,以便和以太网进行通信,接收以太网发送给本终端的IP数据包,进行存储,并转发给音频解码芯片进行播放。

硬件部分:

硬件电路结构分为两个部分,基于Spartan 3E开发板的音频数据接收模块和音频解码模块。

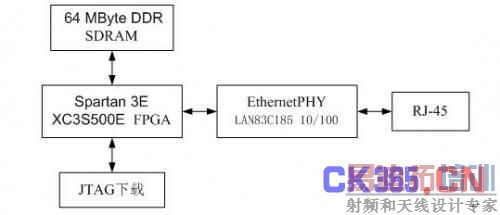

Xilinx Spartan 3E开发板上的XC3S500E FPGA作为控制芯片,在EDK中配置MicroBlaze微处理软核作为CPU,配置FPGA内置Ethernet MAC IP核(MAC是EDK开发平台的一部分),外部存储器采用DDR SDRAM,采用Xilkernel嵌入式操作系统和LwIP协议栈,构建一个完整的嵌入式系统实现以太网互联。

硬件结构图如图5所示:

图5 硬件结构图

MicroBlaze微处理器软核是可嵌入在FPGA中的RISC处理器软核,采用哈佛结构的32位指令和数据总线,具有运行速度快、占用资源少、可配置性强等优点,支持CoreConnect总线,和其他外设一起可以完成可编程片上系统的设计。特征:32个32位通用寄存器和2个专用寄存器;32位指令系统,支持3个操作数和2种寻址方式;分离的32位指令与数据总线,符合IBM的OPB总线规范;通过本地存储器总线(LMB)直接访问片内块存储器;具有高速的指令和数据缓存(cache),三级流水线结构;具有硬件调试模块;带8个输入输出快速链路接口。

EDK开发流程:

EDK:所有的系统设计包括后面的应用程序开发设计均在嵌入式开发套件软件EDK内完成。EDK(Embedded Development Kit)是针对FPGA内部32位嵌入式处理器开发而推出的开发套件,EDK工具包中集成了硬件平台产生器、软件平台产生器、仿真模型生成器、软件编译器和软件调试等工具,利用其集成开发环境XPS(Xilinx Platform Studio)可以很方便、快速地完成嵌入式系统开发的整个流程。EDK以IP核的形式提供LMB、OPB总线接口、外部存储控制器、SDRAM控制器、UART中断控制器、定时器及其他一些外围设备接口等资源,利用这些资源可以构建一个完善的嵌入式处理器系统。这些IP核都有相应的设备驱动和应用接口,使用者只需利用相应的函数库,就可以编写自己的应用软件和算法程序。

首先完成系统硬件平台的搭建和相应的驱动配置。在EDK的XPS中先使用基本的系统生成向导BSB,自动生成MicroBlaze系统的基本构架,设置处理器时钟频率为50MHz,总线时钟频率为50MHz,设置片上读写调试模块为调试接口。生成结束时XPS可以自动地生成对硬件进行例化的微处理器硬件规范文件MHS和描述软件系统结构的微处理器软件规范文件MSS以及一些相关的文件,对这两个文件进行修改,以便完成对系统的优化。生成的系统经过综合、布局布线无误后生成bit文件下载到目标开发板上。

系统软件平台:

在硬件系统建立后,利用XPS的集成工具,完成网标的生成核软件的配置,存储器地址映射默认由系统自动生成,自动分配地址。

为了能够更好地管理系统资源,选择Xilinx 精简嵌入式操作系统Xilkernel,它是一种可定制的简单高效系统,能够与用EDK形成的硬件系统紧密结合,并支持可移植操作系统界面POSIX开放结构。Xilkernel系统的设置可以在开发环境EDK中手动设置,需要配置调度原则为SCHED_RR(simple round-robin scheduling),并设置一个静态线程用于初始化要使用的LwIP协议栈。Xilkernel操作系统通过移植LwIP协议栈就可以实现基于Socket的网络通信。LwIP协议栈支持服务器模式和客户机模式,提供RAW和Socket两种API,是目前使用最为广泛的TCP/IP协议栈。本设计中采用Socket API模式,利用Libgen工具对LwIP库进行链接和编译。

在Xilkernel中设置一个静态线程serverThread来初始化LwIP协议栈,即可以使用协议栈提供的功能函数。调用LwIP的线程生成函数sys_thread_new()生成并启动一个线程。在这个线程中设置开发板硬件的MAC地址、网关、IP地址和子网掩码等参数。分配内存空间开发板的网络接口,再将MAC地址、网关、IP地址等信息添加到内存空间,初始化网络接口。

在设置好系统的软件平台后就可以编写各种关于网络传输控制的应用程序了。使用标准C语言进行应用程序开发,编写相应的算法软件,将编写的程序代码利用mb-gcc编译工具,根据系统软件环境,生成.ELF文件,完成系统功能的实现,通过JTAG接口连到目标开发板上,将软件程序下载到系统中进行调试。

程序设计思路:

终端同样需要Socket编程,以接收从以太网传送来的音频数据。为了实现数据的顺序存储与转发,定义一个循环队列来存储接收到的数据。

struct Queue

{ int front; //队首

int rear; //队尾

int count;

char DATA[QueueSize][SIZE];

};

初始化一个Socket,将它与IP地址和端口号绑定,然后开始监听网络,一旦监听到网络上有数据到来,就生成一个线程去处理。先定义一个结构体struct CSTRING,包含目的终端的IP地址,终端通过判断其成员变量,与自己的IP地址进行比较。若有成员变量与自己的IP地址相同,则存储数据包中数据到循环队列中。还需要定义一个接收数据结构体struct RECVBUFFER,来存放所接收到的音频数据,并且struct CSTRING IP作为它的一个成员用于判断目的IP包地址。

struct RECVBUFFER

{ INT32 count;

struct CSTRING IP; //用来判断IP包是不是发给自己的

INT8 recvbuffer[SIZE]; //接收数据缓冲区

}RecvBuffer; //接收数据的结构体

Socket接收函数接收数据到一个数据缓冲区,然后对数据包进行判断,根据IP数据包头判断该包是不是发给自己的,若是,将数据放入循环队列以待转发,否则丢弃。在以太网范围内实现音频广播,终端以太网控制器IP地址要和服务器处在同一个网段内,设置本地IP地址和端口号,并绑定到服务器地址。

广播终端的实现还需要连接一个音频D/A转换器,将开发板上输出的数字音频信号转换为模拟音频信号。在本设计中采用VS1003音频解码器。VS1003是一个单片MP3/WMA/MIDI音频解码器和ADPCM编码器,包含一个高性能、自主产权的低功耗DSP处理器核VS_DSP,工作数据存储器,串行的控制和数据接口,4个常规用途的I/O口,一个UART,一个高品质可变采样率的ADC和立体声DAC,还有一个耳机放大器和地线缓冲器。VS1003通过一个串行口来接收输入的比特流 。数据流程:首先音频数据从SDI接收并解码,若其SCI_AIADDR非零则应用代码从寄存器所指向的地址开始执行;然后数据流是否经过低音/高音增强器,取决于SCI_BASS寄存器;之后数据流向音量控制单元,同时拷贝数据进音频FIFO,锁存住数据,通过音频中断将数据送进采样率变换器和DAC;采样率变换器将所有不同的采样率变为XTALI/2或128次最高可用采样率;过采样的输出被片上的模拟滤波器进行低通滤波;滤波后的信号前往耳机放大器。

VS1003通过一个串行接口来接收输入的比特流,所以要实现VS1003与FPGA的互连,还需要在开发板上模拟实现SPI总线接口。SPI——串行外设接口总线系统是一种同步串行外设接口,允许MCU与各种外设以串行方式进行通信、数据交换。在内部硬件实际上是两个简单的移位寄存器,传输的数据为8位。一般使用4条线:串行时钟线(SCK)、主机输入从机输出数据线(MISO)、主机输出从机输入数据线(MOSI)和低电平有效的从机选择线/SS,即可实现与具有SPI总线接口功能的各种I/O器件进行通信,而扩展并行总线则需要8根数据线、8~16位地址线、2~3位控制线,因此采用SPI总线接口可以简化电路设计,提高设计的可靠性。在本设计中,从器件是vs1003音频解码器,在主器件产生的从器件时能和移位脉冲作用下,才能接收主机传送的数据,其数据传输格式是高位(MSB)在前,低位(LSB)在后。

FGPA为主控芯片,vs1003为从芯片,选择开发板上与FPGA连接的Hirose FX2扩展连接器模拟实现SPI接口,实际上是对SPI时序的模拟。FPGA的I/O口与Hirose FX2扩展连接器相连,双向I/O口都可以驱动或接收信号。选择FX2连接器上的FX2_CLKOUT模拟实现SPI接口的时钟输出线,一个I/O(如FX2_IO1)口模拟实现MOSI数据线,一个I/O(如FX2_IO2)口模拟实现/SS选择线。SPI数据传输模式采用模式0(CPOL=0,CPHA=0)。数据传输流程:首先主控芯片FPGA要使能相应的/SS信号(FX2_IO2,直到数据发送完毕),通知从芯片即VS1003数据传输要开始了;主控芯片产生SPI时钟脉冲,将数据从每个时钟下降沿发送出去,每次发送1bit,从高位开始发送;待数据发送完毕,主控芯片复位/SS信号,SPI传输结束。

系统设计中的难点与重点:

(1)音频信号的采集;

(2)IP广播包的UDP传输;

(3)广播终端对音频信号的接收;

(4)FPGA控制芯片与VS1003解码芯片之间的数据传输。

5、项目预期成果:

实现音频数据的以太网上实时UDP传输,同步播放,支持多个广播终端同时工作,实现网络广播功能。