- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA+DSP的跳频电台传输系统

引言

跳频技术是一种具有高抗干扰性、高抗截获能力的扩频技术。接收系统是跳频通信系统中非常重要的部分,自适应跳频技术、高速跳频技术、信道编码技术、高效调制解调技术成为近年来跳频技术发展的新动态,基于FPGA的跳频通信接收系统研究有很高的应用价值。

跳频电台就是采用了频率跳变来扩展频谱,提高抗干扰能力,在军事通信中得到了广泛的应用。基于FPGA+DSP的跳频电台传输系统的设计方案具有很好的可移植性。无线通信调制解调纷繁复杂,数码率及误码率要求也不尽相同,该传输系统还需要能够自适应地检测跳频电台的时钟信息及同步码,并进行相应的处理,以满足业务速率的接收解调。

本文系统中采用Xilinx公司的VIRTEX5 XC5VSX50T668 FPGA,该芯片具有先进的高性能逻辑架构,包含多种硬IP系统级模块,并且还支持以太网与PCI Exprees端点模块。其中RocketIO GTP收发器的设计运行速度为100 Mb/s~3.75 Gb/s,RocketIO GTX收发器的设计运行速度为150 Mb/s~6.5 Gb/s。

1 系统总体架构

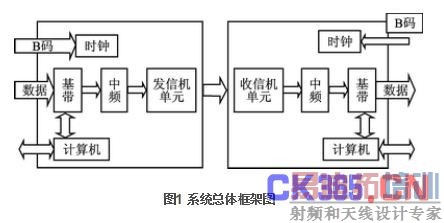

该系统采取半双工形式进行工作,通过 PTT进行收/发切换。高速跳频通信系统可具体化为发送状态模型和接收状态模型。本系统的硬件设备分为两个实体,一个负责发送数据,一个负责接收数据,主要的软件工作在基带板和中频板卡上。系统总体框架图如图1所示。

基带板芯片主要包括FPGA和DSP,处理器间使用RapidIO接口交换数据,中频板主要由FPGA和AD/DA转换芯片组成,基带板和中频板通过高速 SERDES传输信号数据,基带信号经过信道编码、交织、软扩频,然后添加同步头,组成特定的帧格式后,写入FPGA 的发送消息存储区,其结构图如图2所示。

从图2可以看出,在发送端,数据终端或语音终端将数字信息送入基带信号处理器(高速通用FPGA+DSP),然后DSP 对这些数字信息进行基带处理,得到数字化的基带信号并送入FPGA 进行数字中频处理(频谱上搬移过程),用数字化的方法将信号搬移中频上,数字化的中频信号再经过宽带D/A转换器转化为模拟信号,最后经由射频电路将载有信息的电磁波送入自由空间。

当接收信号到达接收端后,经过前端电路的模拟中频信号将通过宽带A/D 转换器转化为数字信号,并送入FPGA 经行中频处理(频谱下搬移过程),FPGA在把解调以后的数字基带信号送入DSP,DSP 在完成接收基带处理以后,将把信息序列送入远端的语音终端或数据终端,这样就完成了一次完整的通信过程。

对于其中的处理器,本课题选用了TI公司的DSP 芯片TMS320C6487TCI和Xilinx公司的FPGA VIRTEX5 XC5VSX50T668作为高速跳频系统实现的硬件架构载体。其中Xilinx公司的Virtex5系列采用第二代 ASMBL(高级硅片组合模块)列式架构,包含5种截然不同的平台(子系列),比此前任何 FPGA系列提供的选择范围都大,它具有运算速度高、使用灵活、功耗低等优点,可以快速地完成数字信号处理中的特殊运算。

2 系统设计

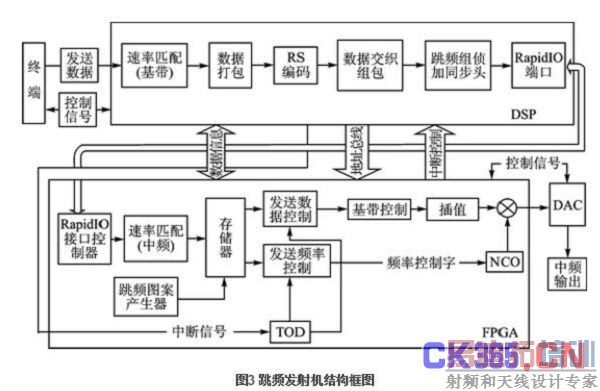

跳频发射机系统包括基带处理部分和中频处理部分,基带处理部分由FPGA和DSP完成,主要处理包括:产生发送消息,进行信道编码、交织,按帧格式进行打包,写入FPGA内部消息存储器,生成跳频图案、跳频数、跳时等参数,写入FPGA内部频率表存储器、跳频数寄存器和跳时寄存器。中频处理部分由FPGA和AD/DA完成,主要处理包括:存储器控制、基带调制、脉冲成形、数字上变频,发送数据控制和跳频控制。为了提高数据的传输速率,处理器之间使用DSP芯片的RapidIO端口进行数据交换,基带板和中频板通过高速SERDES方式转换数据进行传输。

接收机与发射机完全是对偶关系,主要完成的数据处理工作包括:正交数字下变频、解调、解扩、跳频同步等。使用 FPGA+DSP的形式完成基带处理部分和控制部分,主要数据处理任务包括对接收到数据的信道解码和解交织,并完成与FPGA接口的数据转换工作。基带部分还需要完成写入跳频频率表、跳频图案、扩频码表,读出解扩后的数据等,FPGA内部存储器用于与DSP进行数据交换。

2.1 硬件设计

跳频电台传输系统的硬件实现如图3~4所示,主要包括两大部分:发送板和接收板。芯片主要包括:VIRTEX5 XC5VSX50T668、TMS320C6487TCI,D/A芯片AD9788、A/D芯片ADS62C17、McBSP接口控制器、存储器模块。在该系统设计方案中假设信源产生的数据率为9.6 kbps。

发送状态下系统的工作原理:终端通过与跳频通信机之间的串口,对跳频通信机的工作模式等参数进行设置,之后就可以进行信息的发送,信源以9.6 kbps的速率将信息通过RS232异步串口连续把数据送给基带速率匹配单元,该单元将数据每32字节分为一组,以3.686 4 Mbps的传输速率通过SPI同步串口送给RS编码单元进行RS编码,编码采用RS(255,239)的缩短码形式RS(48,32)实现差错控制,累计接收三组RS编码数据后送往交织单元,交织后的数据包为144字节,然后将144字节编码数据进行并/串变换为1 152位/包,并以3.125 Mbps的传输速率,然后在1 152位/包的数据前加8字节数据帧同步头,随后将完整的一帧152字节(共1 216位)以1.98 Mbps的传输速率,通过DSP的RapidIO端口传送给FPGA处理器,FPGA处理器通过同步串口接收中断与缓冲器接收到数据,FPGA中频速率匹配单元将接收的数据按照中频调制器要求的串行时钟主外部帧模式,以32 kbps的帧速率将调制数据送给调制器,进行中频跳频调制。

接收状态下系统的工作原理:接收信号经过中频板FPGA中的解扩器和解调器完成数字解调,将基带32 kb数据以连续的同步串行数据的格式送给DSP。DSP对数据进行同步帧检测并解帧,并以3.125 Mbps的传输速率并行将144字节/包的数据送往解交织器进行解交织,处理后的数据每48字节为一组,以3.125 Mbps的传输速率通过同步并口送给RS译码模块,依次进行RS译码。RS译码得到的32字节/包信息,通过缓冲器以SPI数据模式送给基带速率匹配单元,传输速率为1.562 5 Mbps。基带速率匹配单元将去掉冗余码的数据,再以9.6 kbps的速率送往信宿,至此接收处理过程完成。

2.2 软件设计

为了实现高速跳频通信系统,需要考虑的问题是跳频码的接收同步和跳频帧结构[8]的实现。跳频同步算法[7]的性能主要考虑达到同步所需要的时间和精度,帧结构[9]主要考虑到跳频数据的平衡和发送速率。其中,跳频图案的同步是关键,能否快速、准确地实现跳频图案的同步,直接关系到能否实现数据的正确接收与判决。载波同步由频率合成器的性能来保证,位同步和帧同步与一般的数字通信系统相同。

2.2.1 跳频控制模块的功能

电台开机或由其他工作状态进入跳频工作方式后,首先进行初始化,然后转入搜索状态,一方面检测PTT线是否指示发状态,一方面搜索同步信息。一旦检测到 PTT线是指示发初始同步信息,随即转入正常跳频状态;若接收到同步信息,则也转入正常跳频状态。在正常跳频状态,一方面用户可以进行话音或数据通信;另一方面,若电台处于发送状态,并检测到PTT己经松开,则发完结束信息后转入搜索状态;若电台处于接收状态,并检测到有效的结束信息,则也转入搜索状态。从以上分析可以看出,电台主要有三种工作状态,即发送状态、接收状态和搜索状态,而且跳频电台工作状态设置及其转移具有以下特点:

①同步搜索态是电台的常态,或称稳态,电台开机后,只要是进入跳频,电台无论是发方还是收方,都将首先处于同步搜索状态,迟入网同步也从搜索态开始。

②这是一个闭环同步系统,电台开机后,不需要人工的同步操作,全部自动实现,方便战术使用。

2.2.2 数据帧结构及同步跳

(1) 初始同步信息构成

同步信息分成2组(记为A组、B组);每组同步消息帧包含80位数据,第一组用4个同步频率(f1,f2,f3,f4)传送,第二组用另4个同步频率(f5,f6,f7,f8)传送;其中第1组同步信息(称为A组)重发5次,第2组同步信息(称为B组)重发2次;同时在每组同步信息跳之后,分别在A组和B组同步信息跳之后插入2跳伪同步跳(f9,f10)和(f11,f12)。这样,初始同步跳共发送了32跳。以400跳/s的跳速发送这32跳同步信息,则初始同步时间需要80 ms。A组信息结构如下:

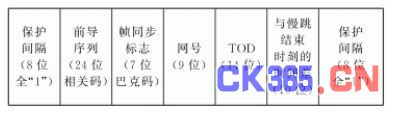

同步信息的构成除TOD低位外还包括前导序列、帧头、网号、与慢跳结束时刻的时间差等,B组同步信息结构如下:

(2) 勤务同步帧结构

在数据跳中,伪随机地插入了勤务跳,迟入网电台可通过搜索这些位于数据跳中的勤务跳来完成入网。勤务跳频的4个频点和初始同步频点一样,根据TOD信息和密钥随机的选出,并且4个频点均匀分布在整个跳频频带内。勤务跳频内的同步信息与初始同步信息结构基本一致,由保护时间、帧同步、网号、TOD组成,帧结构如下:

接收机在1000跳/s的数据接收状态下根据勤务跳的同步信息不断调整本地时钟,以实现跳频的跟踪保持状态。当发射机停止发数后,自动发送8跳结束标志信息,接收机收到结束标志信息后断开基带数据通路,以停止接收数据,并且迅速转入慢跳搜索状态。结束信息在每次松开PTT键后发送。

(3) 数据跳帧结构

数据跳帧格式如下:

由于以9.6 kbps的用户速率传送96字节数据需要80 ms时间,经过Rs编码与交织等处理后,整包数据变为152字节。传送152字节数据,使用1000跳/s的跳速,76个数据跳全部发送完毕。剩余的4 ms时间内插入4个频点的勤务同步跳,共4跳,作为勤务同步和迟入网同步。因此本跳频系统中设计了一个跳频通信周期为80 ms,如表1所列。

一个通信周期为80 ms,每1 ms容纳32个基带位(基带速率为32 kbps)。

发端在按下PTT(Push To Talk)键时先发送一组同步头,用来传送初始同步信息,然后再发送语音信息。初始同步信息由初始同步频率进行发送,根据发送的初始同步信息,初始同步频率分成两组,每组有4个同步频率组成,为了提高同步的抗干扰性能,同步的频率是随着时间的变化而更新的。第一组频率为f1、f2、f3、f4,每隔100 个通信周期换掉一个同步频率,用于传送A组初始同步信息,传送完A组同步信息后插入两跳伪随机跳频(f9,f10)。第二组频率为f5、f6、f7、 f8,也是每隔100个通信周期换掉一个同步频率,用于传送B组初始同步信息,传送完B组同步信息后插入两跳伪随机跳频(f11,f12)。每次按下 PTT键,发送32跳的初始同步信息,其发送格式如图5所示。

正常跳频通信时在语音跳中间加传勤务同步跳,每800跳为一个通信循环,每80跳为一通信周期,每个通信周期传4跳(f1,f2,f3,f4)勤务同步信息发送。

结语

基于FPGA的跳频通信接收系统与常规跳频通信接收系统相比,该系统具有灵活性强、可靠性高、开发周期短和费用低等优点,可广泛应用于通信领域。在测试过程中发现本文设计的系统满足性能要求:4.8kbps以下业务跳频同步时间小于6s,4.8kbps以上业务跳频同步时间小于0.6s。

上一篇:过孔基础知识与差分过孔设计

下一篇:基于单片机的无线环境监控系统设计