- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的大动态数控AGC系统设计

随着软件无线电技术和FPGA、DSP、AD 等技术的高速发展,数字接收机的应用日益广泛。为了扩大数字接收机的ADC 动态范围,广泛采用了自动增益控制(AGC) ,使接收机的增益随着信号的强弱进行调整,其性能的好坏直接影响着接收机能否高质量稳定接收。传统的AGC 电路大都采用模拟电路,但由于模拟AGC 缺乏智能性,难以实现复杂的控制算法,且精度不高,调试复杂。这里介绍了一种基于FPGA 和数控VGA 芯片AD8370 的数字自动增益控制的实现方法,实时地调整中频接收机的增益,大大增强了系统的动态范围。

1 数控AGC 实现方法

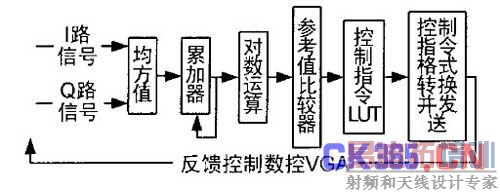

数控AGC 原理框图如图1 所示,在信号数字化后,根据样本估计出信号功率,与参考值比较后,反馈控制前端的数控VGA 芯片,将信号输出调整到ADC 的满量程附近,以获得全程数字量化和最大输出信噪比。

图1 AGC 环路框图

要实现AGC 控制,必须先检测信号幅度或功率的估计值,通过正交I/Q 的均方值即I2+ Q2 精确得到AGC 信号功率,其中I、Q 为同相正交2 支路的符号峰值采样点数据。计算机仿真表明,当信号以每符号4 采样点进行统计平均估计时,得到的估计值与定时恢复无关,即I、Q 值不必为最佳采样点。

由于输入信号的幅度通常是缓慢变化的,故可通过一段时间样值的累加进行一次估计,通常将累加值与参考值相比,得到AGC 需放大或缩小的倍数。在这里,将除法运算改为对数运算后的减法实现,通过与参考值的比较,直接对应需放大或缩小的dB数。再通过查表,转化为数控VGA 芯片的控制字,反馈至前端。这与模拟AGC 相比,由于反馈部分的主要功能由数字方法实现,使得复杂的控制要求用数字信号处理技术能够较容易的实现,且具有快速收敛和精确的稳态响应等优点。

2 计算机仿真

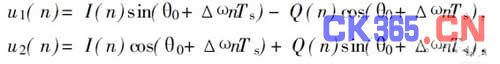

在Matlab 中,首先生成PN 9 的伪随机码作为基带信号。进行格雷码的预差分编码和成型滤波,上变频、加噪、下变频后得到正交和同相2 路基带信号:

式中,△ω为载波频偏,θ0 为载波相位,则:

![]()

仿真中,设置其中信噪比为12 dB,中频为70 MHz,符号率2 Mbps,采样率为64MHz,抽取率为8,信号功率估计时累积长度为1 024 点,即256 个符号。

调整前采样所得的中频信号如图2 所示。其中前4 000 点的信号放大倍数为1,4 001 至9 000 点的信号放大倍数为10,9 000 点之后的放大倍数为20,即信号幅度有2 次变化,需通过AGC 进行调整,使信号幅度保持恒定。图2( a) 为AGC 调整后的中频信号,其中调整的参考值为前4 000点信号的功率,可以看出在4 000和9 000附近信号有一段抖动,这是调整所需的相应时间; 下图为AGC 的放大倍数,同样的,在4 000和9 000点产生了跳变,以响应信号幅度的变化,其中前4 000点的放大倍数为1,4 001至9 000点的放大倍数变为0. 1,而9 000点之后则为0. 05。另外根据仿真结果,信号功率估计值最大偏差小于1 dB,因此,该估计算法和调整控制是准确有效的。

图2 调整前后的信号及放大倍数

3 硬件实现

硬件方案的具体实现如图3 所示。上面为信号处理板卡,下面为中频执行板卡。其中控制板卡上AD 转换由AD9640 芯片完成,输入信号的峰峰值可设置范围为1~ 2 V,本系统初始化为2 V; 控制部分在FPGA XC4VLX100 中完成,以产生时钟、使能和数据三线控制信号; 作为环路执行元件的是前端中频板上的AD8370,其控制功率增益范围为- 11~ + 34 dB; 3 dB带宽为750 MHz; 串行的8 bit 控制信号接口; 提供200Ω差分输入和100Ω差分输出。由于本方案动态范围需达60 dB,故采用了2 级AD8370 级联,为了让系统工作稳定,设计时应使2 级的放大倍数尽量接近,以避免第2 级出现饱和,因此在将调整的倍数转化为AD8370 控制字时,需特别注意。

图3 硬件测试板卡

系统由微波信号源4438C 产生中频70 MHz、比特率4 Mbps 的QPSK 信号,采样时钟64 MHz,由前端中频部分的DDS 产生,系统抽取率仍为8,由DDC后的CIC 完成。

实现中,I、Q 两路的均方值由FPGA 中乘法器DSP48 求取,累加器完成均方值的累加,而累加样本点的个数直接决定了控制调整的相应速度,累加长度太长会使相应速度变慢,无法跟上信号的变化; 但长度太短又会使估计的功率值不准,起伏太大从而引起控制精度的下降,通过实测发现通常数百符号即可得出较准确的信号功率估值,因此对符号率百K 以上量级的信号而言可以在数毫秒甚至更短的时间内完成信号的精确调整。本系统设置为1 ms 进行一次调整,即2 048 个符号得到一次估计值。此外,求对数运算以及信号需调整的倍数到控制字的转换都通过查表实现,其中增益控制字查找表的可实现增益为- 13~ + 60 dB,其深度为4 096,即每1 dB的变化对应56 个步进,可实现最小0. 02 dB的调整,因此结合之前的准确估计一起实现了较高的控制精度。

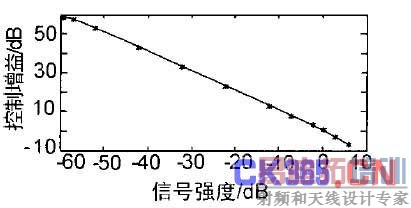

为避免低信噪比情况下AD 长时间工作在溢出状态,系统设置的参考值设计为比AD 满量程小2 dB左右。经测试,当4 dBm 的QPSK 信号直接输入AD 时,AD 采集信号的量化值为# 6 000 左右,距14位满量程对应的# 8 192 约2 dB,故以此功率为参考。如图4 所示,横轴为输入信号功率,纵轴为AGC的增益。理论上2 级AD8370 级联能实现90 dB 的动态,但实测中,在信噪比10 dB 条件下,单级在- 7~ + 28 dB 范围,2 级联合在- 14~ + 56 dB时,其线性性较好,故在本系统中实现了近70 dB的动态范围。

图4 输入信号强度及对应的AGC 增益

4 结束语

首先介绍了数控AGC 的原理,指出AGC 的数字实现方法的优点。在此基础上,对功率检测以及反馈控制方法进行了计算机仿真,结果表明,该方法是可行的,适合FPGA 实现。在硬件实现中,通过2级AD8370 级联实现了近70 dB 的动态范围变化,并保证了控制精度误差小于1 dB。

上一篇:CMMB网络覆盖特点及解决方案

下一篇:基于FPGA的超声诊断仪动态滤波器的设计