- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

DAB单频网适配器研究与设计

在频谱资源和能源日趋紧张的今天, 对频谱和发射功率极大节约的单频网( Single Frequency Network,SFN)技术成为通信领域研究亮点。在数字声音广播( D ig ita lAudio B roadcasting, DAB)领域尤其如此。

目前国内针对DVB 系统MPEG - 2中TS 流的单频网技术相对成熟, 但DAB 单频网设备还依赖欧洲进口, 故在普及单频网通信广播过程中, 研究及开发国内自有DAB单频网产品具有重要意义与价值。

相对传统适配器设计, 本文提出的基于FPGA 平台并结合PC I总线技术来实现SFN时间同步适配器设计方案不仅利用PCI总线广泛适用于PC 的通用性优势, 使得本适配器应用范围更广, 更方便接入DAB 编播网络, 用PC I高速特性使其应用于实时处理, 同时还利用FPGA进行逻辑电路的搭建, 从而降低成本增加系统升级灵活性, 充分发挥其扩展接口的灵活性。

单频网适配设计主要基于ETSIETS 300 799标准的信号群传输接口( ET I, Ensemble Transport Interface)数据流同步原理。总线技术利用A ltera 公司开发的PCI..IP核辅助实现设计。

1 DAB单频网的同步原理

1. 1 DAB 系统结构

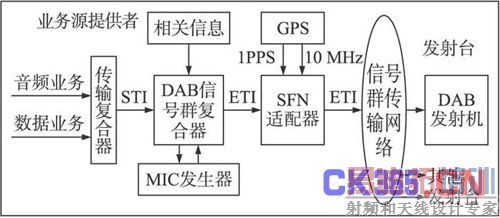

如图1所示, 每个业务源的音频业务数据流和数据业务数据流先于各自的传输复合器中进行复合, 形成STI( Service Transport Interface, 业务传输接口) 数据流。再经DAB 信号群复合器, 插入MC I(Mu ltiplex Configurat ion In fo rmation, 信号群专用信息和产生复合配置信息)。复合器输出并向不同发射台馈送ET I数据流, 速率恒为2. 048 Mbit/ s。信号群传输网络再将ETI数据流分配给DAB 单频网中各发射台。

本文重点在于设计SFN 适配器模块使其将GPS同步秒脉冲和10MH z参考频率转换成同步信息, 加入DAB信号群复用器ET I数据流。

图1 DAB发端系统框图

1. 2 DAB系统的时间同步

1. 2. 1 时间戳信息( TIST)

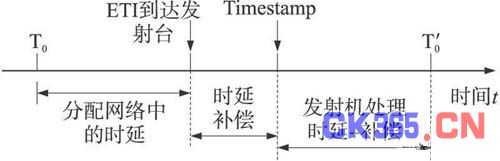

欧洲电信标准协会( ETSI) 发布的标准中定义一个时间戳信息( timestamp, 简写为TIST)用于确定馈送时分配网络中不同路径所需补偿时延。图2中, 对分配网络不同时延的均衡由ET I数据流中TIST的值实现。因发射机处理时延对于每台发射机都是固定值, 故单频网中处理速度最慢的发射机决定了其需要补偿的时延值。

图2 DAB 中TIST与各时延的关系

ETI每个逻辑帧包含产生一个ET I帧所需的数据信息, 它由以下两部分组成:

图3 ETI( L I)帧结构

状态字段( STAT ) 表明传输网络的性能, ETI物理层可能会改变该值;数据区( LIDATA ) 其中的数据信息对任何ETI物理层都是透明的, 在无差错传输中, 其内容不能被其它物理层修改。注意, TIST 包含在LIDATA数据段中。

2 DAB单频网适配器的设计方案

2. 1 方案的硬件设计

2. 1. 1 系统结构

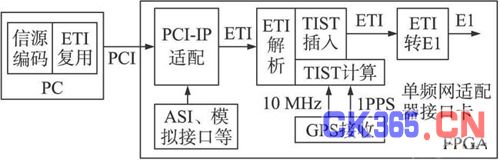

设计单频网适配器接口卡系统结构如图4。

图4 单频网适配器接口卡

接口卡主要功能:

( 1)音频数据在PC 端做信源编码并以ETI帧格式复用, 通过PC I总线传输至板卡实现数据输入。

( 2)使用A ltera的PC I IP核并设计后级接收模块, 在FPGA端实现PCI接口适配, 保证PC I通信顺畅, 本文主要应用IP核的主模式读写功能。

( 3)解析ET I帧头, 并定位协议中时间戳数据。

( 4)根据DAB 同步系统提供的GPS 秒脉冲和参考频率重新计算时间戳的值, 正确插入ET I帧头。

( 5)为符合DAB 系统需求, 使用E1 数据格式向发射机进行馈送, 即对ET I帧进行HDB3单极性编码。且需满足E1格式2. 048MH z的数据率。

2. 2 PC I总线IP核后级接口逻辑设计

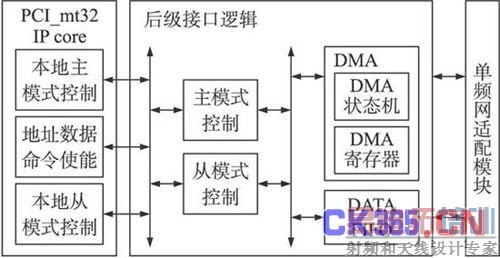

如图5所示, 后级接口逻辑模块主要功能为将IP核与后级通信各信号进行逻辑解释和传输控制。

接收SFN 适配模块传输控制时钟, 为SFN 适配模块提供64 kH z的32 bit数据输出时钟。

图5 后级接口逻辑模块示意图。

本文使用主模式读交易将ETI帧数据从PC 端读入。后级接口逻辑先接收PC 端对DMA 寄存器值的写入, 后申请总线, 获得总线授权后以DMA 状态机控制多次单周期主模式读交易。

2. 2. 1 DMA 寄存器

DMA 寄存器组模块中定义四个寄存器: BCR(字节计数寄存器) , ACR (地址计数寄存器), ISR(中断状态寄存器) , CSR(控制状态寄存器)。在一次DMA 传输发起前, PC 端以从模式写交易方式向CSR、BCR 和ACR 中写入数据, 其中, CSR 记录使能等初始状态信号, BCR 记录本次DMA 传输欲传输字节数, ACR记录本次传输数据目标起始物理地址(即PC 向PC I发送数据中待传数据起始物理地址)。每当一个32 bit双字被传送后(因PC I接口为32位, 故每次传输为32 b i,t 即4 字节相当一个双字) , BCR值减4, ACR值加4, 为其后一个双字数据传送的地址。DMA 控制逻辑在数据传输状态中将始终监控DMA数据传输过程, 当BCR 值减为零时,一次DMA传输结束, 出发中断, 改变中断状态寄存器ISR 值, 计算机在收到中断申请后通过读取ISR值确认中断是否为DMA 传输结束所引起。若确实为DMA 引起, 则可进行下一步处理; 如另一次数据传输: 重新写入CSR, BCR, ACR 值并启动新一次DMA 状态机。另外, 计算机对该模块寄存器访问控制方式为解析地址线上数据判断是否应对DMA 寄存器做读、写操作, 并由读写使能信号配合完成。

2. 2. 2 DMA 状态机

DMA 传输控制状态机如图6所示。

图6 DMA 状态机。

PC配置DMA 寄存器后, DMA 传输控制启动。

若DMA 寄存器有效(即BCR指示有数据等待传输,ACR指示地址有效, ISR和CSR 有效) , 则由后级接口逻辑控制IP核请求总线, 并等待总线, 得到总线传输授权时进行本次传输, 检查各寄存器值。根据条件跳转至传输完成、空闲或寄存器有效状态进行下一次32 bit数据传输。PC I主模式写交易DMA过程仿真波形如图7所示。

图7 DMA数据传输。

2. 3 单频网适配模块逻辑设计

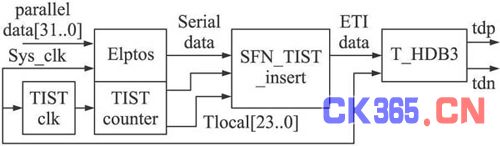

单频网适配FPGA 模块如图8所示。

图中模块实现PC 与板卡间的PC I总线通信。

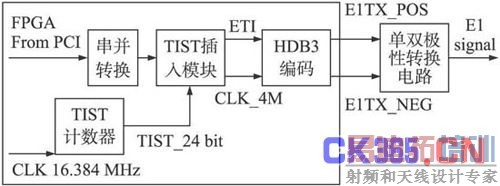

如图, PC I模块接收的ET I数据流经过串并转换, 使总线32 bit位宽数据形成串行码流。T IST插入模块将新生成的T IST 值插入到正确位置, 随后进行HDB3编码, 得到双路单极性码流。数据输出到片外后, 后级采用片外码流合成电路以及BNC 接头输出最终的双极性信号。上图模块分别为E1格式修正的并串转换模块, TIST 计数模块, TIST 计算插入模块, E1格式适配模块。

图8 系统的FPGA 模块构成。

2. 3. 1 时间戳数值的内涵

时间戳信息被携带在持续24 ms的ETI帧中。

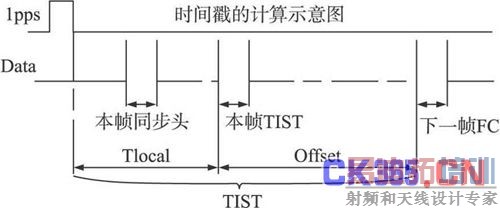

时间戳实际定义相邻下一帧第一个b it的起始时刻相对于参考脉冲的时间差, 即如图9。

图9. 时间戳的计算。

应用层的概念我们可理解为T IST 的值实际表示当前帧的下一帧出现在发射机接收端对等层的时间。即发射机接收端解析的时间戳值表示下一帧帧头出现在N I解析层输出端的时刻。

2. 3. 2 T IST值的计算

T IST值主要涉及标准定义的N I层(即物理适配层的上一层)。T IST 是主要的同步参考值, 也是发射机接收端进行同步发射时, 发射时间点确定需要分析和计算的重要参考指标。其计算如下:

TIST= T loca l+ o ffset+ mostdelay

其中mostdelay 是适配器硬件的处理时延和发送网络时延, 称为最大路径时延。

标准中规定Tloca l为16. 384MH z(时钟二分频)计数器的输出值, 即系统以16. 384MHz做为同步计数参考时钟。本设计采用的32. 768MHz时钟由片外锁相环提供, 与GPS提供的10MH z参考频率同相。

O ffset为帧格式决定的修正值。其计算如下:

offset= *8- ( FL+ 3) × 4 byte

其中FL为ET I(N I层)格式中定义的帧头长度。

最大路径时延(mostdelay)设定需注意, 其值不能超过1 s。T loca l的取值范围0~ F9FFFF16, 加上修正值和最大路径时延后仍然不能超过这一范围, 否则直接将FFFFFF16赋给移位寄存器, 表明新TIST无效。

2. 3. 3 T IST定位并计算状态机

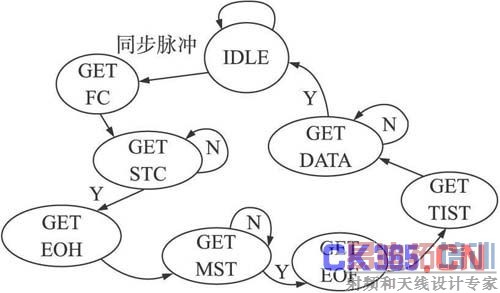

如图10所示, 状态机个状态功能如下:

( 1) IDLE 空闲状态, 等待帧同步脉冲, 捕获则跳转到下个状态开始接收帧;( 2) GET_FC 接收FC 字段, 提取包括NST、帧长( FL)、M ID( DAB 工作模式)等信息, 将表示帧开始的寄存器置1;( 3) GET _STC 传送STC 信息, 长度等于NST的值, 完成后跳转到下个状态;( 4) GET_EOH 判断FC、STC和MNSC 的CRC校验结果, 错误则将err_CRCh置1;( 5) GET _MST 传送MST信息, 长度等于( FL- NST- 1), 完成后跳转到下个状态;( 6) GET_EOF 判别MST的CRC校验结果, 错误则将标志位err_CRC 置1;( 7) GET_T IST 提取时间戳信息, 计算正确的TIST值并重新插入寄存器中;( 8) GET_DATA 传送剩余部分的数据, 完成后状态跳转到IDLE状态。

图10 N I帧同步模块状转移图。

2. 4 E1接口电路设计

我国DAB系统采用E1数据格式标准进行发射机网络数据分配。E1 为欧洲30路脉码调制PCM,其速率为2. 048 Mb it / s。本文中, E1 接口模块将ETI数据流转换成适合E 1线路上传输的HDB3编码信号形式, 其功能实际为实现DAB 分配网络适配。发送接口由FPGA 内部逻辑部分和外围硬件电路两部分组成。如图11所示, FPGA 内部信号为插入TIST新值并经过HDB3 编码后的双路单极性信号。片外经外围转换电路(变压器电路)变换成为单路双极性E1信号馈送入发射机分配网络。

图11 E1发送接口。

3 时间戳插入模块设计与验证

3. 1 T IST 计算插入模块的验证

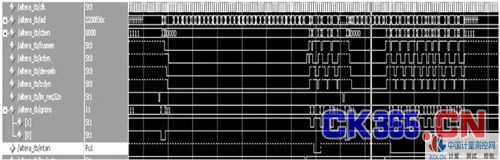

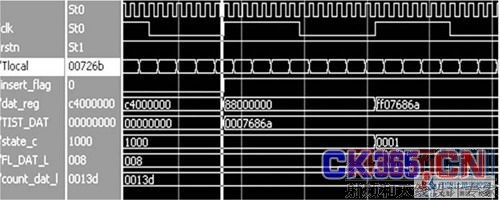

仿真中加入32 b it并行信号输入模块, 按照ETI帧结构进行数据的组织。帧由帧头和数据部分组成。

其中帧数据部分用0循环填充来突出帧头部分的数据处理过程。为避免仿真时因使用1 s的GPS 参考(追求仿真精度为ns级)而导致仿真过程过慢及不必要的浪费, 1 pps生成模块修改为隔125 s产生脉冲来使时间戳计数模块计数器清零。经验证本模块可正确定位T IST 插入正确的值于ETI串行码流中。

Mode lsim 仿真结果如下:

当参考脉冲上升沿到来时本地T IST 计数器清零。该计数器工作为记录当前时刻与秒脉冲之间频率为16. 384MH z的时钟个数。

时间戳的计算和插值仿真结果如图12所示。

图12 时间戳计算和插值。

3. 2 实验结果

验证结果表明时间戳实现正确的插值。完成DAB 的同步适配器功能。本案的设计已完成, 准备投入DAB系统中使用, 做进一步的调试。

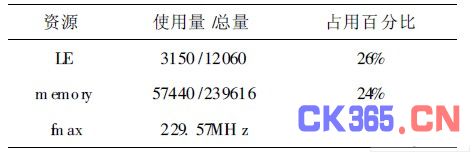

表1 FPGA资源

本设计使用的FPGA 为A ltera公司的Cyc lone系列EP1C12Q240C8, 资源占用及最高主频情况如表1。开发平台为QuartusII 8. 1, MATLAB。仿真平台Mode lS im A ltera 6. 3。编程语言为verilogHDL。

因本方案采用一路E1输出, 即使用2. 048MH z串行数据率, 故时钟33MHz, 位宽32 b it的PC I总线远远满足其并行数据传输率64 kH z的需要。

4 结束语

在DAB 单频网中, 单频网适配器可作为单独设备实现。本文结合DAB 系统中单频网适配器同步原理(主要依据ETSI相关标准)以及PC I总线传输原理, 提出一种DAB 单频网适配器设计方案, 集PCI总线技术, 单频网技术于一身。本文对其中重点设计模块进行着重阐述和正确仿真并给出正确的结果。本文提出的适配器设计方案满足设计需求,测试证明本单频网适配器设计方案切实可行, 并具有很好的实用价值。