- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的带CRC校验的异步串口通信

引言

现场可编程门阵列(field programmable gate array,FPGA)在数字电路设计中已经被广泛使用。这种设计方式可以将以前需要多块集成芯片的电路设计到一块大模块可编程逻辑器件中,大大减少了电路板的尺寸,增强了系统的可靠性和设计的灵活性。本文详细介绍了已在实际项目中应用的基于FPGA的串口通信设计。硬件描述语言(hardware description language,HDL)是一种用形式化方法来描述数字电路和设计数字逻辑系统的语言。数字逻辑电路设计者可以利用这种语言来描述自己的设计思想,然后利用电子设计自化(EDA)工具进行仿真,再自动综合到门级电路,然后用ASIC或Soft-Core实现其功能。Verilog HDL是硬件描述语言的一种,用于数字电子系统设计。串口通信是指在一个时间内传输1位数字数据。从19世纪的二进位电报编码,发展到现在的RS 232(EIA 232),主要用于连接终端和大型主机。串口通信在过去的40年里,大大推动了通信技术的发展。通信协议是指通信双方的一种约定。约定包括对数据格式、同步方式、传送速度、传送步骤、检纠错方式以及控制字符定义等问题做出统一规定,通信双方必须共同遵守。因此,也叫通信控制规程,或称传输控制规程,它属于 ISO’sOSI七层

参考模型中的数据链路层,其主要完成的作用如下:

(1)实现数据格式化;

(2)进行串/并转换;

(3)控制数据传输速率;

(4)进行错误检测;

(5)进行TTL与EIA电平转换;

(6)提供EIA-RS 232C接口标准所要求的信号线;

(7)为了完成上述串行接口的任务,串行通信接口电路一般由可编程的串行接口芯片、波特率发生器、EIA与TTL电平转换器以及地址译码电路组成。

1 方案设计与分析

1.1 硬件电路

该方案的硬件电路设计包括:FPGA芯片、MAX3232,DB9。其硬件电路与微机通信的结构框图如图1所示。

1.2 软件设计思想

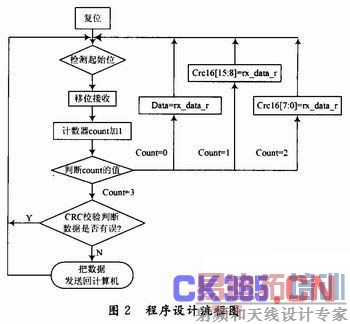

软件部分的设计流程如图2所示。

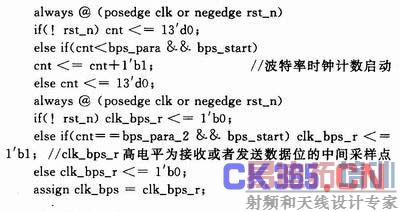

1.2.1 波特率设置

系统时钟是由PFGA的16引脚输入的24 MHz时钟,而异步串口通信的波特率设置为9 600 b/s,所以需要对主频进行分频。分频过程定义了2个常量,分别用来存储波特率96 000 b/s的分频计数最大值bpspara和分频计数的一半bps_para_2。每个系统时钟的上升沿来临时计数器cnt加1,每bps_para_2个系统时钟周期clk_bps改变1次状态,这样就产生了96 000 b/s的波特率。部分分频代码如下:

1.2.2 数据接收

数据接收模块所要完成的任务包括:

(1)连续接收3个字节:1个字节的数据信息和2个字节的数据信息的CRC校验码;

(2)取出这3个字节的第一个字节,重新生成CRC码;

(3)讲新生成的CRC码与接收到得CRC比较,若相同则传输过程中没有出现错误;若不相同则传输过程有错误,等待接收下一组数据。

①单字节串/并转换

串口通信发送数据的格式:1位起始位(低),8位数据位,1位停止位(高),共10位(这里没有校验位ParityBit)传输时的顺序是:起始位+数据位低位---数据位高位+停止位,其时序图如图3所示;

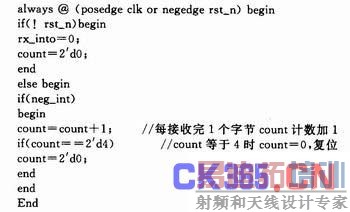

②3字节连续接收并储存

为了连续接收3个字节数据,定义中断寄存器neg_int和计数器count,复位时都清零,开始接收数据时rx_int置高,每接受完1个字节,rx_int清零,此时检测rx_int的下降沿,下降沿到来时计数器count加1,直到接收完第3个字节时count的值是3。部分程序如下:

因为HDL是硬件描述语言,所以必须时刻检测是否有起始位到来,需用几个并行的always语句块来处理。在接受完第1个字节后继续检测下降沿,并把接收到的数据暂存到寄存器data中,接收完第2个字节后仍继续检测下降沿,并暂存数据到crc16[15:8],接收完第3个字节继续检测下降沿,暂存数据到crc16[7:O]。等待下面的校验处理。下面用case语句块来暂存数据。

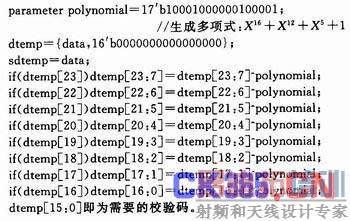

③CRC码生成

循环冗余校验(cyclic redundancy check,CRC)是一种在数据传输中广泛应用的差错检测方法。CRC的设计思想是将数据包当作一个多位的二进制数,用这个二进制数除以一个选定的多项式,所得的余数作为校验数据直接附加在数据后面发送出去,在接收端对数据除以相同的多项式如余数为零则表示没有错误被检测到。CRC的工作过程如下:假设需要发送的数据为8位,校验多项式一般为X16+X12+X5+1。首先将发送数据左移16位生成一个新的数列,然后采用模2运算(异或)将新数列除以校验多项式,所得余数序列即为冗余循环码,将其直接加到数据后面即可。

部分程序如下:

将生成CRC码与接收到得CRC码进行比较,判断传输过程是否有误,若无误就将数据信息发送出去。

1.2.3 数据发送

数据发送部分的功能是将检验完毕后的正确数据发送出去,实际上是一个并/串转换。当数据校验正确后err置位,通过pos_err滤波检测err的上升沿,上升沿到来时pos_err置高1个时钟周期,此时开始进行数据发送。串口通信的传输格式是:1位起始位,8位数据为,1位停止位。所以需要将数据装载成发送格式,然后再发送出去。发送时先发送起始位O,再发送数据低位,然后发送高位,最后在发送停止位1。这部分用计数器num进行计数,在case(num)语句块里,分别发送这10位。

2 实验验证

按照以上设计方案编写Verilog HDL程序,下载到FPGA芯片中,通过微机与设计系统的通信来验证该设计方案的可行性与可靠性。下载程序前,事先连接电路,连接好电源、串口线、 Byteblaster下载电缆。程序代码用开发软件QuartusⅡ5.O下载到FPGA芯片里,具体操作步骤如下:

新建Verilog HDL文件→输入并保存代码→新建工程→设置选项(选择目标芯片,本实验用的是cyclone公司的EPLC6T144C8N,配置方式,下载方式等)→编译→配置引脚→编译→选择下载电缆→下载运行。

按照以上步骤下载好程序即可以进行实验验证。微机串口调试助手的选项如下:波特率:96 000 b/s;校验位:NONE;数据位:8位;停止位:1位;接收区设置:16进制显示;发送端设置:16进制发送。

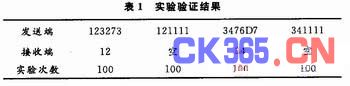

表1所示为实验验证结果,其中的12的CRC码为3273,34的CRC码是76D7。

实验验证结果可以看出,数据传送的正确率很高。

3 结语

简单介绍了FPGA芯片、Verilog HDL、串口通信协议以及硬件电路设计,详细分析了软件部分各个模块的设计方法,并下载程序到FPGA芯片,通过微机与系统之间的串口通信,验证了该设计的可行性与可靠性。在实现过程中,着重分析了移位串/并,并/串转换过程,并加入CRC检验码生成过程和具体校验过程,用Verilog HDL语言编程,实现了串口通信的采集、数据处理、数据发送的全过程。该方案的特点是实现容易,速度快,效率高,实用性强,可以广泛应用于终端、打印机、逻辑分析仪、磁盘等与计算机相距不远的人-机交互设备和串行存储的外部设备。

上一篇:基于组态王的大型烟机监测诊断系统研究

下一篇:LM4702高保真功放器件的设计原理