- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

应对FPGA/SDI子系统中的高速板布局挑战

简介

电视和影院已经进入数字时代。视频图像曾以标准传输率(270Mb/s)传输,后来升级到高传输率(1.485Gb/s),现在已上升到3Gb/s。更高传输率实现了更高分辨率的娱乐图像传输,但同时也使硬件工程师和物理布局设计师面临着更大的挑战。很多视频系统都采用多功能FPGA和多传输率SDI集成电路,以支持高性能专业视频在长距离的传输。FPGA需要高密度、细迹线宽度的传输,而高速模拟SDI传输需要阻抗匹配和信号保真。本论文概述了硬件工程师面临的挑战,并为处理这些挑战提供了建议。

FPGA/SDI子系统

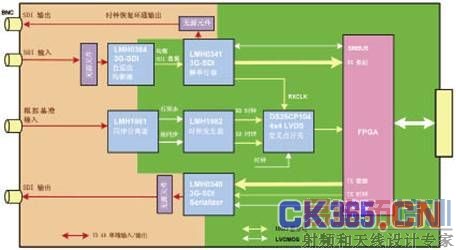

在典型的FPGA/SDI板中,数字视频信号在BNC(卡拴式同轴接头)与高性能SDI75 迹线模拟集成电路之间传输。FPGA和SDI集成电路之间的互连包含通过FPGA细间距球栅发送的多对100 差分信号。其中一个布局难点是75 单端迹线和100 差分迹线的共存。通常,这两种迹线在元件所在顶层上传输。适合75 的迹线宽度对于100 迹线可能过宽。图1是FPGA/SDI的示意框图,显示75 和100 的两个区。

图1 典型FPGA/SDI框图

SDI布局难点

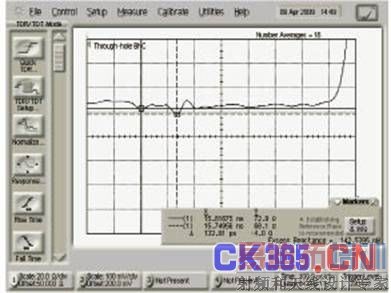

电影与电视工程师学会(SMPTE)发布了同轴电缆上数字视频的传输标准。规定信号幅值为800mV±10%。必须通过芯片外的75 ±1%精确终端电阻器满足此幅值要求。SMPTE标准还包含输入和输出的回波损耗要求,基本规定了输入或输出端口如何近似于75 网络。图2显示SMPTE对回波损耗的要求。

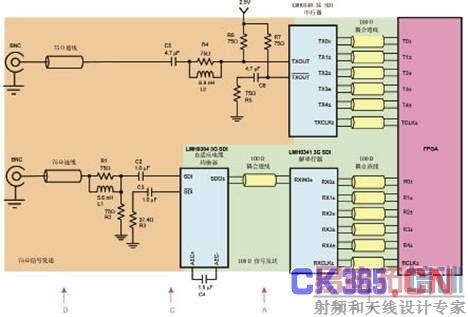

芯片外阻抗平衡网络由电感器和并联电阻器构成,通常用于抵消SDI集成电路的输入或输出电容。大交流耦合电容器(4.7µF)通常用于传输SDI串行位流,以避免低频直流漂移。如图3所示,75 迹线的SDI集成电路及其BNC连接器之间附有多个芯片外无源元件。每个元件都具有串联寄生电感,每个元件焊盘又具有并联寄生电容,从而影响与75 匹配的总阻抗。SDI布局的难点在于最大限度减少外部无源元件在75 SDI端口造成的阻抗失配。

选择FPGA/SDI子系统的板堆叠

应该使用什么迹线宽度 在小于3Gb/s的SDI速度中,铜损耗很小,并不构成选择迹线宽度的重要考虑因素。选择略小于元件接合焊盘的迹线宽度更为重要,以最大限度减少阻抗失配。0402尺寸的无源元件需要20密尔x25密尔的接合焊盘,以使15密尔到20密尔的迹线宽度最适合于75 SDI迹线。

为了便于传输和偏斜匹配,FPGA的100 差分信号使用细迹线宽度传输。宽松的耦合迹线通常用于避免较大的阻抗变化,而分支出的紧密耦合迹线则连接到终端电阻器或交流耦合电容器。

图4显示了适用于FPGA和SDI信号传输的板堆叠。在此堆叠中,SDI信号迹线采用在第4层以GND2为基准的75 单端微带线。GND2是在第4信号层形成的金属岛。第2和第3层的金属(GND1和VCC面)在75 迹线区被移除,以使其不会降低迹线的特征阻抗。FPGA的100 差分迹线是在第2层以GND1为基准的宽松耦合微带线。两个接地基准(GND1和GND2)通过接地缝补镀通孔相连。此板堆叠排列允许通过调节绝缘长度h2自由选择75 迹线的宽度,以及通过调节h1自由选择100 迹线的宽度。

图2 SDI端口和SMPTE限制值的输入回波损耗图

图3 典型SDI电路(仅显示高速信号路径)

图4 具有75

和100

迹线单独接地参考的板堆叠

BNC连接器的布局

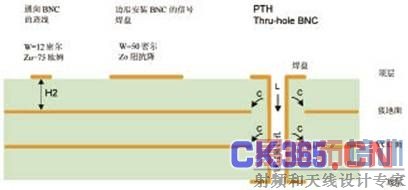

很多SDI板的常见问题是使用非优化BNC连接器布局,因此产生严重的阻抗失配、无法满足回波损耗要求,并削弱了设备的信号保真度。图5显示板的横截面,其中12密尔宽的微带线连接到50密尔宽的边沿安装BNC焊盘上。接地面被置于顶部迹线下的绝缘距离点上,以实现目标迹线阻抗。连接器的接合焊盘是宽微带线,因此焊盘的特征阻抗略低于迹线阻抗。焊盘具有较大的阻抗降,从而影响回波损耗和限制迹线的传输带宽。

图5还显示了通孔BNC布局的横截面。内接地和供电面与镀通孔绝缘,以避免短路。圆柱孔带有一定的电感。每个接地或供电面的镀通孔都具有寄生电容。小间隔的大镀通孔将抑制容易造成大组抗降的多余电容。图6显示具有60密尔孔和20密尔间隔的设计不佳通孔BNC的阻抗形态,图中显示了镀通孔的阻抗从75 迹线下降到40 。

图5 BNC布局的横截面图

图6 设计不佳的通孔BNC的阻抗形态

设计良好的BNC布局

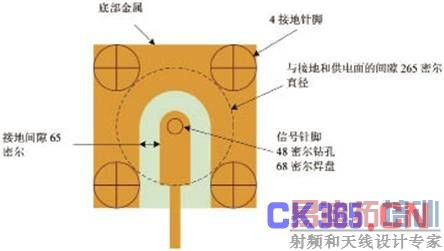

设计良好的BNC布局的目标是避免BNC布局与连接到布局的迹线间产生过多的阻抗失配,可以遵循信号路径查找板结构变化可能导致的阻抗失配。时域反射计是能够确定阻抗失配发生位置的仪器。可以使用电磁仿真器检查板布局设计中的阻抗变化。如果阻抗过低,应设计能够抵消过多电容的板结构;如果阻抗过高,应增加额外寄生电容使阻抗值接近目标值。通过正确的电感和电容值,可以建立具有所需特征阻抗的通孔BNC布局。图7显示良好的通孔BNC布局示例,图8显示非常接近75 目标值布局的阻抗。

图7 良好通孔BNC布局的顶视图

图8 良好通孔BNC布局的阻抗形态

FPGA/SDI板的布局指导原则

FPGA/SDI板的数据传输率低于3Gb/s,信号转换时间约为100微微秒。SDI板布局的难点不在于速度,而在于计划一种布局策略以最大限度减少与75 SDI端口很多外部元件的阻抗失配,设计大BNC控制器的受控阻抗布局和实施支持75 和100 迹线的板堆叠。可以通过遵循以下这些简单的布局指导原则解决这些难点:

•将迹线阻抗设为75 ±10%、100 ±10%

•使用最小的表面贴装元件和最小的无源元件接合焊盘

•选择能最大限度减少信号路径上阻抗失配的迹线宽度

•选择支持单独接地基准75 单端迹线和100 宽松耦合差分迹线的板堆叠

•使用表面贴装陶瓷电容器和射频信号电感器

•使对回波损耗有影响的元件(终端电阻器、阻抗平衡网络)尽可能接近集成电路针脚

•使用75 受控阻抗,设计良好的BNC布局

•保持互补信号发送的对称性

•均匀地传送100 差分迹线(使迹线上的迹线宽度和迹线间隔保持均匀)

•避免陡弯,使用45度弯曲

•遵循信号路径识别几何变化,并预估相应的阻抗变化

•使用整平面。如果需要采用凹凸地面抵消过多的寄生电容,应谨慎使用;借助三维仿真工具决定布局

•使用最短的VCC和接地路径,将针脚连接到通孔面

布局示例

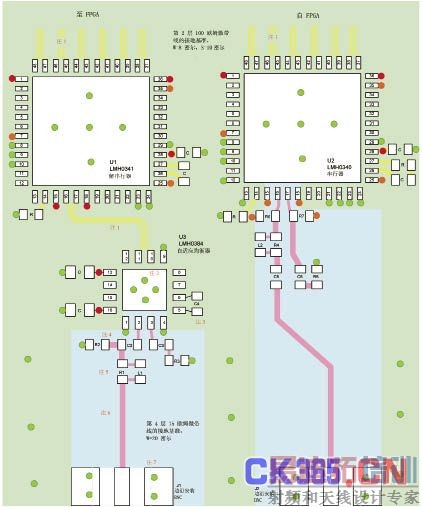

图9是美国国家半导体LMH03843Gbps/HD/SDSDI自适应电缆均衡器、LMH0341SDI解串行器、LMH0340SDI串行器和FPGA(未显示)的简要布局图。本例使用图4中显示的堆叠。第2层(绿色显示)是8密尔宽100 差分迹线的接地基准,它连接到LMH0384的输出针脚SDO+和SDO-以及LMH0340和LMH0341的LVDS信号传送线。第4层上的金属岛(蓝色显示)用作75 迹线的接地面。这两个接地基准使用设备DAP连接通过地面缝合到一起。

图9 LMH0384、LMH0340和LMH0341的布局示例

交流耦合电容器C2紧邻SDI+的输入针脚。阻抗匹配网络L1和R1通过C2尽可能地靠近输入针脚SDI+。75 终端电阻器R2置于C2后方,以最大限度减小接线柱的影响。

这种设计使用0402尺寸元件,尽可能减少75 迹线的阻抗变化,75 迹线通过20密尔微带线连接到第4层基准。BNC使用的布局应具有良好的信号发送,以实现低回波损耗。

图9注释如下:

注1-使用100 差分阻抗连接到第2层基准的耦合迹线。

注2-第2和第4层的接地缝合。

注3-C4邻近集成电路针脚。

注4-C2尽量靠近集成电路输入针脚;R275 接收端子置于C2后方。

注5-L1、R1阻抗匹配网络通过C2邻近SDI+针脚。

注6-使用75 受控阻抗迹线连接到第4层基准。使用0402元件。使用15-25密尔的迹线宽度,以最大限度减少较大元件焊盘导致的阻抗降。

注7-BNC使用75 受控阻抗布局。

总结

SDI板布局的难点在于设计一种方案,可以最大限度减少75 端口上很多外部元件引起的阻抗失配。使用75 微带线以及与无源元件的接合焊盘尺寸相当的迹线宽度可以实现使阻抗失配降到最低的目标。使用第二接地基准就可以为连接到高针脚数FPGA的100 差分迹线灵活选择较细迹线宽度。务必使用75 受控阻抗设计良好的BNC布局。建议在信号路径上查找因布局结构变化引起的阻抗变化,并设计一种方式可以抵消过多电感或电容以保持目标特征阻抗值。通过遵循几个简单的布局指导原则,可以设计符合SDI高信号保真要求的板,并实现高密度连接至FPGA。