- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的高速同步HDLC通信控制器设计

高级数据链路控制HDLC(High-level Data Link Control)广泛应用于数据通信领域,是确保数据信息可靠互通的重要技术。实施HDLC的一般方法通常是采用ASIC器件和软件编程等。HDLC的 ASIC芯片使用简易,功能针对性强,性能可靠,适合应用于特定用途的大批量产品中。但由于HDLC标准的文本较多,ASIC芯片出于专用性的目的难以通用于不同版本,缺乏应用灵活性。例如CCITT、ANSI、ISO/IEC等都有各种版本的HDLC标准,器件生产商都还有各自的标准,对HDLC的 CRC序列生成多项式等有不同的规定。况且,专用于HDLC的ASIC芯片其片内数据存储器容量有限,通常只有不多字节的FIFO可用。对于某些应用来说,当需要扩大数据缓存的容量时,只能对ASIC芯片再外接存储器或其他电路,ASIC的简单易用性就被抵销掉了。

FPGA是现场可编程门阵列,属于超大规模集成电路,具有丰富的系统门、逻辑单元、块RAM和IO引脚等硬件资源。由于FPGA具有重装载功能,可以在其内部灵活实现各种数字电路设计,甚至可以动态改变其内部设计,动态实现不同的功能。

因此,采用FPGA实现HDLC是一种可行的方法。HDLC通信控制器主要是对数据进行CRC校验、‘0’比特插入和加帧头帧尾操作。

1 “0”比特插入模块

HDLC规程规定信息的传送以帧为单位,每一帧的基本格式如图1所示。

![]()

HDLC规程指定采用8 bit的01111110为标志序列,称为F标志。用于帧同步,表示1帧的开始和结束,相邻2帧之间的F,既可作为上一帧的结束,又可作为下一帧的开始。标志序列也可以作为帧间填充字符,因而在数据链路上的各个数据站都要不断搜索F标志,以判断帧的开始和结束。

由于HDLC具有固定的帧格式,以7EH为帧头和帧尾,为了保证透明传输,即只有帧头和帧尾出现连续的6个‘l’,其他地方不允许有连续5个以上的‘l’ 出现,否则就要进行‘0’比特插入,即只要遇到连续5个‘1’,就在其后插入1个‘O’。根据传输数据量的大小可采用以下2种思路实现‘0’比特插入操作。

1.1 遇‘O’缓冲实现法

由于数据中出现多少个连续的‘1’是不可控的,故最终插入‘0’的个数也是不可控的。例如要发送的“有效数据”(包含地址字段、控制字段、信息字段、帧校验字段)为320 bit,则最多会插入64个‘0’。数据是串行输入,每插入1个‘0’,则数据由5位变成6位,则插‘0’后要输入的数据就被“积压”来,插入的‘0’越多,“积压”的数据就越多。如果采用文献中的插‘0’方法,简单的将‘O’插入,将会丢失1位数据,设置1个64位的缓冲,每插入1个‘0’就把后面数据做为1位延时,插‘0’后在把已经延时1个时钟周期的数据加进来,就保证不丢失数据。实际利用VHDL语言编译时,其VHDL代码为:

上述VHDL的思路:矢量a的第64位到第l位分别为datain延时64个时钟周期的串行数据到延时1个时钟周期的串行数据,i的初始数据为O,每遇到连续5个‘1’,插入1个‘0’后,dataout输出为datain延时i个时钟周期的数据。这样就做到了不丢失数据。图2是利用ISE 9.1i仿真的波形图。

由图2可看到插‘0’操作后,数据比未插‘0’前变长了,而且变长了多少位是由数据内容决定的。

该方法编程简单,占用FPGA资源少,在一个模块内就能完成‘0’比特插入操作。

1.2 利用FIFO实现

遇‘0’缓冲实现法在传输大容量数据时,需要设置许多位缓冲,这样就耗费大量的FPGA内部资源,而且随着延时位数增加,门延时呈指数增长,累积到一定程度就会产生误差,所有当数据量大时,上述的方法就不再适用,可以利用FIFO实现。

当数据量大时,“积压”的数据相应也变大,可以利用FPGA内部资源FIFO节省逻辑资源,提高逻辑速度。选择异步FIFO,即读/写时钟不是同一个,这样可高速写入数据,再通过控制读时钟控制读的信息。

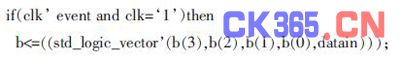

利用FPGA实现的VHDL代码为:

其基本思想是,一旦遇到5个连续的‘1’,就“抹掉”1个时钟,利用ISE 9.1i仿真的波形图如图3所示。

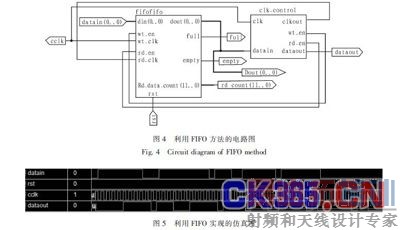

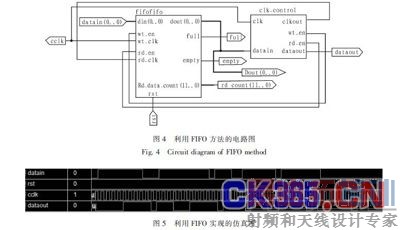

设计一个FIFO与上述VHDL代码产生的模块相连,电路图如图4所示。

利用ISE 9.1i仿真得到的波形图如图5所示。可看到对datain进行了‘0’比特插入操作,保证数据不丢失。而且该方法可根据所选器件的片内资源设置任意大容量的FIFO,并且当片内FIFO的存储量不够时,可先存入一部分数据,等FIFO读取一部分后,不满时再存入一部分数据。

‘O’比特删除操作是‘0’比特插入操作的反过程。在接收时为了还原原本的信息,就要删除发送时插入的‘O’。以逐位延时法为例,dataout最一开始输出延时了64个时钟周期的串行数据,i的初始值为64,当遇到‘lllll’时,i减1,输出延时了i个时钟周期的串行数据。而利用FIFO的方法就是遇到‘lllll’,抹去1个写时钟,将数据写入FIFO,再按规定的时钟把数据读取,当然写入的时钟可用较高的时钟周期。

2 CRC校验模块

帧校验字段用于对帧进行循环冗余校验,校验的范围从地址字段的第1个比特到信息字段的最后1个比特,但为了透明传输而插入的‘0’比特不在校验范围内。

CRC原理实际上就是在一个p位二进制数据序列之后附加一个r位二进制校验码,从而构成一个总长为n=p+r位的二进制序列,例如,P位二进制数据序列,r位二进制校验码,所得到的二进制序列就是,附加在数据序列之后的这个校验码与数据序列的内容之间存在着某种特定的关系。如果因干扰等原因使数据序列中的某一位或某些位发生错误,这种特定关系破坏,因此,通过检查这一关系,实现对数据正确性的检验。

要传输p=16位数据1001011010101011,选定的r=16的校验序列为10001000000100001,对应的FCS帧校验列是用 100101101010101100000 00000000000(共p+r=32位)对2取模整除以10001000000100001后的余数1010100011000001(共有r=16 位)。因此,发送方应发送的全部数据列为10010110101010111010100011000001。接收方将收到的32位数据对2取模整除以r校验二进制位列10001000000100001,如余数非O,则认为有传输错误位。

而多项式乘除法运算过程与普通代数多项式的乘除法相同。多项式的加减法运算以2为模,加减时不进位或错位,和逻辑异或运算一致,即加法和减法等价。则对上述例举的数据的CRC计算过程如图6所示。

模拟上述计算CRC校验值的方法,不难想到可用状态机实现,设置一个17位的矢量,检验最高位是否为零。如果为零,则跳转到状态1,即所有位左移,最低位补1位数据;如果不为零,则跳转到状态0,最低位补1位数据,与“00010000001000010”异或,(以CRC-CCITT为例,由于y16与 ‘1’异或必为‘0’,datain与‘0’异或还为datain),这种思路的VHDL代码如下:

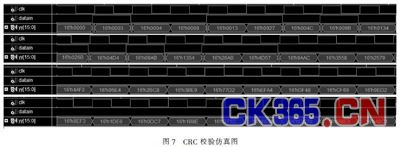

图7为该VHDL代码的仿真波形,可看到该方法模拟对2取模整除的一步步计算。

该方法思想简单,是对2取模整除方法的模拟,直观,易于理解,由于是串行输入,不受需要CRC计算的数据位数限制。由于HDLC通信协议的最大优点是对要传输的信息文电比特结构无任何限制,也就是说,信息文电可以是任意的比特串,不会影响链路的监控操作。因此,这里给出的CRC串行算法符合HDLC传输文电比特结构任意的特点。

3 程序加载验证

经过逻辑综合和时序仿真后,利用ISE 9.1i集成开发软件将程序烧入FPGA,利用示波器观测FPGA按HDLC通信协议标准发出的信号。如要发送的“有效信号”(不含帧头帧尾,未进行 CRC校验及‘O’比特插入之前的原始数据)为“llll llll”,则经过FPGA处理后应发出的数据为“0111 1110 1111 1011 1000 1111 0111 1000 0011 1111 0”,利用示波器检测到的信号波形如图8所示。

由图8可知,对数据进行CRC校验,‘0’比特插入及加帧头帧尾操作,发送数据正确,符合HDLC通信协议标准。

4 结束语

由于HDLC通信协议具有透明传输、可靠性高等优点,在数据链路层应用广泛,而FPGA更具有灵活、高性能、低成本、平台化、可定制等优点,具有系统级能的复杂可编程逻辑器件和现场可编程门阵列实现可编程片上系统也成为今后的发展方向。本文提出的基于FPGA实现HDL-C/SDLC协议方法采用ISE 9.1i编译、综合、仿真、布线、烧写,ISE软件支持器件多,功能强大,操作更方便,因此,该实现方法具有很强的实用性,另外,程序加载入FPGA后发送数据正确,说明该实现方法实用、有效。

上一篇:基于事故安全设计的开关量输出控制单元

下一篇:基于CPLD器件的单稳态脉冲展宽电路