- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA+DSP的软件无线电通用平台设计

引言

软件无线电是具有可重配置硬件平台的无线设备,可以跨多种通信标准,其基本思想是以开放性、可扩展、结构最简的硬件为通用平台,把尽可能多的通信功能用可升级、可替换的软件来实现。因为更低的成本、更大的灵活性和更高的性能,已迅速成为军事、公共安全和商用无线领域的事实标准。软件无线电能够对多种波形进行基带处理和数字中频处理,而数字中频处理能够将数字信号处理的领域从基带扩展到射频。同时,支持基带和中频处理的能力又增加了系统的灵活性,也减小了制造成本。

目前用于数字信号处理的器件有三种:ASIC,FPGA,DSP。ASIC即专用集成电路,它的优点是速度高、体积小以及低功耗,缺点在于可编程能力较弱。

FPGA具备现场可编程能力,速度高,适合处理顺序逻辑,功耗较低;缺点在于处理复杂算法时程序设计难度大。DSP也具备可编程能力,其特殊的硬件结构非常适合数字信号处理算法,且程序设计相对于FPGA要容易;缺点在于功耗高,速度较低,也不适合比特流的顺序处理。基于对运算能力和可编程能力的考虑,选择DSP+FPGA结构。FPGA实现大计算量的信号处理数据通道和控制,让系统延迟最小,而DSP处理器则完成基带处理的算法实现,以实现从一种标准切换至另一种标准。DSP处理器能够动态地在软件的主要部分间切换,而FPGA能够根据需要完全重新配置,实现特定标准的数据通道。

本文介绍了一种基于DSP+FPGA 的数字中频处理通用平台,以对软件无线电的设计提供一种灵活的架构,在这个平台之上利用数字上变频器和下变频器以实现软件无线电中频信号的接收与发射功能,利用FPGA的容量大、可编程实现很多功能,并结合DSP具有高速的信息处理能力的特点,可以灵活方便地对数据进行处理,使得整个平台结构灵活,通用性强,易于扩展。

本平台较其他类似平台的优点在于:

(1)将DSP,FPGA,A/D,D/A,DUC,DDc集成在一块板卡上,集成度高,体积小,功耗小,也减少了数据在多块板卡间传输可能引起的损坏;(2)DUC和DDC采用硬件电路,避免应用软件实现难度大的困难,降低开发难度,缩短开发周期。

1 、数字中频处理通用平台设计方案

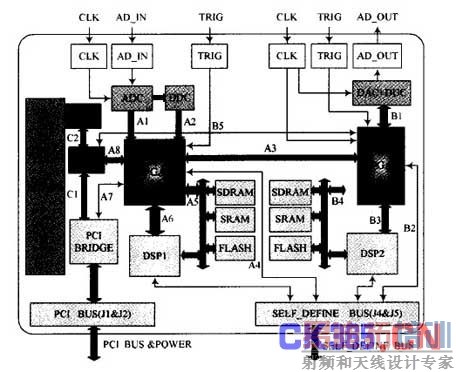

数字中频处理平台为6U CPCI结构,主要由A/D转换及DDC模块、D/A+DUC转换模块、DSP信号处理模块、PCI总线接口、FPGA高速数字传输、存储器等几部分组成。总体框图如图1所示。

图1 系统总体框图

DSP信号处理模块主要用于针对TI的DSP相关的技术开发、应用和仿真,板上集成了两片TMS320C6713浮点DSP芯片,因而可极大地满足通信、雷达、数字电视等高科技领域对信号处理实时性的要求。FPGA采用的是Virtex一4系列的SX35,通过编程可完成使用者想要实现的功能。FPGA 间可通过LVDS总线交换数据,此总线工作速率可满足实时性的要求。在数字下变频和上变频侧,各有一组FPGA和DSP构成数据处理单元,在此单元中它们共用外部存储器,以实现数据的交换、处理与存储。在每组的FPGA和DSP中都有自定义方式的外引线接到接插件,以方便扩展功能。在本系统中,系统可以对外部无线电信号进行采集与处理,也可以把数据从PC机传送到系统中,由系统处理后从D/A通道发送出去。因为FPGA和DSP具有系统随时更新程序的功能,所以在对无线电信号的处理上具有很强的灵活性。

系统PCI管理芯片采用Quicklogic公司的QL5O64,这是一款反熔丝设计的芯片,符合PCI V2.2规范,包括PCI部分和用户部分。PCI嵌入式内核由各种控制器和一系列FIFO组成,它具有零等待状态猝发连接能力,可提供高达600 MB/S的PCI数据传输率,主要实现系统与PCI总线的连接。主机可以通过PCI总线实现对板上所有资源的访问,包括对FPGA及DSP的程序配置,对系统工作寄存器的配置,对内存的读写。QL5O64还可以作为PCI总线主设备,以DMA方式与主机内存交换数据,发起iNItial方式访问PCI总线上其他设备。

另外,利用QL5064器件上的FPGA部分模块,可以实现PC机通过PCI总线随时更新FPGA和DSP程序。

本系统可以在一个板卡上完成软件无线电的接收与发射功能,同时具有系统可以随时配置的硬件DUC,使用者也可以采用FPGA 实现软核DUC的功能;FPGA和DSP都能进行数据处理,为使用者提供了多重选择;硬件设计上实现了可由PC机通过PCI总线随时更新FPGA和DSP的功能,极大地方便了程序调试。

1.1 发射前端数字中频处理系统

发射前端是由高速DAC+数字上变频、抽取滤波处理模块以及专用数字信号处理(DSP)模块组成。信号处理模块由FPGA 和DSP组成,DSP完成复杂算法的计算,而FPGA完成路径选择、工作配置等实时性强的工作。经信号处理模块处理后的数字信号送到数字上变频及抽取滤波处理模块,经处理后再送到高速DAC传送给发射系统。

数字上变频DUC与DAC的实现采用AD公司的AD9857。AD9857是Analog Devices公司推出的一种单片混合信号的14位积分数字上行转换器,集成数字上变频DUC功能与DA转换功能的DDS芯片。采样速率为200 MSPS,可产生直流到80 MHz的数字输出和80 dB窄带的无杂散信号动态范围。

AD9857具有200 MHz内部时钟速度,集成了带锁定指示器的4~20倍可编程时钟倍频器,可提供高精度的系统时钟;内部32位正交DDS,可实现FSK调制功能;14位DDS和DAC的数据路径结构,可接受复合I/Q输入数据;32位频率控制字,而且控制接口简单:

10 MHz串行,并与SPI兼容;具有反转SINC功能,在DAC变换之前恢复出想得到的信号包络;有很好的动态特性:当65 Hz模拟信号输出时,D/A转换电路输出的无杂散动态范围SFDR大于80 dB,并且能够对8位输出进行幅度控制。

1.2 接收后端数字中频处理系统

接收后端是由高速ADC模块、数字下变频、抽取滤波处理模块以及专用数字信号处理(DSP)模块组成。输入的模拟中频信号先经过高速AI)C模块,在中频进行带通采样数字化,然后进行数字下变频,将感兴趣的信号转换至基带,同时做抽样率转换及滤波处理,之后由后续的专用数字信号处理器(DSP)进基带信号处理。

A/D采样之后的数字信号速率非常高,要从这些高速信号中得到有用的基带信号,需要有效地对其进行数字下变频、抽取、滤波等处理,这些功能可以采用现场可编程门阵列(FPGA)来实现。FPGA 具有较高的处理速度和较高的稳定性,同时又具有设计灵活、易于修改和维护的优点,可以适应不同的系统的要求,采用灵活的结构满足不同的需要,提高了系统的适用性及可扩展性。专用数字信号处理器(DSP)主要是通过软件来实现数字基带信号处理以及比特流控制、编码解码等高速的数据交换和处理功能。DSP的运算速度和精度决定着系统的数据处理能力,同时也会对整个系统的性能和结构产生重要的影响。

AD芯片采用AD公司的AD*5。AD*5是一种高速、高性能、单片14位ADC,它的高速性能特点允许用于采样速率高达105 MHz的中频采样。

AD*5的数字输出电平与CMOS 兼容。因为AD*5的转换速率很快,所以允许更经济有效的设计。转换后的数字信号送人到下变频模块DDC中进行处理,DDC采用AD公司的AD6*。从AD6*中出来的数字信号再由FPGA存入板上SDRAM 中,以便于由DSP芯片加以处理。DDC可以由系统随时进行配置,这样可以减轻FPGA编程的压力。

2 系统测试与分析

2.1 稳定性测试

稳定性是一个系统长时间工作的一个重要指标。

测试时使用两台信号源,信号源2输出10 MHz参考信号给信号源1,使两台信号源输出的信号严格相参。信号源1产生一个外时钟信号,而信号源2产生一个10 MHz正弦波信号。通用处理平台对10 MHz正弦波进行采样,并通过内部DDC将采样的10 MHz正弦波(将DDC的中频设定为1O MHz)正交解调为直流I,Q信号。解调出的直流I,Q信号送到计算机中,用Mat—lab求幅度和相位。

每隔20 min采集一组数据,共采集了3组数据。

数值如下:

(1)幅度均值为70.41 dB,标准差为0.003 2 dB;相位均值为116.82°,标准差为0.055 3°;

(2)幅度均值为70.41 dB,标准差为0.003 1 dB;相位均值为116.78°,标准差为0.057 6°;

(3)幅度均值为70.40 dB,标准差为0.003 1 dB;相位均值为116.75°,标准差为0.053°。

从三组数据可以看出,接收系统随时问变化稳定性很好。如图2所示。

图2 第一次采集的信号幅度和相位。

2.2 信噪比测试

ADC时钟为80 MHz,采集的输入AD信号是5 MHziE弦波,对采集的数据用Matlab计算其方差 。

(信号叠加噪声的功率),并结合噪声功率,按照式(1),最终得到信噪比为 48.081 0 dB。

DDC时钟80 MHz,抽取设定16,A/D模拟信号输入为10.1 MHz正弦波,DUC中频为10 MHz,对采集的数据用Matlab进行方差计算,最终得到的信噪比为45.514 4 dB。

![]()

式中:![]() 表示信号叠加噪声的功率;

表示信号叠加噪声的功率;![]() 表示噪声功率。结果表明,信噪比满足通信要求。

表示噪声功率。结果表明,信噪比满足通信要求。

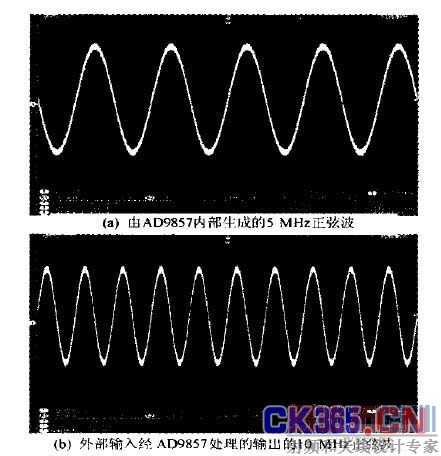

2.3 D/A 输出测试

图3(a)是配置DUC在DAC芯片内部生成的5 MHz正弦波的输出显示(4.996 MHz);图3(b)是从FPGA给DAC的一个10 MHz正弦波得到的波形显示(9.996 MHz)。从这两个波形显示来看,AD9857器件的DUC部分工作效果很好,其DAC输出效果也非常好。

图3 D/A 输出测试。

3 结 语

本系统中,FPGA可提供通用的计算结构,实时性好,非常适合于软件无线电中基带和IF数字处理的需要。另外,通用处理DSP与FPGA结合使用,发挥各自的优势,能够增强功能,改善吞吐量,减小系统成本和降低系统功率。板上设计有硬件数字下变频和数字上变频器件,可以用系统对它们进行灵活的配置,使得对DDC和DUC的应用变得简单,初学者也能很容易地实现这些功能。目前,本文所设计的通用平台系统,已作为产品成功地应用于某院校的电子对抗项目。