- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于TMS320VC54X的USB2.0硬件接口设计

USB总线具有传输速度高、热插拔、即插即用等特点,深受广大用户青睐,但由于USB通信协议和开发手段的复杂性,给研究人员的开发应用增加了一定的难度。CYPRESS公司生产的CY7C68001通用USB2.0接口控制器是基于应用层编程的接口器件,相对于其它基于链路层编程的接口器件,使用简单,开发方便。因此我们在深入研究CY7C68001的特点的基础上,对TMS320VC54X进行USB功能接口设计。

1 USB测控系统框图

测控系统的框图如图1所示。

2 CY7C68001的主要特点

CY7C68001符合USB2.0规范;支持高速(480Mbps)或全速(12Mbps)USB数据传输;4个可编程端点共享4KB的FIFO,每个端点对应的FIFO空间大小及FIFO状态可编程;8/16位双向命令接口、配置灵活(同步/异步可配置,状态引脚、读写引脚以及极性可编程),数据I/O口可与DSP、FPGA或其它ASIC同步/异步通信;智能SIE功能(可在不借助微处理器中断的前提下完成枚举);集成的锁相环功能;I/O口为3.3VTTL电平,可承受5V电压。

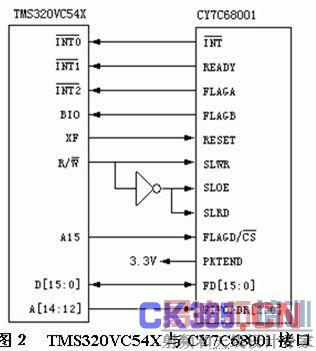

3 TMS320VC54X与CY7C68001的异步接口

接口框图如图2所示,CY7C68001相关引脚说明如下: ![]() :表明CY7C68001有中断事件发生,或反映对于CY7C68001的读操作结束;READY:通知TMS320VC54X可以对CY7C68001读写;FLAGA、FLAGB、FLAGC:报告由FIFOADR[2:0]选择的FIFO状态,默认分别对应为FIFO自定义、满、空状态;FLAGD/ :FIFO状态/片选可选,默认为片选信号;SLOE:CY7C68001驱动并行数据总线,常与SLRD短接;SLRD:并口读有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;SLWR:并口写有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;PKTEND:总是高电平,将当前的缓冲区提交给上位机USB;FD[15:0]:数据总线;FIFOADR[2:0]:提供给与TMS320VC54X接口的FIFO地址选择。

:表明CY7C68001有中断事件发生,或反映对于CY7C68001的读操作结束;READY:通知TMS320VC54X可以对CY7C68001读写;FLAGA、FLAGB、FLAGC:报告由FIFOADR[2:0]选择的FIFO状态,默认分别对应为FIFO自定义、满、空状态;FLAGD/ :FIFO状态/片选可选,默认为片选信号;SLOE:CY7C68001驱动并行数据总线,常与SLRD短接;SLRD:并口读有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;SLWR:并口写有效信号,在SLRD有效且同步通信时,FIFO指针在每个IFCLK的上升沿递增;PKTEND:总是高电平,将当前的缓冲区提交给上位机USB;FD[15:0]:数据总线;FIFOADR[2:0]:提供给与TMS320VC54X接口的FIFO地址选择。

4 CY7C68001主要寄存器说明

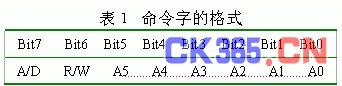

命令接口寄存器:命令字的格式如表1所示:

A/D对应地址/数据,0 表示本次操作为数据读或写,1 表示本次操作为地址写 。 R/W表读/写操作选择,0 写操作,1 读操作。A[5:0] 地址/数据,当A/D=0时,A[3:0]为数据半字节,A[5:4]未用。命令字为8位,命令字数据分两次读出或写入 ,对于每个字节而言,先读写高4位,后低4位。当A/D=1时,A[5:0]为将要寻址的命令寄存器地址。

端点配置寄存器(EPXCFG):对USB端点类型、方向和大小进行配置。端点2、4、6和8共享8X512byte的RAM,通过配置,端点2、6分别享有2、3或4个512byte大小的缓冲区,端点4、8最大只能配置成两个缓冲区。本文使用默认端点配置(每个端点对应512B*2缓冲的Bulk配置)。EPXPKTLENH/L:端点缓冲区大小寄存器。FLAGSAB/FLAGSCD:FIFO引脚标志分配寄存器。EPXPFH/L:确定每一端点对应FIFO标志大小的寄存器。

5 CY7C68001提供给DSP两种软件接口

(1)FIFO接口:CY7C68001内部4Kbyte的RAM(8个512byte块)通过编程,分配给EP2、EP4、EP6和EP8直接作为FIFO。

(2)命令接口:用于设置CY7C68001、读状态、加载描述符和访问端点0 。

DSP通过对CY7C68001地址线FIFOADR[2:0]的访问完成上述两种接口,地址分配如表2:

6 DSP与CY7C68001的通信

本部分包括DSP自身初始化、DSP对CY7C768001初始化、DSP协助HOST计算机枚举CY7C68001、中断处理以及对CY7C68001的各状态监控。由于本文使用CY7C68001默认的描述符信息,所以在枚举时只要提供厂商、产品及设备代码(VD、PD、DD)即可,如果把这部分代码烧写到符合I2总线接口的EEPROM,并连接到CY7C68001的SCL、SDA引脚,USB枚举时,在SIE作用下,可以自动完成枚举。在DSP初始化中对I/O口等待状态寄存器设置为7,以适应同CY7C68001的数据交换。

CY7C68001的初始化:CY7C68001的初始化是通过对它的一系列寄存器进行设置完成的。CY7C68001的地址FIFOADR[2:0]为100时,选中CY7C68001的命令接口。通过CY7C68001的命令接口,可以访问37个寄存器、端点零缓冲器(64个字节FIFO)和描述表(500bytes的FIFO)。对于这些寄存器、缓冲器和描述表的读写操作,根据上面的论述要分两步进行,即在READY有效时,先向命令口写入要寻址寄存器的子地址和操作类型(读或写),之后,在READY再次有效时分两次读写命令口,即可读写一个字节的数据。相应读写时序(图3、图4)及代码如下:

void WriteRegister (BYTE r, BYTE d) //寄存器号r,要写入的数据d

{

low_level_command_write (0x04, (r " 0x80)); // bit7 = 1, bit6 = 0,写请求

low_level_command_write (0x04, (d & 0xF0) >> 4); //写数据的高四位

low_level_command_write (0x04, (d & 0x0F)); //写数据的低四位

}

BYTE ReadRegister (BYTE r) //寄存器号r

{

BYTE d; //临时变量d

read_interrupt = TRUE;

low_level_command_write (0x04, (r | 0x80 |

0x40)); //读请求, bit7 = 1, bit6 = 1

while (read_interrupt) //等待 SX2 有数据

d = low_level_command_read (0x04);//读数据

return (d);

}

FIFO标志的获取:FLAGA-FLAGC的高低电平反映由FIFOADR[2:0]所选取的FIFO状态,FIFO标志所代表的信息可以通过对FLAGSAB/FLAGSCD寄存器进行编程配置,对FLAGX的获取可以通过硬件中断裁决,也可以通过对相应状态寄存器的查询裁决,本文对FLAGA、FLAGB通过硬件中断裁决,对FLAGC通过状态寄存器的软件查询裁决。

有关中断:CY7C68001有6个中断源,可以分别通过对中断使能寄存器的各位进行设置,一旦中断事件发生,CY7C68001的引脚就被置低,并且置中断使能寄存器的相应位(即中断使能寄存器同时充当中断标志寄存器,中断使能寄存器具有读写属性)。当中断发生时,中断标志寄存器的状态字映射到FD[7:0],所以中断发生后,DSP对CY7C68001简单的一次读操作即可获取中断信息,识别中断源并进行相应处理。相对于中断标志寄存器的读操作,其它对CY7C68001寄存器的读操作通常要先发送一次读请求,并且收到READY响应后,才可以读取数据。

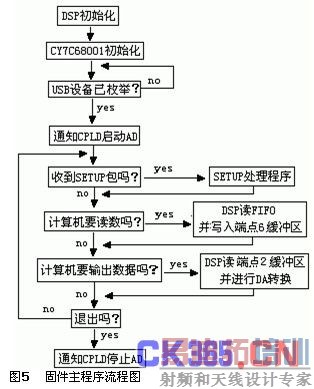

7 USB固件程序的组织

本设计主程序流程如图5所示:

8结束语

在设计开发中,DSP固件程序的组织应综合考虑以中断方式工作的USB通信部分和以查询方式工作的DSP数据采集、控制部分。由于以中断方式工作的USB通信程序随时都可能打断以查询方式工作的DSP数据采集、控制程序,造成数据丢失,相位紊乱,我们采用CPLD进行AD、DA逻辑控制,并运用FIFO数据缓冲机制,减小了DSP压力,取得了良好的效果。

本设计中,TMS320VC5402与CY7C68001接口之间采用异步信息交换。该方案对于使用其它微处理器开发基于CY7C68001的USB2.0接口,或在微处理器与CY7C68001之间采用同步信息交换也有良好的借鉴作用。

上一篇:基于DDS的程控信号发生器设计

下一篇:智能化数控调谐文氏电桥陷波器研究