- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于CC1101的无中心数字对讲机设计

1 引言

对讲机在诸多行业领域广泛应用。虽然模拟对讲机现今仍垄断市场,但数字通信以其更丰富的业务种类,更好的业务质量、保密性和连接性,尤其可提高频谱效率,更有效利用宝贵的频谱资源,因此对讲机数字化是大势所趋。这里介绍一种基于CC1101射频器件的数字无线对讲机的语音通信技术。

2 整体设计方案

虽然提供包含图像、文字、语音的综合业务是未来对讲机的发展趋势,但鉴于对讲机的数字化研究尚处于起步探索阶段,而且语音传输仍是对讲机最广泛最重要的作用,该系统设计的核心是经语音数字化处理后通信更安全可靠,话音更清晰。此外,由于业界至今尚无统一的标准和法规,系统应留存一定的扩展和变换空间,以适应新的变化和进一步研究的需要。

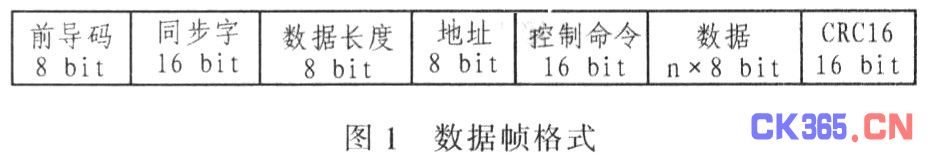

得益于微电子技术的长足进步和快速发展,射频电路的灵敏度不断提高,无线接收机在相应的发送设备不工作时也会有数据解调输出,因而无线通信系统中有必要使用数据帧分组传输数据。还需要使用帧同步技术保证通信系统能从混乱的数据中识别合法的数据帧。由于在无线通信系统中存在干扰、噪声、多径、衰落等现象,使得无线通信信道在传输数字信息时经常出现误码,为此,常采用信道编码技术,在帧中增加校验码元。在无线通信中,最常用的是CRC16,它可以纠正一定程度的随机错误,但却没有能力纠正突发差错的能力,需要用交织编码的方法使其变成交错码。

此外,为保证通信的可靠性,还需要合理设置帧的长度。帧长与编码方式有关,曼切斯特编码时不要超过256字节,若采用其他方式,则不要超过64字节。采取短帧方式通信有利于降低干扰,但帧太短又会增加开销,降低效率。此外,帧的长度还受硬件系统限制,如处理器的处理能力、缓冲、天线带宽等。综合各方面因素,这里采用图1所示数据帧格式。由于语音信号一般比较微弱,根据Mu/A律编码规则,容易出现长连“1”或长“0”情况。若出现这种情况,由于长时间不出现“0”点,接收端的本地同步信号的相位会逐渐漂移,甚至失步。若采用变换归零或重新编码的方式,又有可能降低系统抗干扰能力或频带利用率。为此,需要采用扰码技术,消除长“1”长“0”。

为了实现一对一双丁通话和一对多的广播,该系统采用时分双工(TDD)方式,分成接收和发送两个时隙,保留1.5 ms时间作为射频部分的收发转换保护。

3 系统硬件设计

使用微处理器,通过软硬件的配合实现设计功能;采用基于CC1l01的设计方法,根据需求定义其内部逻辑和引脚;运用“白顶向下”和“模块化”的理念,是现代电子系统设计的特点。因而,该系统采用DSP处理语音数据,使用MCU以弥补DSP控制上的缺憾,采用优秀设计的射频器以降低软件复杂度和MCU的负荷。系统逻辑框架如图2所示。系统由射频模块、语音处理模块、MCU模块、人机接口模块和电源模块组成。系统主处理器负责所有设备控制、任务调度、功能协调、通信协议控制。该系统采用TI公司的MSP430F149,该器件拥有60 KB的Flash ROM和2 KB的SRAM。人机交换模块是连接使用者与系统的桥梁,指示系统工作状况,接收使用者的指令。语音处理模块的语音信号经麦克风进入A/D转换器,经采样量编程数字信号,传输至DSP,实现数字滤波和压缩。语音处理器选用TI公司的TMS320VC5509A,与经典的C54x相比,其综合性能提高5倍,而功耗却仅为C54x的1/6。其工作频率高达200 MHz,具有3个McBSP,64 KB的DARAM和192 KB的SARAM。DSP与MCU间采用SPI通信方式,DSP的McBSP1接MCU的USART1,MCU主模式,DSP从模式。SDRAM采用HY57V641620,具有4 M×16 bit容量,工作频率为72 MHz,内核速率为DSP一半,与DSP的EMIF可直接无缝连接。

CODEC实现语音信号的采样、模/数转换、编码后传输给DSP进行信号调理包括滤波压缩等。在接收节点,则接收DSP传来送的信号,数模转换后还原成模拟语音信号,由于此时的信号比较微弱,加入音频功率放大器MAX4368放大,再输出至扬声器。CODEC选用TI公司的TLV320AIC23B(以下简称AIC23B),与DSP的McBSP模块实现无缝连接,串行传输数据;而DSP通过I2C总线初始化AIC23B。该系统采用主从模式,AIC23B 工作在主模式下,向DSP传送收发数据所需的时钟和帧同步信号。

该系统采用1 M×16 bit的Flash以解决上电复位后DSP程序加载问题,需要20根地址线,但DSP的PGE封装仅引14根地址线,因而使用CPLD映射到DSP的一个CE空间以扩展地址。具体连线方式请参看文献[5]。

从DSP出来的语音信号经由MCU控制到达射频模块,加入前导冗余同步码等构成帧后经交织发射。CC1101是TI公司一款高性价比的单片UHF收发器,为低功耗无线电应用而设计。它是CC1100器件的加强升级版,灵敏度更高,功耗更小,带宽更大。MSP430F149与CC1101采用SPI方式通信,MSP430F149工作在主模式,使用USART1模块,3线模式,CC1101从模式,工作在403~425 MHz频段内。射频模块电路如图3所示。

射频模块布线是整个系统PCB板设计的中核心。外围器件最好选用体积小的贴片元件,滤波电容尽可能接近器件引脚布置,这样滤波效果会更好。尽可能将数字电路远离射频电路,因为数字电路存在陡峭的上升下降沿,所以DSP和MCU都是射频电路的巨大噪声源。也可以考虑使用金属屏蔽罩,虽然该办法存在很多缺点,但仍然非常有效,而且在很多时候是隔离关键电路的唯一办法。虽然CC1101的使用手册给出了外围器件的详细参数,但实际应用中,很多时候阻抗匹配仍然需要重新测量计算,也要调整相应器件的参数。比如接地电容,由于PCB板存在分布电容,实际使用的电容要比推荐的略小一些。整个PCB板最好采用统一接地方式。虽然数字地会干扰射频地和模拟地,但是若分开成3部分,最终总是有些高速信号线要穿过这些分开的接地点。

为了提高系统稳定高质量的能源和准确的脉冲信号。CC1101单独使用了27 MHz的无源晶体振荡器,MCU则采用8 MHz,DSP与AIC23B共同使用一个12 MHz晶体振荡器,DSP再用软件设置为144 MHz。此时,DSP需要的内核电压为1.35 V,外围电压为2.7~3.6 V,AIC23B需要1.5 V,其他器件工作在3.3 V。所以系统电源将采用5 V供电,然后用LDO稳压器,分别降成各个器件所需的电压。

4 系统软件设计

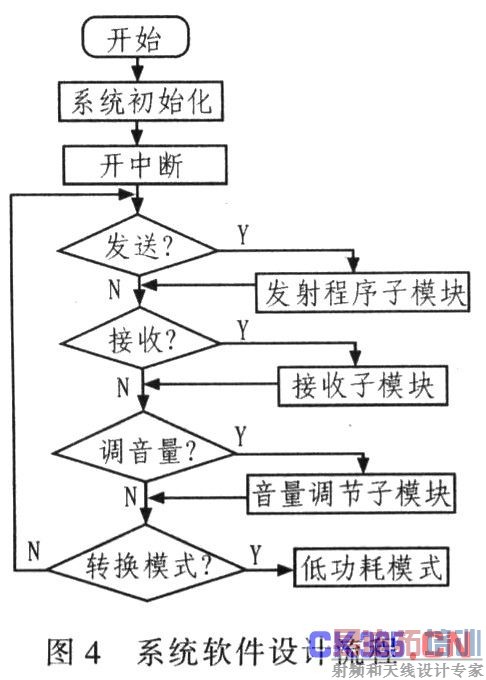

系统软件设计包括MCU和DSP两部分。MCU部分包括各硬件驱动程序和各硬件间的协调调度,以及通信协议程序;DSP的主体是语音处理算法的设计。这里主要讨论MCU程序设计。

CC1101拥有卓越的数据包处理能力。发送时,只需简单设置寄存器,当用户往CC1101内的TXFIFO写入数据后,器件自动在数据包内增加前导字节(长度可控),同步信息,CRC16校验,并根据寄存器设置将FIFO内写入的头两个字节数据标志为长度信息(此功能可选)和地址信息(可选)。接收状态下,器件自动侦测前导码,同步码,地址信息和计算并比较CRC16。此外,CC1101还支持变长数据包格式和交织功能。这些原本需要复杂算法和巨大运算量和存储空间的功能由硬件支持,MCU的编程难度大大降低,其负荷也大为减轻。

程序采用中断程序+循环主程序的方式。将最紧急需要立即处理的事件,设置为高优先级中断,以便在多个中断同时申请中断时能够优先得到响应。中断2~6分别是MCU与DSP和CC1101的数据收发及键盘信号监测。由于MSP430的速度很快,其他事件的处理都放在主程序中,循环执行。为了节省能量,若无外部信号要处理,主程序循环一段时间后,系统转入低功耗模式中。MCU程序的开发环境为IAR Systems,采用汇编语言编写。图4为系统软件设计流程。

5 CC1101编程要点

CC1101的寄存器众多,包括状态寄存器将近80个,若手动配置容易出错,因此Chipcon公司提供了SmartRF Studio射频仿真软件。该软件可根据程序员的需求(包括频率,速率,调制方式,等)自动给出一组最佳的寄存器配置参数,若与TI公司的相关评估板联用,还可以对射频器件的PLL回路的晶体振荡器选择,频道间隔,分频,调制,数据格式,数据比率,RF射频功率输出进行仿真。用以评价RF PCB的层设计是否符合射频设计规范。使无线电系统设计人员在没计早期阶段就能准确轻松评估RFIC,加快电子系统开发。但需要注意的是:CC1101器件处于idle状态时才能对寄存器进行配置。CC1101的数据接口与控制接口复用。传输数据或命令主要依靠访问不同寄存器进行区别,地址与命令/数据则是依靠时序区别。

CC1101有2个64字节FIFO,一个接收数据(RX FI-FO),另一个发送数据(TX FIFO)。FIFO控制器能侦测RXFIFO是否上溢和TX FIFO是否下溢。但是写FIFO时,MCU必须控制TX FIFO是否产生溢出;读RX FIFO时,MCU也必须避免读空值,这些错误CC1101都无法侦测到。

6 结束语

针对传统模拟对讲机仅单工通信和频谱利用率不高的缺限,提出一种基于CC1101的无中心数字对讲机设计方案,该设计方案可应用于抢险、救灾、野外作业等缺乏基础通信设施的环境。射频模块电路设计是方案中的重点,无论是仪器测得的参数还是反复实地测试都表明射频部分的电源、接地和阻抗匹配不仅极大影响通信距离也密切关系通信质量。由于未使用功率放大器和所用天线增益较低(2 dB),该系统的实际通信距离与当今主流模拟对讲机相比尚有差距,但该设计方案仍对对讲机的数字化研究工作有一定参考价值。

上一篇:基于NiosII的SOPC中EEPROM

Controller

Core的设计

下一篇:单片机与PC机串行通信中波特率的确定