- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA技术的数字相关器的设计与实现

1 引 言

同步在通信系统中占有非常重要的地位,同步系统性能的高低在很大程度上决定了通信系统的质量,甚至通信的成败。相关器是同步系统的关键部件之一,因此,要求相关器须有比其它部件更高的可靠性。实际应用中,相关器可用软件实现也可用硬件电路实现,后者更适合于高速数据通信中的相关检测。本文在总结一般数字相关器设计的基础上,设计实现了一种高性能的数字相关器。

2 数字相关器的一般原理

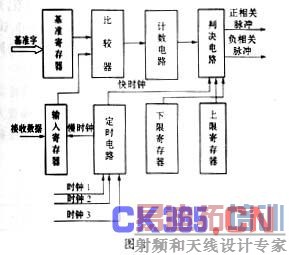

数字相关器的一般原理如图1所示。

相关器以数倍接收数据bit速率对所输入的接收数据取样,每个取样bit移入数据输入寄存器,然后逐bit地与存贮在基准寄存器中的基准字进行比较,若两者一致,输出正相关脉冲,若输入数据bit与基准字补码相一致,则输出负相关脉冲。正相关和负相关所允许的最大不一致bit数分别存贮在相关器的上限寄存器和下限寄存器里。快时钟频率一般是慢时钟的数十倍,相关计数判决在快时钟的后半周之内必须完成。因此,时序控制比较复杂,而且输出相关峰的宽度很窄(半个快时钟周期),系统工作时容易造成丢峰、漏峰等不良后果,给系统带来了潜在的不稳定因素,且增加了系统内在功耗。为此,本文提出一种用VHDL设计的在FPGA器件中实现的高速硬件相关器(无快时钟,适时运算处理)的设计方法。

3 用VHDL设计数字相关器

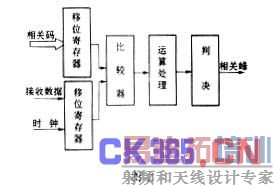

用VHDL设计数字相关器的逻辑框图如图2所示。

本文用VHDL设计的数字相关器,仅需一个数据时钟,避免了复杂的时序控制,它采用适时运算处理,所得相关峰的宽度是一个数据比特,比较容易捕获,不会产生丢峰漏峰等不良现象,提高了相关器的可靠性。

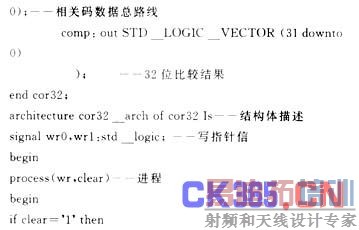

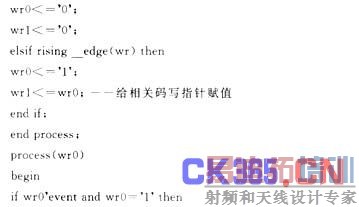

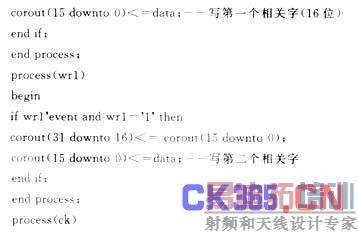

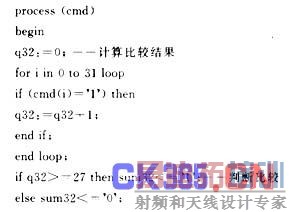

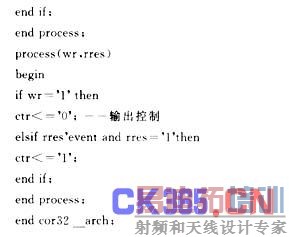

下面给出32-bit数字相关器的部分VHDL源程序。

4 FPGA实现32-bit数字相关器

本设计选用XC4044XLA FPGA芯片实现,开发工具是XILINX公司的FoundationSeries3.1i。相关器仅占该芯片部分资源,该芯片其余资源为同步系统中其它部件所用。

下面给出该相关器测试结果。给相关器设置32位相关码:将0F7ADH、96E8H依次由低到高置入相关码寄存器中,其接收数据中的独特码与相关码相同,测试结果如图3所示。

5 结束语

用VHDL设计在FPGA芯片中实现数字相关器,简化了相关器复杂的逻辑电路设计,降低了相关器的功耗,提高了相关器的可靠性。该相关器已成功地应用于某无线通信系统中,性能稳定可靠。