- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

MPC850中复位逻辑和CPM协议切换的CPLD实现

1 引言

近年来,微处理器(MPU)在嵌入式系统研发中所占地位越来越重要,很多应用场合对MPU的处理速度、集成密度也提出了更高的要求。Power PC系列MPU是Motorola公司推出的面向嵌入式应用的专用MPU,它在片内集成了基于RISC体系的微处理器的内核和支持多种通信协议的通信处理器(CPM),具有强大的通信和网络协议处理能力,可广泛应用于通信和网络产品中。CPLD(Complex Programmable Logic Device)是一种复杂的用户可编程逻辑器件,和FPGA相比,由于采用连续连接结构,易于预测延时,从而使电路仿真更加准确。近年来,由于采用先进的集成工艺和大批量生产,CPLD器件成本不断下降,集成密度、速度和性能大幅度提高,一个芯片就可以实现一个复杂的数字电路系统,再加上使用权方便的开发工具,因此使用权CPLD器件可以极大地缩短产品开发周期,给设计修改带来很大方便。

嵌入式系统常用MPU和CPLD联合设计。现以PowerPC系列MPC850和 Xilinx 公司的XC95144XL为例来介绍实现MPU功能的CPLD辅助设计方法。实际上,MPC850的外部复位和通信模块(CPM)的设计在整个系统设计中占用重要地位,也是调试硬件中最容易出问题的环节。本文将对MPC850的外部复位逻辑和通信模块的复用作一探讨,并给出了这两部分的CPLD逻辑实现方法。

2 MPC850的复位逻辑和CPLD实现

2.1 复位逻辑

MPC850内部的复位时钟具有复位控制逻辑,以及决定复位起因、同步和相应复位的逻辑模块。概括起来,MPC850总共具有以下复位源:

*上电复位;

*外部硬复位;

*内部硬复位:包括失锁、软件看门狗复位、校验停复位、调试口硬复位;

*JTAG复位;

*外部软复位;

*内部软件复位:指调试口软复位。

设计中需要用户参与的主要是上复位和外部硬复位。其中上电复位的复位过程如下:

(1) 产生上电复位信号PORESET

(2) PORESET有效,CPU配置SCCR寄存器,PORESET保持时间至少在3μs以上。

(3) PORESET无效后,CPU采用MODCK(时钟模式配置)并锁存,同时初始化时钟。

(4) CPU驱动HRESET和SRESET信号512个时钟周期,512周期结束后,如果RSCONF信号接低,则CPU从数据总线上采样配置数据,并将内部产生 的HRESET和SRESET信号置为无效;如果RSCONF信号接高,则CPU按内部缺省值进行配置。

(5) 计数器计数16个时钟周期,然后采样外部硬复位信号和外部软复位信号,如果存在职效的外部硬复位信号或软复位信号,则计数器清0,并重新计数,否则跳出,执行正常操作。

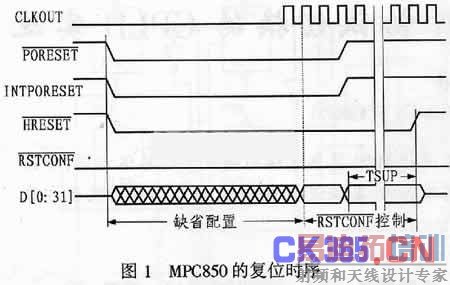

系统中硬件复位主要用于在CPU感知外部硬复位信号有效后,产生内部硬复位信号,然后按照上述上电复位步骤从第4步开始执行。其时序图如图1所示。

可见,相比一些常用的MPU器件,MPC850的复位逻辑比较复杂,而且对复位控制的时序有严格的要求。通常的设计需要较多的外部器件来实现逻辑控制,而采用一片CPLD则只需编写简单的代码就可以了,且易于调度。本应用于设计采用 Xilinx 公司的XC95144XL进行逻辑设计。

2.2 基于CPLD的实现方法。

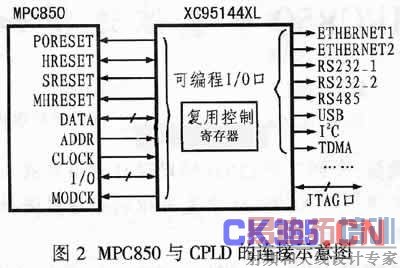

设计时,将MPC850的复位信号(上电复位poreset、硬复位hreset、软复位sreset)连接到XC95144XL的连接方法如图2所示。

该方案中CPLD的上电复位设计过程如下:

(1) 系统上电后,上电复位poreset由XC95144XL产生,为了使MPC850得到可靠的复位,这个延迟时间通常比要求的3μs要大一些。MODCK配置可一直固定。

(2) poreset 信号无效后(为高电平),MPC850会采样MODCK并驱动HRESET信号512个时钟周期。需要注意的是这个时间由MPC850控制的,CPLD不作逻辑实现。然后MPC850开始采样总线上的32bit配置数据。这时不能马上驱动总线数据线,应延迟若干时钟周期后驱动,经应用证明延迟8个时钟周期以上可以满足要求。

(3) 驱动总线配置数据16个时钟周期后把总线置为高阻态,上电复位结束。

手动复位的逻辑实现主要考虑的是对按键的复位作抗抖动处理,以防止多次短暂接触对系统造成反复复位,可以在代码中加入一个RS触发顺来实现抗抖。

本设计采用VHDL语言实现,限于篇幅代码省略。需要注意的是:在总线数据配置时,不能采用顺序执行语句,而只有应用并发语句执行才能得到正确的配置。如:

d <="ZZZZZZZZZZZZZZZZ"when flag=true else"0000011010100010";

--512个时钟周期后,再等待8个时钟周期将初始配置字推至数据线

--采用条件代入语句的并发描述

而如果采用顺序描述语句:

if flag =true then

d <="ZZZZZZZZZZZZZZZZ "

else

d <="0000011010100010";

则配置字将得不到正确读取。这一点需要特别注意。

3 MPC850通信的CPLD实现

3.1 MPC850 CPM的应用

MPC850的CPM模块支持7个串行通道,其中包括:2个串行管理控制器SMC(支持通用异步收发UART、透明模式和通用电路接口)、2个串行通信控制器SCC(支持Ethernet、ATM、HDLC和其它多种通信协议)、1个USB信道、1个I2C端口和1个串行外围接口SPI。

在实际应用中,可通过设置模式寄存器的相关控制位来决定各个通道应该采用的协议。各信道的接口通过MPC850的并行I/O口PA、PB和PC与外设进行连接,这些I/O口对应的协议需要对端口的引脚配置寄存器(pin assignment register)和数据方向寄存器(data direction register)进行配置,但由于端口数量的限制,所有的通信协议不可能被同时支持,因此受I/O口限制,若干协议不能同时被使用。故此,在使用这些I/O口,就存在复用和互斥的问题。表1给出了各I/O口和通信协议的对应关系。

表1 MPC850端口复用一览表

3.2 复用逻辑的CPLD实现

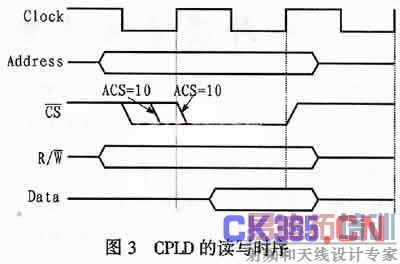

将MPC850需要复用的I/O端口全部连接到XC95144XL的可编程I/O口,然后将外部连接的各通信端口(RS232、以太网1、以太网2等)也连接到XC95144XL的可编程I/O口。这样,当MPC850需要切换到某个外部端口时,除设置内部相关寄存器外,通过数据和地址线控制XC95144XL内部的复位控制寄存器就可以完成I/O口的切换。余下的工作就是了解复用控制寄存器的结构和CPLD的读写时序。这样,通过对各位的设置就能开关相应I/O口。图3和图4分别是CPLD的读写时序和复用控制寄存器的位定义结构图。

4 总结

本文介绍了MPU和CPLD在嵌入式设计中的综合应用方法,同时提供了一种简单的实现方案,随着VLSI集成度和功能的不断增强,MPU和CPLD的结合应用远不止文中提到的这些。随着先进集成工艺和大批量生产的出现,CPLD器件的成本也不断下降,其集成密度、速度和性能也将大幅提高。另外,其CPLD器件的设计灵活性也使得它能够完成许多更多复杂的在片设计,从而极大地扩展了MPU的功能,增强了系统的易裁减特性,而这切都无颖将充分提升设计人员的创造空间。

上一篇:基于CPLD的USB总线的隔离接口实现

下一篇:基于PLC的十字路口交通灯控制系统