- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于TMS32OVC5509 DSP的FIR数字滤波器的实现

0 引言

在数字信号处理系统中,数字滤波器占有十分重要地位。而有限冲击响应(FIR)数字滤波器因其具有系统稳定、运算速度快、易实现等特点,在图像信号处理、数据传输等领域被广泛采用。FIR滤波器可以由计算机软件来实现,也可以通过专用的数字滤波电路、专用的数字信号处理器或通用可编程DSP处理器来实现。其中计算机软件实现的方法速度较慢,常用于算法的模拟及仿真;专用硬件或专用处理器实现的方法速度快,但通用性较差、成本高:而通用可编程DSP处理器可通过编程实现各种数字滤波算法,使用灵活、功能强大,在滤波器设计中被广泛使用。本文主要介绍基于TMS320VC5509可编程DSP的FIR数字滤波器的设计与实现。

1 FIR滤波器的特点和基本结构

1.1 FIR滤波器的特点

(1)系统的单位冲激响应h(n)在有限个n值处不为零;

(2)系统函数H(z)在|z|>0处收敛,在|z|>0处只有零点,有限z平面只有零点,而全部极点都在z=0处(因果系统);

(3)结构上主要是非递归结构,没有输出到输入的反馈,但有些结构(例如频率抽样结构)中也包含有反馈的递归结构。

1.2 FIR滤波器的基本结构

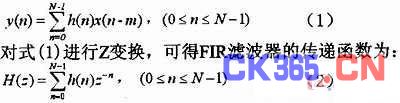

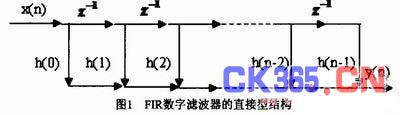

FIR滤波器的基本结构是一个分节的延时线,把每一节的输出加权累加,得到滤波器的输出。数学上表示为:

由式(2)可画出FIR滤波器的一般结构,如图1所示:

2 FIR滤波器的窗函数设计法

常用的FIR滤波器的设计方法有窗函数设计法和频率抽样设计法。窗函数法设计的基本思想是设计一个有限长滤波器频率响应来逼近理想滤波器的频率响应。设理想滤波器的频率响应为Hd(ejw),其单位抽样响应用hd(n)表示。通常选择Hd(ejw)为具有分段常数特性的理想滤波器,因此hd(n)是无限长非因果的,不能直接作为FIR数字滤波器的单位抽样响应。窗函数设计法就是截取hd(n)的一段为有限长因果序列,并选择合适的窗函数进行加权作为FIR数字滤波器的单位抽样响应。窗函数法设计线性相位FIR滤波器的一般步骤为:

(1)首先是给定所要求的频率响应函数Hd(ejw);

(2)求理想滤波器的单位抽样响应

![]()

(3)由过渡带带宽及阻带最小衰减的要求,选定窗函数w(n),并估计窗口长度N;

(4)求得所设计的FIR滤波器的单位抽样响应

![]()

(5)求FIR滤波器的系统函数

通常整个设计过程可利用计算机编程来实现,可多选择几种窗函数来试探,从而设计出性能良好的滤波器。

3 FIR滤波器的DSP实现

3.1 TMS320VC5509简介

TMS320VC5509是美国德州仪器公司(TI)推出的新一代数字信号处理器,其CPU在结构上包含一个32×16位指令缓存队列、2个17位×17位乘累16位算术逻辑单元(MAC)、一个40位算术逻辑单元(ALU)、一个16位算术逻辑单元(ALU)、一个40位桶形移位器和4个40位加法器。TMS320 VC5509支持多种工业标准的串行口,如:多通道缓冲串行口(McBSPs)、多媒体卡/安全数据串行口(MMC/SD)、USB和I2C总线接口等。还具有增强型主机接口(EHPI)、通用I/O口、可编程数字锁相环(DPLL)、计时器和多个DMA控制器等片上外设。TMS320VC5509高度并行的结构与优化的指令集合在一起,使得每个操作所需的时钟周期数在减少,而代码密度则在增加,进而提供了一个代码长度小、耗能低、高性能的数字信号处理引擎。

3.2 FIR低通滤波器的设计及实现

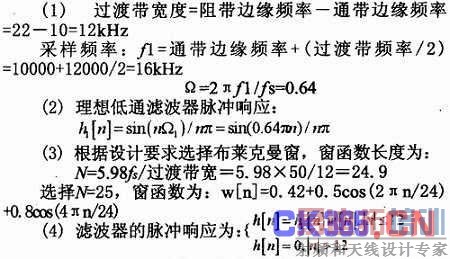

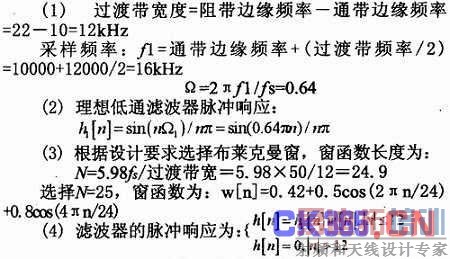

用窗函数法设计FIR低通滤波器。设计参数为通带边缘频率10kHz,阻带边缘频率20kHz,阻带衰减75dB,采样频率50kHz。

由已知参数设计FIR低通滤波器过程如下:

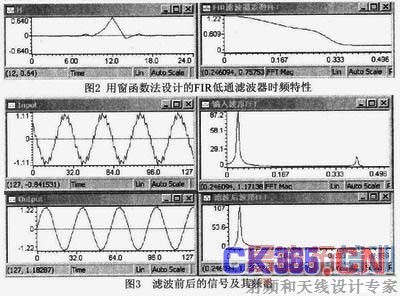

FIR滤波器的DSP实现程序采用C语言编写,滤波器时频特性如图2所示。利用设计好的FIR滤波器对叠加了高频噪声的输入信号进行滤波,滤波前后的波形及频谱如图3所示。通过时域波形的对比发现,叠加了高频噪声的输入信号经过FIR低通滤波器后,信号相对滤波前变得光滑;由频域波形对比同样可以发现有用的低频信号被保留下来,而高频噪声被很好地滤除掉了。

4 结束语

FIR滤波器可以在保证幅度特性的同时,保证严格的线性相位,在数字信号处理系统中被广泛使用。而DSP芯片具有强大的数字信号处理功能和丰富的指令集系统,用DSP实现数字滤波既能满足系统准确性、稳定性的要求,同时又具有实时性、灵活性的特点,在语音、图像处理和数据传输等领域具有广泛的应用前景。

上一篇:基于DDS的励磁恒流源设计

下一篇:某型无人机信息系统字符叠加模块设计