- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于LPM的高速FIFO的设计

1引言

当今电子系统的复杂程度越来越高,手工设计已经无法完成,必须依靠现代电子设计技术。现代电子设计技术的核心是EDA(electroNIc design automation),就是利用计算机,在EDA工作平台上,利用硬件描述语言(例如VHDL),完成逻辑编译、逻辑化简、逻辑综合、仿真测试、布局布线等设计工作,完成对系统硬件功能的实现。

在基于EDA技术的电子系统设计中,如果能够直接调用参数可设置模块库(Library of Parameterized Modules,简称LPM)中的兆功能块,则可以大大提高系统设计的效率和可靠性。设计者可以根据实际系统的需要,在LPM中选择库中的适当模块,对其参数进行必要的调整设置,使其符合自己的要求,将已有的设计模块为己所用。

2. 兆功能块的编辑方法

FIFO意思为First In First Out (先进先出),是一种存储器参数可设置模块库,在高速数字系统中常用作缓存。在高速数据传输和实时显示领域中,需要对数据进行快速储存和发送,要实现快速的数据采集、顺序储存和传送,传统的RAM型存储器已经无法满足要求。目前许多高速系统都采用了FIFO作为缓存体。因为FIFO的写入(读出)时间只需要一个时钟周期,不需要对地址进行加1操作,大大提高了存储速度。下面利用LPM中的兆功能块LPM-FIFO,设计一个高速FIFO元件。

LPM库中的兆功能模块有许多种,例如LPM-ROM、LPM-RAM、LPM-FIFO。可以根据需要,调用其中的某一种。例如要设计高速FIFO元件,则选择LPM-FIFO作为以VHDL描述的设计项目中的一个元件,首先利用MAX+PLUS内自带的兆功能块处理器,根据需要对所使用的兆功能块的参数进行适当的调整,由此生成一个满足自己特定需要的模块。最后,利用例化语句,在顶层设计中调用该模块。具体步骤如下:

进入MAX+PLUSⅡ后,在file下进入LPM元件定制器界面,选择storage中的LPM-FIFO元件,然后根据需要修改该元件的参数:

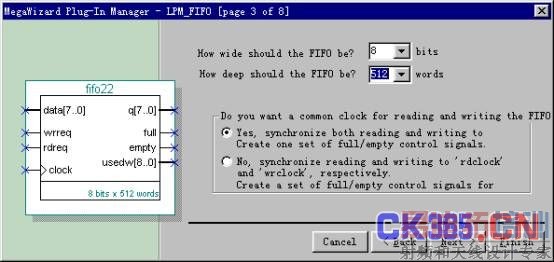

(1)图1,数据宽度为8位,深度为512,即设置此FIFO的存储容量为8*512bit。与clock同步的数据写入wrreq和数据读出rdreq。

图1

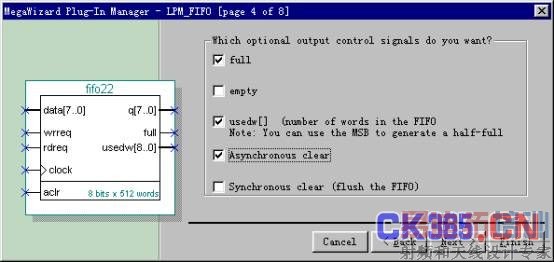

(2)图2,异步清零信号aclr,当此信号有效时, FIFO 清零。存储数据溢出信号full,当FIFO中数据满时,此信号有效。

图2

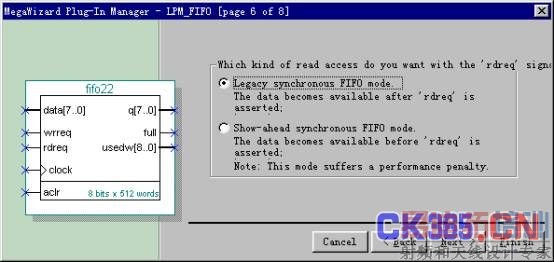

(3)图3,选择数据读出方式:在读请求信号rdreq有效后数据输出。

图3

(4)图4,选择面积优化方式:Area,即要求综合器和适配器更有效地利用逻辑资源而忽略电路速度的约束。

图4

最后单击finish 完成参数的定制,文件以fifo22.vhd名保存。

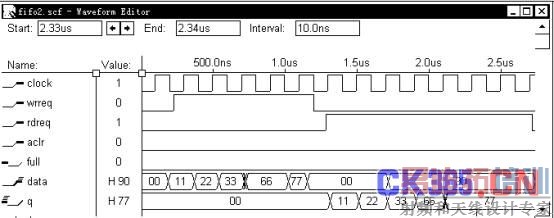

3. FIFO波形仿真测试

对于刚刚制定的元件,必须进行仿真测试,从其工作波形上了解其工作特性。从图5波形可以看出,当写入信号wrreq为高电平时,在clock的每一个上升沿,将data的数据写入;在wrreq为低电平,读出信号rdreq为高电平时,在clock的每一个上升沿,将刚刚写入的data的数据按照先进先出的原则从q读出。波形表明时序已经满足要求。Clock频率设置为50MHz,也达到高速的要求。

图5

4. FIFO的VHDL调用

完成了FIFO的定制和波形测试后,就可以在某个电子系统的设计中将其当作一个元件来调用。调用方法有逻辑电路原理图调用和VHDL调用两种。这里使用VHDL的元件例化语句,在某一电子系统的顶层设计中调用该模块。

元件例化就是引入一种连接关系,将预先设计好的FIFO定义为一个元件,利用特定的元件例化语句将此元件输入输出端口与系统中的其他元件端口之间的关系描述出来。元件例化语句由两部分组成,第一部分是对要调用的元件做出声明,称之为元件定义语句。例如要调用刚刚设计的FIFO22元件,则用下面语句做出声明:

COMPONENT FIFO22

PORT (DATA: IN STD_LOGIC_VECTOR(7 DOWNTO 0);

WRREQ,RDREG,CLOCK,ACLR: IN STD_LOGIC;

Q: OUT STD_LOGIC_VECTOR(7 DOWNTO 0);

FULL : OUT STD_LOGIC);

END COMPONENT;

由关键词COMPONENT 语句声名,PORT内主要对FIFO22元件的输入和输出端子进行说明,相当于对一个现成的LPM模块进行封装,成为一个只有输入输出端口的元件。就像一个芯片,对外来看,只有几个引脚。

元件例化语句的第二部分说明此元件与当前系统中的其他部分之间的连接情况:

U2 : FIFO22 PORT MAP (DATA=>D,WRREQ=>WR_EN,RDREG=>C1, CLOCK=>A1,ACLR=>CLR,FULL=>FULL,Q=>Q);

其中,U2为例化名,它类似于标在当前系统的一个插座名,元件名FIFO22则是准备在此插座上插入的已经制定好的LPM模块。PORT MAP是端口映射的意思,其中的端口名是在上面的元件定义语句中的端口名表中定义过的元件的端口的名字,相当于插座上各插针的的引脚名。

最后对整个系统的进行综合适配、仿真测试和编程下载即可。

5. 结束语

LPM库中的功能模块是许多优秀的电子工程设计人员的硬件设计成果,其种类丰富,方便实用。每一种模块的功能、参数的含义、使用方法、VHDL语言的参数设置和调用方法都可以在MAX+PLUSⅡ中的help中查出。我们可以根据需要选择LPM模块,进行参数的修改和调整,充分利用已有的设计成果来完成自己的电子设计,大大提高工作效率。