- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

波特率自适应的RS-485中继器设计

引 言

RS-485收发器采用平衡发送和差分接收,因此具有抑制共模干扰的能力;加上接收器具有高灵敏度,能检测低达200 mV的电压,故传输信号能在千米以外得到恢复。使用RS-485总线,一对双绞线就能实现多站联网,构成分布式系统,且设备简单、价格低廉,能进行长距离通信,因而得到了广泛的应用。由于在双绞线上的电平损耗,RS-485标准通信的最大传输距离是1 200 m,因此更远距离的应用中必须使用中继器。网络节点数与所选芯片驱动能力和接收器的输入阻抗有关。RS-485标准规定了最大总线负载为32个单位负载,若应用中总线负载大于32个单位负载则必须使用中继器。

1 RS-485中继器原理

RS-485是半双工方式,两线双向传送差分信号,具有多点、双向通信能力,即允许多个发送器和接收器连接到同一条总线上,传输线上信号的传输方向不定。因此,识别和控制好传输线上的信号传递方向是设计RS-485中继器的关键。

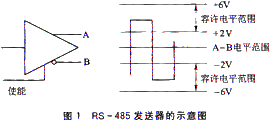

RS-485标准规定:数据信号采用差分传输方式(differential drivel mode),也称为“平衡传输”。它使用一对双绞线,将其中一根线定义为A,另一根线定义为B,如图1所示。

通常情况下,RS-485发送器A、B之间的正电平在+2~+6 V,是一种逻辑状态;负电平在-6~-2 V,是另一种逻辑状态。在RS-485发送器件中,一般有一个“使能”控制信号,用于控制发送器与传输线的切断和连接。当“使能”端为低电平时,发送器输出处于高阻状态,称作“第三态”。它是有别于逻辑“1”与“0”的第三种状态。

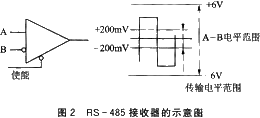

对于RS-485接收器,也作出与发送器相对的规定,收、发端通过平衡双绞线将A-A与B-B对应相连。当在接收端A、B之间有大于+200 mV的电平时,输出为正逻辑电平;小于~200 mV时,输出为负逻辑电平。在接收器的接收平衡线上,电平范围通常为200 mV~6 V,如图2所示。

RS-485接收器同样定义逻辑1(正逻辑电平)为B>A的状态,逻辑0(负逻辑电平)为A>B的状态,A、B之间的压差不小于200 mV。在。RS-485接收器件中,一般也有一个“使能”控制信号,用于控制接收器与传输线的切断和连接。当“使能”端为高电平时,接收器与传输线切断,接收器输出为高电平;当“使能”端为低电平时,接收器输出电平与总线信号的逻辑电平一致。

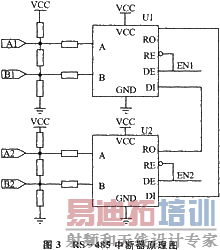

RS-485中继器原理图如图3所示。正常工作时主要有三个状态:空闲状态,数据从RS-485收发器U1边的总线往RS-485收发器U2边的总线传送(简称“数据右传状态”),数据从RS-485收发器U2边的总线往RS-485收发器U1边的总线传送(简称“数据左传状态”)。

(1) 空闲状态

当中继器上电启动运行或总线上没有数据传送时,中继器工作在空闲状态。RS-485收发器U1、U2均为接收数据状态,U1、U2的EN1、EN2引脚均为低电平。

(2) 数据右传状态

当RS-485收发器U1边检测到连接其A、B引脚总线上的差动信号有数据向右边传送时,它通过RS-485收发器U1的RO引脚以RS-232的方式逐位接收数据,并通过。RS-485收发器U2的DI引脚以RS-232的方式逐位输出数据。传送顺序为先传一个低电平起始位,再传8位数据位,最后传1位高电平结束位,为一数据帧,此段时间U2的EN2引脚应为高电平。此后U2将一直输出高电平直到下一帧数据到来之前,U2的EN2引脚也应为低电平且处于接收状态。

(3) 数据左传状态

数据左传状态的过程与数据右传状态一致,只是在一数据帧时间段内U2的EN2引脚应为高电平。

当总线上干扰较大时也有可能发生总线冲突,数据右传状态和数据左传状态同时发生。此时,总线上的信号是无效的,但总线冲突(总线双方同时活动)并不需要中继器来处理和解决,而是由通信协议来处理和防止的。要求总线冲突(或干扰)结束后,RS-485中继器的方向控制器总能自动恢复正常工作。

2 几种RS-485中继器

现有的RS-485中继器通常采用三种方法来实现:①采用RC充放电延时与RS触发器的配合来控制RS-485芯片的数据收发方向;②采用单片机的定时器定时控制RS-485接口收发方向;③采用单片机串口监视总线上的数据,通过查表当数据送给本中继器下的终端时才开启数据传输通道。

第一种方法的缺点是采用电阻、电容组成延时电路。由于电阻或电容本身的误差,运行一段时间后电子器件老化产生的误差以及温度的变化,都会影响延时的准确性,而且这种中继器要求两个字节之间的通信时间间隔必须大于一个字节数据的通信时间才能确保不丢失数据,因此降低了通信速率。

第二、三种方法的缺点是采用单片机的中断来检测数据帧的起始位。单片机的中断响应须要一段时间,RS-485总线一个数据位的时间宽度应大于单片机的中断响应时间,终端处理器才能检测每数据帧的起始位,所以此两种方法的通信速率也受到限制。特别是第三种方法中,单片机要通过对总线上通信内容的监听进行相应查表来决定本中继器后面的总线是否与前面的总线连接。这种方法的缺点是要对总线的通信内容进行处理,这不仅降低了通信的实时性,而且还增加了系统通信协议的复杂性,降低了RS-485总线通信的可靠性。

3 波特率自适应RS-485中继器

在工业现场应用中,RS-485总线的通信速度一般为2 400~115 200 bps,以前设计的RS-485中继器控制RS-485收发器收发状态,以一数据帧时间宽度为单元。不同的波特率,控制RS-485收发器收发状态的时间宽度也不同,所以RS-485总线的通信速度不同,需设置控制RS-485收发器收发状态的时间宽度,以适应所应用RS-485总线的通信速度。

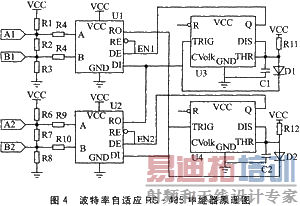

波特率自适应RS-485中继器的设计思路是:控制RS-485收发器收发状态,以一数据位时间宽度为单元。若控制RS-485收发器收发状态时间宽度适应任意波特率的一数据位时间宽度,则RS-485中继器适应任意RS-485总线的通信速度。为此设计波特率自适应RS-485中继器,如图4所示。

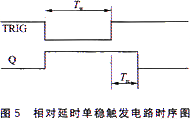

U3、U4为由CA555组成的相对延时单稳触发电路,分别控制RS-485中继器数据左、右传状态。相对延时单稳触发电路是在由CA555组成的普通单稳触发电路的基础上增加了二极管D1和D2。当CA555输入引脚TRIG为低电平时,CA555内部和二极管D1、D2将RC延时电路放电,输出Q端输出高电平;当CA555输入引脚TRIG变为高电平时,CA555内部和二极管D1、D2开始使RC延时电路充电,延时一段时间(与R×C有关),输出Q端输出低电平。其输入、输出信号时序如图5所示。

图5中,TRIG为CA555的输入信号;Q为CA555的输出信号;Tw为单个或连续低电平数据位的时间宽度;Trc为U3、U4组成的单稳触发电路中R11×C1(或R12×C2)决定的延时时间宽度,选择小于RS-485总线最高波特率(如115 200 bps)的数据位的时间宽度为宜。在本设计中,控制RS-485收发器收发状态的时间宽度始终比总线中传输数据低电平宽度大Trc,而且Trc不会大于任何波特率的一个数据位的时间宽度。所以本文设计的波特率自适应RS-485中继器适应于工业现场应用RS-485总线的任意通信速度。

由于波特率自适应RS-485中继器以一数据位时间宽度为单元,所以只有传输低电平数据位时,输出端RS-485收发器的输出使能才打开,并输出低电平。当传输高电平数据位时,输出端RS-485收发器的输出使能关闭,RS-485收发器的输出为高阻状态。所以,在每端RS-485收发器的输出端需增加上拉电阻、下拉电阻和匹配电阻构成的偏置电路,当输出为高阻状态时,在匹配电阻上形成表示高电平的差分信号并输出。

为提高波特率自适应RS-485中继器的可靠性,可将U3的输出端经一反相器与U4的低电平有效的复位端R连接;将U4的输出端经一反相器与U3的低电平有效的复位端R连接。这样,当从RS-485中继器的一侧向另一侧传输数据时,消除了同时向相反方向传输数据的可能性。

当总线上干扰较大时也有可能发生总线冲突,数据右传状态和数据左传状态同时发生。由于实际电路的不完全对称,波特率自适应RS-485中继器只能向一个方向传输数据,并且当总线冲突(或干扰)结束后,中继器处于空闲状态,即中继器两端的收发器均处于接收状态。

4 结 论

本文提出了由CA555组成的相对延时单稳触发电路,并应用于RS-485总线中继器的设计中。它使得RS-485收发器的数据发送状态只由RS-485中继器接收数据端数据的一个或连续多个低电平位来控制,与一数据位时间宽度无关,即与总线传输数据的波特率无关,所以本文设计的RS-485总线中继器自适应任何波特率数据的RS-485总线中继传输。实践证明,该波特率自适应RS-485中继器是可靠的。

上一篇:单片机测试系统的数据存储和管理

下一篇:CSP热连轧组织性能预报数据库的建立