- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的矩阵乘法器优化设计

0 引言

由于具有并发式的硬件结构,FPGA在进行并行计算和多通道数据处理方面具有不可替代的优势,因此在阵列信号处理、图象处理和通信信号处理等许多应用领域,FPGA正被越来越多的使用,它可以被灵活的设计成各种功能模块,如在通信系统中被设计为数字滤波器,在图象处理系统中用于3D图形变换,在阵列信号处理中用于求解信号协方差矩阵的特征值等等。在很多应用中,FPGA的功能都与矩阵的计算与变换有关,很多矩阵计算都可以用并行的计算结构实现,并且运算的并行程度越高,相应的系统性能也就越好,但是提高并行运算的并行度,就需要在FPGA中设计更多的基本运算模块,相应的硬件资源占用也就越大。因此,在FPGA的硬件资源有限的情况下,如何用更少的硬件资源实现更多的运算功能就成为提升系统性能的关键。

新一代的FPGA在硬件结构上为其在信号处理领域的应用做了很大的改进,如嵌入了专用高速数据收发通道、硬件乘法器、专用DSP单元、DCM模块和片内RAM等。本文将以3×3矩阵乘法器的设计实现为例,详细介绍如何使用DCM模块和硬件乘法器等资源,对矩阵基本运算在FPGA中的设计实现进行优化,从而最大限度的提高硬件资源的使用效率。

1 DCM简介

DCM是新一代FPGA中嵌入的高级时钟模块,为高频高性能应用提供了以下功能:

1)产生输入时钟的倍频或分频,或者通过倍频和分频生成一个全新频率的时钟。

2)按要求修正时钟,如将时钟占空比修正为50%。

3)对时钟信号进行精确相移。

4)消除时钟传输延迟,对FPGA内部或外部器件的时钟传输延迟都可进行消除,以提高整个系统的性能。

5)镜像或缓冲时钟信号,可以将输入时钟转换成不同的I/O标准信号,如将LVTTL时钟转换成LVDS。

如图1所示,DCM在结构上由四个功能单元组成,各功能单元可以单独操作或协同使用。

图1 DCM功能结构图

各模块与其主要功能为:

DLL(delay-locked loop):延迟锁定环单元,可以产生零传输延迟的时钟输出信号,它通过监控CLK0或CLK2X信号来补偿输出时钟在传输中产生的延迟。

DFS(digital frequency synthesizer):数字频率合成单元,通过设定不同的倍频与分频系数大小,DFS可以在很宽范围内提供可选频率的输出时钟。DFS和DLL可以同时使用也可单独使用,如果DLL没有使用,那么DFS的输出时钟CLKFX和CLKFX180与输入时钟CLKIN不存在相位关系。

PS(phase shift):相移控制单元,控制DCM的所有输出时钟与输入时钟CLKIN的相位关系,相移值在设计时就已设定并在FPGA加电配置时被加载到DCM中。

Status logic:状态逻辑单元,通过LOCKED和STATUS信号显示出DCM现在的状态,LOCKED信号显示DCM的输出信号是否和输入时钟CLKIN存在相位关系,STATUS信号显示DLL和PS操作的状态。

2 矩阵乘法器设计

2.1 矩阵乘法分解

下列等式显示3×3矩阵乘法的具体操作过程,完成一次3×3矩阵乘法需要进行27次乘法运算和18次加法运算。

从下式可以看出矩阵乘法的一个子系统可以表示为矩阵与向量的乘积:

由三个这样的运算子系统组合运算或由一个子系统执行三次运算都可以完成一次3×3矩阵乘法。

2.2 矩阵向量乘法子系统的设计

在进行硬件设计时,我们让某些硬件单元(如乘法器、加法器和寄存器)工作在高于系统时钟频率的频率下,这样在一个系统时钟周期里,我们可以向这些单元发送多组数据并获得多组结果,从而提高这些硬件资源的使用效率。以矩阵向量乘法器为例,传统设计需要9个乘法器和6个加法器的硬件资源才能在最短时间完成运算,我们对设计进行优化时,使硬件乘法器和加法器工作在9倍系统时钟频率下,配合一定的寄存器和控制单元,可以保证在不增加运算时间的前提下,将完成一个矩阵向量乘法子系统需要的乘法器数量从9个降到1个,加法器数量也从6个降到1个。图2显示了优化后的矩阵向量乘法器结构图,其中9xCLK时钟由DCM模块提供,子系统输出结果由下式决定:

2.3 数据流程

如图2所示,硬件乘法器输出数据被送到加法器的A输入端,从加载数据开始,要经过3个时钟周期,第一个有效的乘法器输出数据才能送到加法器的A输入端。加法器的B输入端接0或是累加寄存器,如果B端接0,那么乘法器输出数据将被直接送到累加寄存器,如果B端接累加寄存器的输出,那么以前的累加结果将和乘法器输出结果相加后送到累加寄存器,而B端的数据选择开关可以由计数器Cntr3的输出信号控制,使得第一个有效乘法结果到达加法器A输入端时选择输出0,第二第三个有效数据到达时选择累加寄存器,之后按三个时钟周期一个循环进行。

图2 优化后的矩阵向量乘法器结构示意图

在Reset之后的第6个周期,有效的X的值出现在累加寄存器的输出端,这之后每过3个周期Y、Z、X、Y、Z的有效值将循环出现。在设计时使用两个输出控制计数器Cntr3_out和Cntr9_out控制计算结果的送出,在系统Reset以后,Cntr3_out从0计数到3并保持,Cntr9_out要等待Cntr3_out计数到3后才开始循环计数,并分别在计数到3、6、9时控制更新X、Y、Z的输出值。

主要寄存器的输出数据流时序在表1可以清楚的显示。

表1 矩阵向量乘法器数据流时序

3 设计仿真与实现

3.1 功能仿真

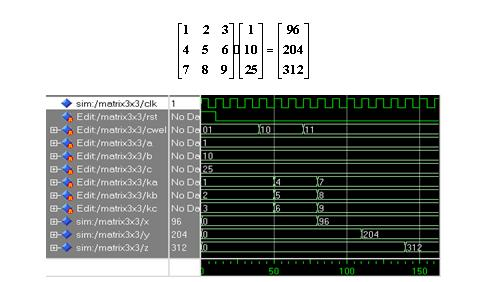

根据图2所示结构图进行各个进程模块设计,设计结果在Modelsim6.0环境下进行功能仿真,仿真结果如图3所示,其中为系统设定的输入矩阵向量乘积表达式为:

图3 矩阵向量乘法器功能仿真图

可以看出,功能仿真结果与理论值完全一致,从而成功的将功能结构设计转换为硬件描述语言设计,下一步就可以进行硬件的综合实现了。

3.2 综合实现

本设计的实现平台使用Xinlix公司Virtex4系列的XC4VLX25芯片,综合布线工具使用ISE 8.2i,布线后的时间性能分析显示如表2所示,矩阵向量乘法器子系统的工作频率可以达到175MHz以上,那么系统的工作频率能达到20MHz左右,流水线的工作模式使其能够满足绝大多数信号处理系统对数据处理速率的要求。

表2 时间性能分析结果

我们还在同样的平台上使用传统设计方法实现了3×3矩阵向量乘法器,表3给出了两种设计方法所占用的硬件资源,通过比较我们可以看出,优化后的设计比优化前多使用了一些寄存器与组合逻辑资源,但大大节省了关键的专用DSP单元的使用量,为芯片提高计算并行度留足了余量。

表3 优化前后硬件资源使用情况

4 结论

通过3×3矩阵乘法器优化设计的实现结果,我们可以看出,通过综合应用FPGA中的DCM和嵌入式乘法器等功能模块,我们可以在设计矩阵运算功能时,极大的提高硬件资源的使用效率,从而进一步提高系统性能,并且这种设计方法可以在关于矩阵的其它运算与变换功能的实现中应用。

参考文献

[1] Xilinx Corporation. ISE 8.2i In-Depth Tutorial[Z]. 2006.

[2] Xilinx Corporation. Using Digital Clock Managers (DCMs) in Spartan-3 FPGAs[Z]. 2006.

[3] Xilinx Corporation. Using Embedded Multipliers in Spartan-3 FPGAs[Z]. 2003.

[4] LATHA P. Matrix Math, Graphics, and Video[Z]. Xilinx Corporation, 2001.