- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA控制的温度检测无线发射接收系统

摘要:本文介绍基于FPGA控制的温度检测无线发射接收系统。本系统采甩EPlKl000C208-3作为控制核心,系统比较温度是否超出人体最佳温度范围,如果过高则发出降温信号,如果过低则发出升温信号;得出需要加温还是降温的信号后通过无线将信号发射到接收电路,接收电路接收到编码过的信号后对信号解码,最终再得到加温还是降温信号,再将此信号加上驱动放大后则可以驱动步进电机等(本设计用发光二极管代替步进电机)。本设计应用了FPGA技术、温度传感技术、无线发射和接收技术,具有集成度高,测量数据精度高、性价比高等特点。具有较强的实用价值和广阔的市场前景。

O 前言

随着社会节能环保意识的增强,人们越来越重视能源的利用效率。传统的暖气控制都是利用锅炉烧出蒸汽或热水,通过管道输送到建筑物内的散热器中,散出热量,使室温增高。但是这种设备控制中心和客户端不在同一个地方,这样就存在着一种控制中心不了解客户的情况。存在着暖气开得过大或者过小,从而导致客户温度过低或过高而浪费了能源!

以前大多温度控制系统都是用单片机控制的,但是随着FPGA的迅速发展,应用也越来越广。本人将设计出一套由FPGA独立控制的、智能化的远程温度控制系统。由一个放置于客户端的温度采集系统采集到客户端温度(可排除工程中热损失),当大于或小于人体最佳温度区时发出报警信号,由控制端去控制是应该加温还是降温,从而达到节能的作用。

1 数字温度传感技术

1.1 数字温度传感器原理

数字温度传感器LM75A是一个使用了内置带隙温度传感器和∑-△模数转换技术的温度-数字转换器。简化框图如图1所示。

它也是一个温度检测器,可提供一个过热检测输出。LM75A包含许多数据寄存器:配置寄存器(Conf),用来存储器件的某些配置,如器件的工作模式、OS工作模式、OS极性和0S故障队列等;温度寄存器(Temp),用来存储读取的数字温度,器件通过2线的串行I2C总线接口与控制器通信。LM75A还包含一个开漏输出(OS),当温度超过编程限制的值时该输出有效。LM75A有3个可选的逻辑地址管脚,使得同一总线上可同时连接8个器件而不发生地址冲突。

LM75A可配置成不同的工作条件。它可设置成在正常工作模式下周期性地对环境温度进行监控或进入关断模式来将器件功耗降至最低。OS输出有2种可选的工作模式:OS比较器模式和OS中断模式。OS输出可选择高电平或低电平有效。故障队列和设定点限制可编程,为了激活OS输出,故障队列定义了许多连续的故障。

温度寄存器通常存放着一个11位的二进制数的补码,用来实现0.125℃的精度。这个高精度在需要精确地测量温度偏移或超出限制范围的应用中非常有用。

正常工作模式下,当器件上电时,OS工作在比较器模式,温度阈值为80℃,滞后75℃,这时,LM75A就可用作一个具有以上预定义温度设定点的独立的温度控制器。

1.2 温度传感器控制原理

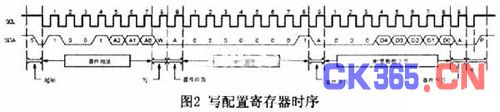

如果将温度传感器设定为正常工作模式,那么首先要向配置寄存器写入控制字告诉器件的工作模式。写配置寄存器时序如图2所示。

写配置寄存器首先要选择器件的地址,即A0-A2设置与硬件地址A0-A2一样。然后是写入配置寄存器地址指针,配置寄存器指针为”0000-000l”。等待器件应答一个SCL周期,再写入工作模式控制字。如果设置在正常工作模式下,OS设置为比较输出,那么配置数据字应写入”00000000”。

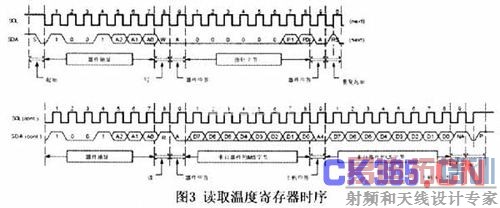

写入配置寄存器控制字”00000000”后温度传感器工作在正常工作模式下,即每一段时间温度传感器将温度转换成数字信号存放在温度寄存器里,所以只需要将温度寄存器的数据读出再加以计算即可以得到温度数据。读取温度寄存器的时序如图3所示。

读取温度寄存器时首先是选中器件,地址信号应该与硬件设置地址一致。第二段是选择温度寄存器,温度寄存器指针地址P1-P0写入”0-0”,表示下次操作的默认寄存器为器件的温度寄存器。重新起始后再次选中器件并读取温度寄存器的十六位的温度数据,并将十六位的数据的有效数据前十一位提取出,即可得到有效的温度数据。将温度数据与预设的温度比较后得出升温或降温信号,连接到无线发射模块的KEYl、KEY2上发射到接收端。接收端接收到信号后再经过放大后便可驱动步进电机等。

2 时序的实现方法

FPGA与其它逻辑语言的运行有很大区别,最大的区别就是FPGA是硬件语言,而不是类似于c语言的程序。VHDL下载后生成的是逻辑硬件电路,不是控制器控制执行的逻辑语句。VHDL语言每个进程之间是并行运行的,但是进程内部的语句却又是顺序执行的。而且每个信号的传输都是在所在进程结束的时候进行的。这点很重要,比如你对一个信号前后两次赋值,哪怕你中间有很多运算最终的结果还是最后一次赋值的结果,前一次赋值将是无效的,且会在报告中弹出一个警告。每个process的运行是靠敏感信号触发的,敏感信号放在process后面的括号中。所以对于VHDL语言来说循环语句不是很必要的,因为每次敏感信号变化该进程将从程序的第一句开始重新运行一次。意味着一个进程本来就是一个循环,只有变化的部分的信号才能得到改变。这一点与普通逻辑语言有很大的区别。

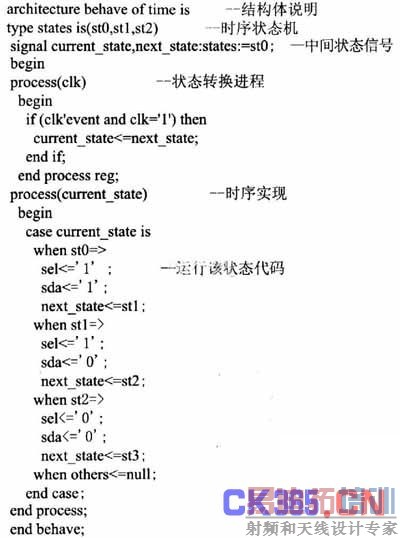

对于时序的实现有很多方法,可以用case语句实现,也可以用if语句实现。但是最有效和合乎逻辑的方法是用状态机实现。以下是状态机的模型。

状态机逻辑清晰,在每个对应的状态下将每个信号应该进行的操作放在对应的状态机程序中,严格控制各个信号的时序要求则可精确地实现高速控制。而且比单片机具有更高的速度。

3 无线收发模块

3.1 无线收发硬件原理

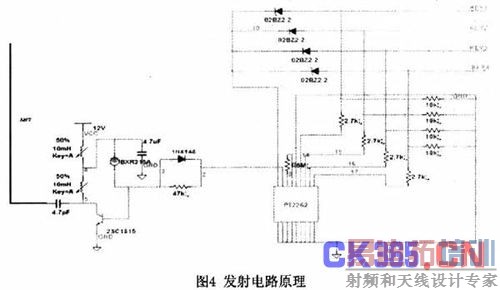

如图4所示,无线发射模块PT2262将来自10-13管脚的按键信号编码后在17管脚上输出。PT2262的17管脚的信号由同步码、地址码、数据码组成。17管脚输出信号经过R315A芯片AM调制后输出到天线上。每组数码连续发射四次,只有两次得到的数码一样以后才把相应数据位输出高电平。为了保护高频设备,本设计采用间歇发射的方式,即每3s发射一下信号,然后停止1s。目的是为了保护高频设备,避免其一直处于一种工作状态而降低其寿命。

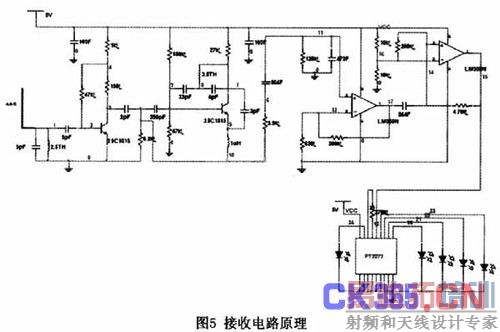

接收电路如图5所示,接收端将天线接收到信号经过两级三极管放大以后再经过一级同向放大,最后将放大信号经过比较以后,输出到PT2272芯片的14管脚,如果没有受到外部干扰,PT2272的14管脚的信号与PT2262的17管脚的信号是一致的。PT2272内部将接收到的信号解码后得出数据码,并在相对应的输出管脚输出高电平。如果输出的信号有效,那么在2272的17管脚将输出一个高电平有效的信号,表示输出信号是有效的。

3.2 无线发射信号原理

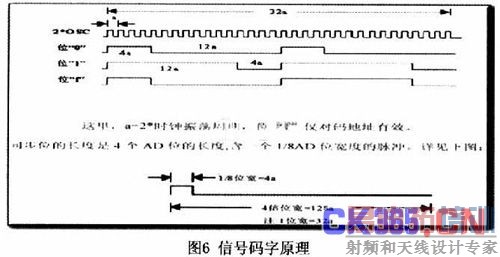

发射数据分为三部分,第一部分是地址码,第二部分是数据码,最后一部分是同步码。即在每一段数据后边都有一个定位信息。每个AD码为占32a。地址码和数据码都用宽度不同的脉冲来表示,两个窄脉冲表示”O”;两个宽脉冲表示”1”;一个窄脉冲和一个宽脉冲表示”F-”,也就是地址码的”悬空”。

发射的数据是一个字码由12位AD码(地址码加数据码,比如8位地址码加4位数据码)组成。2262每次发射时至少发射4组字码,2272只有在连续两次检测到相同的地址码加数据码才会把数据码中的”1”驱动相应的数据输出端为高电平和驱动VT端同步为高电平。

因为无线发射的特点,第一组字码非常容易受零电平干扰,往往会产生误码,所以程序可以丢弃处理。接收端接收到升温或者降温信号后可以控制步进电机等驱动电路工作去控制暖气系统升温和降温。

上一篇:基于USB接口1553B总线设备检测系统设计

下一篇:基于FPGA的

像预处理系统