- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于GAL的VME总线接口电路及程序设计

摘

1 引言

VME 总线由于具有良好的物理特性、严格的技术规范和与微处理器接口灵活的特点而 被广泛应用于雷达、声纳等大规模并行多处理器系统[1],在国内外船舶机舱自动化控制系统 中也有成功应用。用户在开发基于VME 总线的信号采集模块时,首先必须考虑和解决的是 与VME 总线的接口问题。本文采用基于GAL 芯片实现VME 总线接口电路的思路,对VME 总线接口设计问题进行了深入研究。文中通过软件技术实现了VME 总线地址的译码以及数 据读写与中断逻辑控制,有效简化了硬件电路的设计。

2 接口设计功能要求

根据 VME 总线规范和本题具体任务需求,本文设计的VME 总线接口电路为一从控设 备接口电路(Slave Interface),接口的数据总线宽度和地址总线宽度均为16 位。主要接口功 能要求如下:

1)产生电路板本身的程序复位和硬件复位信号;

2)产生I/O 读、写信号及数据总线接口芯片片选信号;

3)产生与VME 总线的应答信号、数据选通信号,控制数据传送方向;

4)具有中断请求功能:可设定的中断请求级;可编程中断向量;支持中断响应菊花链。

3 主要接口电路设计与功能实现

3.1 接口设计原理

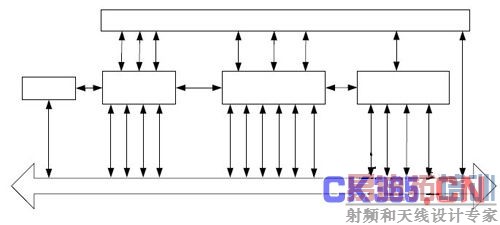

通过比较研究,本文选用 Lattice 的通用阵列逻辑(GAL)芯片来完成接口逻辑电路设 计。GAL 芯片是Lattice 公司开发的电可擦写、可重复编程的PLD,具有结构简单,易于编 程等优点。本文采用3 片GAL 芯片进行接口逻辑电路设计,电路基本结构及原理如图1 所 示。图中2 片GAL20V8 完成地址译码和读写控制,1 片GAL16V8 完成中断请求控制,数 据接口采用通用总线接口芯片Z8536。Z8536 是一种带有两个8 位I/O 口、通用可编程的总 线接口芯片。通过对控制寄存器进行配置,可将这两个I/O 口作为两路8 位信号通道,或共 同构成一路16 位信号的通道。在本设计中,GAL 芯片将VME 总线*问Z8536 的信号进 行译码,再通过LA4 和LA5 对Z8536 各个接口及工作方式配置寄存器进行选择。VME 总 线借助Z8536 即实现对该从板上8 位或16 位数据的读写。

图1 电路基本结构及原理

3.2 地址译码和读写控制电路设计与功能实现

地址译码电路要实现的主要功能是当主设备发出的地址有效信号AS*有效时,自动从 总线上获取地址和地址修饰码,然后根据地址修饰码配置本次地址传送的方式,再根据地址 发出相应的片选信号选择板上芯片。读写控制模块的主要功能是通过读写周期时序内产生的 DS0*、DS1*、WRITE*、LWORD*、IACK*等信号正确配置数据传送的形式,控制板上的 I/O 芯片的读写,并发出DTACK*信号还原主设备[2]。

为满足以上要求,地址译码芯片上的CE[3~0]分别接4 片Z8536 总线接口芯片的使能端; 读写控制芯片上的RD 和WR 分别接Z8536 的读写使能端。通过这两块芯片,实现了VME 总线对该从板上各路信号的读写进行的控制。

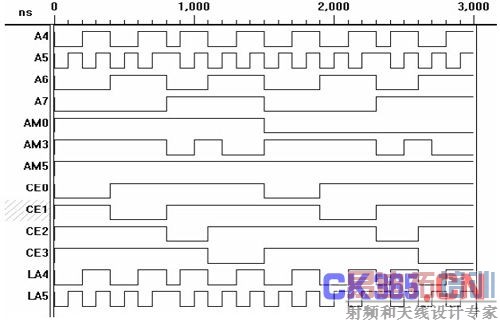

由以上分析及逻辑推理确定了 GAL 芯片要实现的功能以后,根据总线协议和硬件电路 即可得到相关信号之间的逻辑关系,本文据此完成了相应ABEL-HDL 程序编写并利用 Lattice 公司的专用开发工具ispLEVER5.1 对GAL 芯片程序进行了编译和仿真调试,其地址 译码控制过程仿真波形如图2 所示。

图 2 地址译码控制过程仿真波形

3.3 中段请求控制电路设计与功能实现

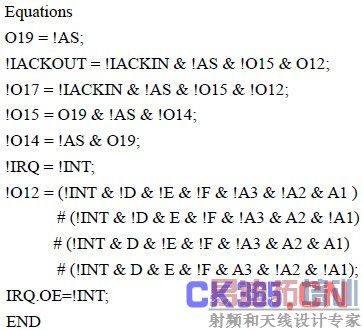

VME 优先级中断机制采用菊花链,它用于在板与板之间传送一电平信号。它始于第一 槽而终结于最后一槽。系统可以提供IRQ 1 ~IRQ7 共7 个中断请求,其中IRQ7 具有最高优 先级。本文采用通过跳线设定优先级的方法。当中断处理器处理中断请求时,中断应答菊花 链驱动器启动中断应答菊花链工作,以确保只有一个中断器响应正在进行中的中断应答周 期。当主设备应答某个中断时,首先把IACK*信号驱动为低,表示当前周期是中断应答周 期,同时将相应的中断请求级别值放到A01~A03 上。而中断响应主要由中断响应输入 (IACKIN*)和中断响应输出((IACKOUT*)组成应答菊花链。若某一从设备发出中断请求,并 且响应的中断识别码和自己匹配,同时接到上一级传下来的有效的IACKIN*信号,则判断 是自己的中断响应,应该堵塞IACKOUT*信号,使之为高电平,否则应该继续下传 IACKOUT*信号[3]。根据上述的VME 总线中断处理机制和过程,可以设计出在Slave 模式 下,从设备通过GAL 芯片申请中断的控制逻辑。中断控制逻辑部分的ABEL-HDL 源程序 如下:

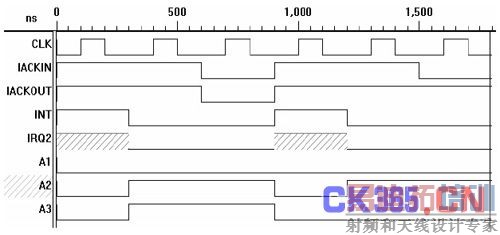

图 3 是该程序在ispLEVER5.1 中的仿真波形图。在该图中,从设备板上的Z8536 通过 将INT 拉低请求一个权限为IRQ2 的中断,译码识别代码为010。由图可见,当A[3~1]为 010 时,菊花链停止传送,否则由IACKOUT 传出。

图 3 中断请求控制仿真波形

4 结语

目前基于上述接口电路的VME 总线I/O 接口板卡设计研制工作已完成,并已成功应用 于机舱自动化控制系统原理样机中。试运行以来稳定可靠,表明本文设计思路方法可行,电 路及程序实现达到预期目标,为VME 总线接口逻辑功能的设计与实现提供了一条途径。

本文创新点:VME 总线接口电路设计方法有多种,本文利用可编程逻辑器件,通过软 件手段实现VME 总线地址译码以及数据读写与中断控制逻辑,使总线接口电路得到了有效 的简化。

上一篇:基于IGBT的高可靠性驱动电路设计

下一篇:基于FPGA的可复用通信接口设计