- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于ISO7816-3标准的智能卡接口控制器的设计

引言

---智能卡(SmartCard)又称集成电路卡(Integrated Circuit Card,即IC卡),将微电子技术和计算机技术结合在一起,具有高的可靠性、安全性和灵活性,其广泛地应用于电信、金融、交通及公共事业等领域。智能卡接口控制器是连接智能卡和主控设备的桥梁,是智能卡处理设备中的最重要组成部分之一。面对庞大的市场需求,各大芯片厂商都推出了各自的智能卡接口控制器芯片,例如,Philips的8007、Linear的LTC1755/6等。本文也提出一种实用的智能卡接口控制器的设计方案。

控制器工作原理

● 控制器的结构

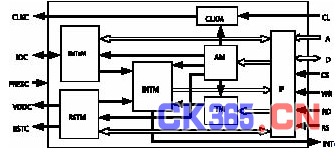

---本方案的设计过程遵循集成电路设计的一般流程,采用自上而下的模块化设计方法。该控制器由七个子模块组成:卡激活复位模块(RSTM)、串行数据收发模块(RxTxM)、状态中断管理模块(INTM)、定时模块(TM)、时钟管理模块(CLKM)、寄存器地址管理模块(AM)和主控制器接口(IF)。其结构如图1所示,CLKC、IOC、PRESC、VDDC和RSTC为控制器同智能卡的接口,分别为输出给智能卡的时钟、双向数据线、卡存在输入信号、卡电源控制信号和输出给卡的复位信号。本控制器同主控器(如CPU)的接口信号有:主时钟输入CLK、地址信号A、双向并行数据线D、片选输入信号CS、写控制信号WR、读控制信号RD、主复位信号RST和中断输出信号INT。

● 内部寄存器

---通常,用户程序要通过对卡接口控制器寄存器的读写操作,才能实现同IC卡的交易,因此,智能卡控制器内部寄存器设置的合理性直接影响到该设计方案的可行性和将来实际产品使用的便利性。不同的智能卡控制器的寄存器设置一般不尽相同。同其他的智能卡控制器相比较,本方案所设置的寄存器数目相对较多,功能更加全面。表1列出了本控制器的寄存器及其地址分配情况。

---卡控制器使能寄存器EN像个总开关,用来使能或关闭整个控制器。当用户系统暂时不需要用到卡控制器时,可以设置EN=0,便可关闭整个控制器内部的所有操作(包括内部分频器的动作),这样可以减少系统中不必要的功耗。时钟预分频参数寄存器PRSCL的设置可以在无需外加分频器的情况下,使控制器方便地应用到高时钟频率的目标系统中去。目前其他绝大多数的卡控制器中都没有设置功能与EN和PRSCL相同或者相似的寄存器。因此寄存器EN和PRSCL的设置是本方案的一大特点,若把此卡控制器作为一个IP用到SoC的设计中去,这一特点将显得尤为重要。

---工作等待时间整数值寄存器WWT只对T=0类卡有效,字符等待时间整数值寄存器CWT和块等待时间整数值寄存器BWT只对T=1类卡有效。本控制器同时设置了这三个寄存器,因此,其既可以和T=0类卡进行通信,又可以和T=1类卡进行通讯,这样弥补了目前大多数的卡接口控制器只能同某一类卡进行通信的弊端。

---如表1所示,本控制器还设置其他寄存器,比如ETU、TXDB、STMR等,这样做是为了更全面地满足ISO7816-3标准地要求,能够兼容各类型的IC卡,同时使得用户软件能够更方便地干预同IC卡的交易过程,提高了交易过程的可控性和使用的便利性。

● 卡控制器的工作过程

---主控制器(HOST)通过主控制器接口(IF)向卡控制器发送命令(即操作卡控制器的寄存器),卡控制器各个模块协同工作对此命令进行解析后,再通过IC卡接口对卡进行相应的操作,这样就完成主控制器对IC卡的一次操作。同样,从IC卡过来的命令或者状态通过卡控制器的处理后,再将相关信息报告给主控制器。卡控制器就是这样在IC卡和主控制器之间起着桥梁作用。下面将重点介绍串行数据收发模块(RxTxM)工作过程。

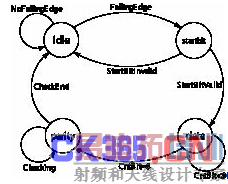

---本方案所设计的卡控制器的串行数据收发模块(RxTxM)负责接收IC卡发送过来的串行数据和将主控制器的命令以串行的方式发送给IC卡。其中串行数据接收器为一个状态机,其状态转换图如图2所示。状态机平时处于空闲状态(idle),若IOC端口上没有负跳变(NoFallingEdge),状态机便一直处于此状态。当检测到IOC上有负脉冲(FallingEdge)时,状态机便进入接收起始位状态(startbit),若起始位不合法(StartBitInvalid,例如宽度不够),状态机便返回idle状态,否则状态机进入到接收数据状态(data)。若还没有收满8位数据(CntBit<8),则继续接收,若已经收满了8位数据(CntBit=8),状态机便进入接收和校验奇偶的状态(parity)。若奇偶校验没有结束(Checking),则继续处理,否则状态机返回idle状态,至此控制器完成一次接收过程。

---若成功接收到1字节,便立即产生一个成功接收状态量rcv_ok,提交给状态中断管理模块(INTM);若接收的数据有错误,也会立即将接收错误的状态rcv_error,提交给INTM,并且在IOC数据线上产生一个1~2位数据宽度的负脉冲,以请求IC卡重发刚才的字节。按照ISO7816标准的规定,这种对同1字节的重发请求最多只发送3次。因此,若RxTxM在第三次重发请求之后仍然接收到错误的字节,RxTxM立即产生一个重收次数超限的状态RTO,报告给INTM。

---当主控器往本控制器的发数寄存器写入1字节数据时,本控制器便会以串行的方式发送给IC卡,若发送成功且没有检测到IC卡的重发请求,便立即产生一个发送成功的状态量tr_ok,报告给状态中断管理模块;若检测到IC卡的重发请求,便重发刚才的字节。同样如果在第三次重发后仍然收到IC卡的重发请求,则立即报告给INTM一个重收次数超限的状态。

设计的仿真及实现

● 控制器模型的时序仿真

---在Xilinx公司的ISE5集成开发环境下,用VHDL语言建立各个模块的RTL模型,并模仿实际情况,用VHDL编写了测试向量testbench,选用外部仿真软件Modelsim进行仿真。由于篇幅关系,这里仅列出控制器接收IC卡发送过来的串行数据时的仿真时序波形,如图3所示。

---由图3可以看出,IC卡发过来的串行数据为1001001010(低位在前),共10位,除去起始位0和校验位1,8位数据为00100101,与数据接收寄存器rxbuffer所接收到的内容相同,且校验结果为0,满足ISO 7816

● 设计的FPGA实现

---根据综合结果,目标器件选用Xilinx公司的Spartan2系列的xc2s30tq144-6,其内部资源概况在表2中列出。

---为了进一步验证本设计的正确性,将本控制器模型的接口改成AMBA总线的APB接口,把它作为一个外围IP,连接到以AMBA总线作为内部总线的SoC的APB总线上,然后将此SoC系统编译并下载到FPGA中,再嵌入实际的应用系统中,经验证可以同IC卡进行交易。

结论

---本方案所设计的IC卡控制器可行性已经在实际应用中得到了验证,应用软件通过对控制器内部的寄存器的操作,可以方便地与智能卡进行通信交易。本IC卡控制器不仅可以单独下载到FPGA或CPLD器件中,应用到目标系统中去,也可以在对其外部接口稍做修改后,将其当作一个IP模块,方便地应用到SoC系统的设计中去。由于没有为其设计内嵌的给IC卡供电的电源模块,所以在实际应用中,需要同外扩的电源模块搭配起来使用,这点有待进一步改进和完善。

上一篇:基于Atmega8的数字功放设计

下一篇:基于FPGA的智能超声波功率源原理与设计