- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

语音合成芯片的ASIC设计

引言

近年来语音集成电路获得了迅速的发展,其应用范围越来越广,在自动售货机、ATM柜员机,内部直通电话机以及玩具等方面应用了大量的语音合成芯片。该芯片内部采用脉宽调制,将数字信号正确的还原成模拟信号,从而使得电路的输出端不需要外接D/A转换;同时使芯片能够以纯数字电路的形式实现,因此可以很方便地把语音合成电路做成专用集成电路(ASIC),这样可以提高电路的抗干扰能力,增加该系统工作的稳定性,同时也降低了生产的成本和简化了板级电路的复杂度。

1、语音合成芯片的结构

该语音合成芯片首先是将语音资料以LOGPCM编码的方式存入ROM中,语音总长为35秒,将其分割成4个语音段,2个触发键,可以根据不同的需求来确定该芯片的触发方式,每一个语音段可指定不同的播放速度,也可设定“语音组跳跃功能”将现在的语音段(S1)播放完后,接着播放指定的语音段,并可以进一步设定这个指定的语音组是否需要无限的循环播放。同样两个触发键可选择为输入或者输出端,音频输出为PWM1和PWM2 两个输出端,可直接驱动喇叭;频率振荡器有两种选择:外部可调电阻式频率振荡器和内部频率振荡器。该芯片的总体设计框图如图1所示。

图1语音合成芯片总体设计框图

2、语音合成芯片工作原理

本语音合成芯片有两个控制信号端:IO1和IO2,共有四段语音内容,根据设计的要求IO2的优先级别高于IO1,通过不同的输入来播放不同语音段的语音信号,而且两个控制信号IO1和IO2的触发方式都采用边缘触发,语音无重触发(后段盖前段)之功能,而且每触发一次输出一段语音内容,循环有序输出各段语音。芯片工作后,IO2开始触发则播放第一段语音(S1),如果IO2为高电平时,此时的IO1触发无效;当IO2为低电平时,IO1触发则播放最后一段语音(S4),假如IO2继续触发,将依次循环输出各段语音。

3.语音合成芯片设计

3.1 时序产生电路

这部分电路是给整个语音合成芯片提供时钟信号,该语音合成芯片只包括一个时钟,就是播放的速度。在芯片中的以LOGPCM编码方式所存储的语音信息是8位,采用PWM的方法进行调制,就需要至少28倍PWM数据读取频率来进行调制,使得PWM信号输出的占空比能实现256级的变化。语音信号是以8KHz为采样频率,因此要以8K×256=2M的时钟频率来进行调制,从而实现芯片的正常播放。在ASIC设计中,为了达到2MHz的时钟频率,采用环行振荡器,该电路3个CMOS反向器,1个电容和一个片外电阻,调节片外的电阻可以产生不同频率的振荡信号,因此可以通过改变外部的电阻值来实现不同的播放速度。同时在芯片的内部可用二分频电路串联来实现28分频。

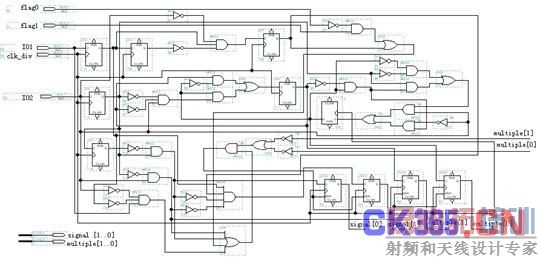

3.2 输入信号控制模块电路

输入信号控制模块中的输入信号IO1和IO2对ROM地址进行前端控制,用来确定播放的语音段,该芯片设计的ROM有16根地址,8根数据线,将语音分割成四段,每段语音可占据4000H个地址单元,第一段语音存储的地址范围从0~3FFFH,第二段语音存储的地址范围从4000H~7FFFH,第三段语音存储的地址范围从8000H~BFFFH,第四段语音存储的地址范围从C000H~FFFFH。在该电路设计中,为了避免一些状态的误动作,故将输入信号IO2、IO1进行两级寄存,首先检测IO2的上升沿,当IO2的上升沿来了后,将signal输出端口先输出“00”信号(signal输出端就是下级模块:地址输出模块的信号控制输入端);为了使得每检测到一次IO2的上升沿,就让一个2位计数器加1,IO2经过寄存器后,再一次检测上升沿,将signal输出“01”信号。然后启动地址输出模块,当IO1上升沿来后,首先是判断IO2是否是低电平,只有IO2在低电平的状态,IO1才能动作,工作方式和IO2一样;否则IO1无效。电路原理图如图2所示。

图2输入信号控制模块电路

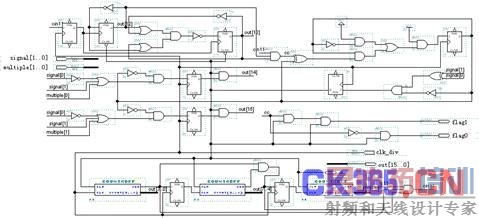

3.3 ROM地址输出模块

ROM地址输出模块是用来接收上级输入信号控制模块的控制信号,根据不同的控制信号,输出不同的地址信号来读取ROM中的数据,ROM有16根地址线,因此在ROM地址输出模块中设计了16位的加法计数器,首先设计一个2位的加法计数器,再由两个2位的加法计数器构成一个四位的加法计数器,然后由3个四位的加法计数器构成一个12位的加法计数器,最后由12位的加法计数器和一个2位的加法计数器构成14位的加法计数器,14位加法计数器刚好能从0计数到3FFFH,也就是第一段语音存储的地址范围,其他各段的语音存储的开始地址相当于3FFFH的相应倍数加1,因此采用倍乘方法,其计算方法是:DOUT=C+MUL×(D+1),其中DOUT表示输出的ROM地址;C表示14位的加法计数器;MUL表示要播放的该语音段号减1;D是常数3FFFH。电路原理图如图3所示。

图3 ROM地址输出模块电路及仿真波形

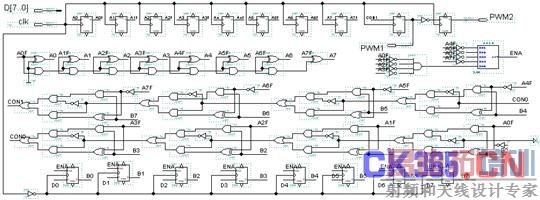

3.4 脉冲宽度调制(PWM)模块

该模块是将存储在ROM中的数据进行解码,将解码的音频信号直接由喇叭进行输出,其方法就是:用连续变化的调制信号各瞬时值对脉冲载波的持续时间进行调制。实际上就是把数字信号转化成模拟信号,从而使声音还原[2]。已调脉冲信号的宽度随调制信号的瞬时值大小而变化,当脉冲幅度不变时,调制的信号变化完全由脉冲的宽度来表示,在信号的传输中,要使信号的幅度失真干扰得到解决,可以用限幅的方法加以消除。由于语音信号的采样频率是8KHz,为了使得输出信号的占空比为256级的变化,则用8位的计数器来实现0到256的计数,让输出信号为“1”的时间维持相应数据大小的长度。而数据的读入是在系统调制时钟(2MHz)的下降沿来临时开始动作,且当8位计数器为“0”时开始读入数据。因为此时正是前一个PWM调制完成,而下一个调制周期还没开始的时隙,只有在这个时隙开始读入数据才能不影响PWM调制[3]。最后是将读入的数据和当前8位计数器的计数值进行比较,假如计数值小于当前读入的数据值,则端口1(PWM1)输出高电平“1”,否则输出低电平“0”,这样让输出信号的占空比根据输入LOGPCM数据的大小而发生变化,从而实现语音输出功能。电路原理图如图4所示。

图4 脉冲宽度调制(PWM)模块电路

3.5 存储语音的ROM

ROM(只读存储器)由地址译码器、存储矩阵和输出缓冲3部分组成;地址译码器将ROM输入的16位地址码A0、A1……A15译码后输出个输出信号W0、W1……W65535,称为字线。每一条字线输出分别对应一个存储单元的地址,如W0对应0单元地址,W1对应1单元地址。利用此地址从存储矩阵中选出指定的单元,并将其中的数据送至输出端。存储矩阵由许多基本存储单元排列而成,包含大量存储单元,存储单元在ASIC设计中由MOS管构成,它是作为输入的条字线和作为输出的8条位线(D0~D7)组成的阵列。每条字线和位线的交叉点都是一个存储单元,存放一位二进制值0或1。每一个或一组存储单元对应一个地址[4]。

4 功能仿真及分析

从实际应用和成本的角度来考虑,拟订0.5um的硅栅工艺进行流片,按照nMOS管宽长比为14:1,pMOS管宽长比也是14:1的比例设置(有些地方需要作适当的调整),将以上的各个模块进行连接,在QuartusII中进行功能仿真,仿真出来的波形如图5所示:其中clk_div是256分频电路的输出信号,最终的输出结果是2路音频信号PWM1、PWM2,flag0是语音播放完后的标志信号,flag1是当有语音信号播放时为高电平,播放中断将送出“0”信号,D[7..0]则是ROM中所存的语音资料, IO1为“1”时则立即播放最后一段语音信号,当IO2为“1”时,则依次播放第一至第三段语音;sig[1..0]是语音段,为“1”时则说明正在播放第一至第三段中的某一段,当为“2”时,则是播放最后一段语音,为了实现IO2是依次播放第一至第三段语音,采用倍乘的方法,当有第一次IO2为“1”时,倍乘mul[1..0]输出“0”,以此类推,当有第四次IO2为“1”时,mul[1..0]将重新清零。

图5 功能仿真波形图

5 结束语

本文作者创新点: 在本文中所研究的语音合成芯片利用了多种优化方式,将设计的语音合成芯片内部电路更加简化,而且性能更加稳定。同时用脉冲宽度调制(PWM)方法对语音信号的调制与解调的可行性进行论证,并且用FPGA硬件验证的方式来证明利用PWM技术实现全数字的语音合成输出是可行的,从而使该语音合成芯片以全数字的形式来实现。

上一篇:TMS320C61416

EMIF下双FPGA加载设计

下一篇:基于ATmega8的新型电动自行车调速控制系统设计