- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于FPGA的可键盘控制计数电路的设计与实现

摘要:介绍一种基于FPGA(Field Programmable Gate Array)现场可编程门阵列的可键盘控制的计数,显示电路的实现方法。应用VHDL语言(高速集成电路硬件描述语言)完成了3x4矩阵开关的扫描电路,可预置数的BCD码计数电路及4位数码管动态扫描电路的描述。通过原理图输入方式完成了系统功能的设计。电路结构简单,便于扩展,可靠性高,且可移植性强,容易实现。该电路已成功应用于测试某脉冲电容质量试验的控制电路中。

关键词:FPGA;键盘扫描;计数;动态显示

FPGA做为现代电子设计技术的核心器件,成为目前硬件设计研究的重点。在工业控制中,计数显示基本电路在仪器仪表中得到了广泛应用,而如何根据需要灵活的设置计数范围,是一个较为复杂的问题。本文应用EDA技术通过对键盘的控制,实现了从0~9999范围内预置数可变的计数显示电路设计。与传统的应用单片机控制键盘扫描的设计方法相比,具有集成度高,稳定度高,抗噪声能力强,容错率低等优点。

1 系统设计原理及电路图

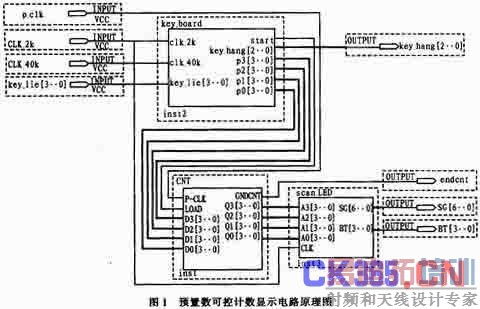

图1为基于FPGA的预置数可控计数显示顶层设计电路原理图,共由3部分组成:键盘扫描控制电路key_board;BCD码计数电路CNT;4位数码管动态扫描显示电路scan_LED。首先,由键盘扫描电路完成对键盘的扫描和键值的译码,当计数电路置数端LOAD为上升沿时,将键盘扫描电路读取的数据经P3-P0并行置入到计数器中做为其计数范围,计数器的输出通过动态扫描译码模块驱动4位数码管显示。

2 VHDL语言的实现

该设计采用层次化设计方法,首先采用VHDL语言完成了对各子模块电路的描述,然后分别将其生成符号元件,通过原理图编辑完成了系统的设计。

2.1 键盘扫描电路

2.1.1 行列式键盘工作原理

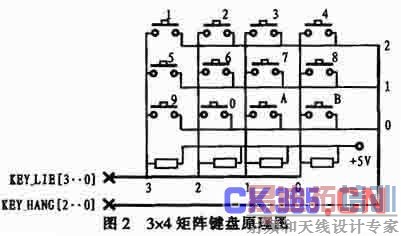

图2为3x4行列式键盘原理图,行线是KEY_HANG[2..0],列线是KEY_LIE[3..0],形成12个交叉点,每个交叉点连接一个按键。12个按键分别对应数字0~9和清零键A,确定键B。当没有按键按下时,所有交叉点断开,由于列线的上拉电阻作用,使其保持高电平。如果行线KEY_HANG[2..0]被设置为低电平,当有按键按下时,该键所在的行线和列线被按键短路,那么相应得列线就变为低电平。

2.1.2 键盘扫描电路工作原理

图3为键盘扫描原理图。CLK_40K为键盘扫描工作时钟,连续读取数据输入端KEY_LIE[3..0]的信息;CLK_2K为键值控制工作时钟信号,无键按下时控制电路循环扫描输出;P3,P2,P1,P0为键盘译码输出BCD码形式;START端为数据输出标志信号,当P3-P0输出时,START端输出一个脉冲。工作时,由行信号输出端KEY_HANG[2..0]循环输出“110”,“101”,“011”。当没有按键按下时,扫描电路列信号输入端检测到“1111”。当有按键按下时,例如按下1键,此时行信号KEY_HANG[2..0]输出“011”,由图2可知。列信号输入端将检测到“0111”,在扫描译码时,可根据行信号输出和列信号输入数据同时判断“0110111”对应数据为1。

2.1.3 键盘扫描电路VEIDL实现

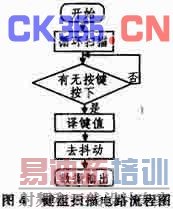

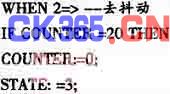

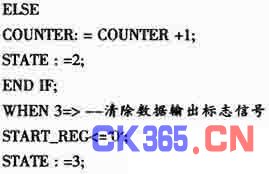

键盘扫描电路主要有判断按键有无按下,键值识别和去抖动处理等功能。其中去抖处理主要为了避免外界振动引起按键误动,以及保证按键每稳定闭合一次,系统仅对其响应一次。采用不同的键盘其机械抖动时间各异,本文设置去抖时间为20 ms。图4为键盘扫描电路VHDL描述流程图。以下是去抖动程序关键代码:

2.2 可预置数BCD码计数电路

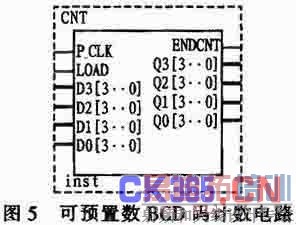

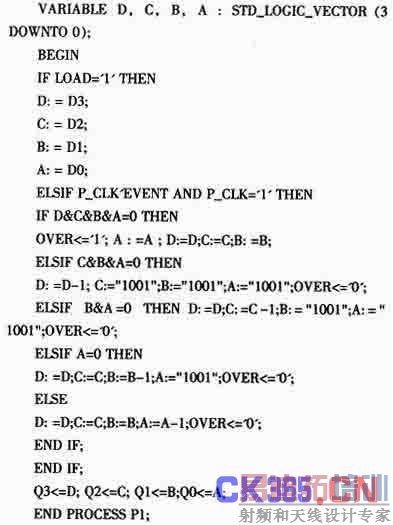

图5为可预置数BCD码计数电路。置数端LOAD为高电平时,将通过键盘设置的数并行置入到D3~D0。然后对输入的脉冲直接进行BCD码减法计数,由Q3~Q0输出。计数结束,ENDCNT端输出一个脉冲。

部分源程序如下所示:

2.3 4位数码管动态扫描显示电路

段式LED显示器的控制方式分为静态显示控制和动态显示控制两种。本电路设计采用动态扫描方式,具有占用资源少,电路结构简单等优点。电路如图6所示。外接4位共阴数码管,其中每个数码管的7段a、b、c、d、e、f、g都分别连在一起,4位数码管分别由BT[3..0] 4位选通信号来选择。被选通的数码管显示数据,其余关闭,与此同时,在段信号输入端口加上希望在该对应数码管显示的数据。随着选通信号的循环扫描,段码的分别输出,利用数码管的余晖效应,即可显示4位数据。

3 仿真结果

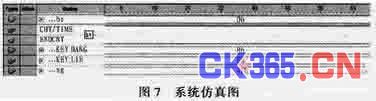

将设计好的电路经过编译、引脚配置、下载到FPGA芯片EP1C12Q240。采用QUATUSⅡ6.0软件自带的嵌入式逻辑分析仪对目标芯片内部信号各节点进行观察分析,如图7所示。实验中已将预置数1234置入计数器中,通过图7可以看到此时位选信号选通第2位数码管,显示数据3。

4 结束语

完成了基于FPGA,应用VHDL文本输入和原理图混合输入法,实现预置数灵活设置的计数显示电路。该电路设计解决了可预置数计数器从外部设备置数难的问题,以及在电路内部直接实现BCD码计数,方便,可靠,电路简单,尤其该系统在较恶劣环境情况下依然可以稳定工作。