- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

TMS320C54xDSP的视频 像采集接口设计与实现

视频图像采集的方法一般可以分为:自动图像采集和基于处理的图像采集。前者采用专用图像采集芯片,自动完成图像的采集、帧存储器地址生成以及图像数据的刷新;除了要对采集模式进行设定外,主处理器不参与采集过程。后者采用通用视频A/D转换器实现图像的采集,不能完成图像的自动采集,整个采集过程在CPU的控制下完成,由CPU启动A/D转换,将数据存入帧存储器。其特点是数据采集占用CPU的时间,对处理器的速度要求高,但电路简单、成本低、易于实现,能够满足某些图像采集系统的需要。下面以TI公司的TMS320VC5402(以下简称C5402)DSP为例,介绍基于数据信号处理器(DSP)的视频图像采集电路和采集方法。

C5402是TI公司C54x系列定点DSP芯片中的新产品它集中了此系列早期产品的优点,并提供了许多新的功能,开发和使用更加方便。C5402具有灵活的指令系统和操作性能,它可选择助记符指令或算术指令作为编程指令,同时支持汇编语言和C语言的单独或混合编程。C5402采用改进的Harvanl处理结构,指令流水线操作。计算和处理速度很高,系统单指令周期可达到10ns。在片内提供16k的RAM用作程序和数据存储,其最大可扩展寻址空间为1M字节。C5402提供的McBSP串口和DAM数据传送方式极大地方便它在通信领域的应用和开发。C5402由于其高性能价格而成为当前语言和静态图象处理和主流产品。

1 电路原理

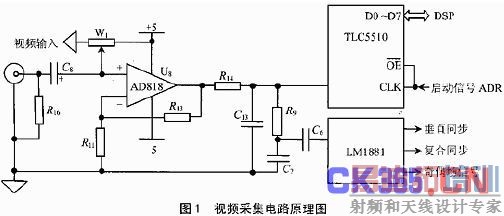

采集电路如图1所示,由视频缓冲器、视频A/D转换器和视频同步分离电路等组成。

1.1 视频缓冲器

来自摄像机的标准黑白全电视信号的幅度峰-峰值为1V,要送往A/D转换器和行、场同步分离电路,而A/D转换器的满量程为2V,因此,视频缓冲器要对全电视信号进行阻抗匹配和电压放大,并能对全电视信号进行黑电平调整。图1中,U8构成视频缓冲器,增益为+2;调整电阻W1可以调整输出信号的直流电平;R16是输入匹配电阻,阻值大小由信号源决定,本电路中为75Ω。

1.2 A/D转换器

TLC5510是美国TI公司生产的新型模数转换器件(ADC),它是一种采用CMOS工艺制造的8位高阻抗并行A/D芯片,能提供的最小采样率为20MSPS。由于TLC5510采用了半闪速结构及CMOS工艺,因而大大减少了器件中比较器的数量,而且在高速转换的同时能够保持较低的功耗。在推荐工作条件下,TLC5510的功耗仅为130mW。由于TLC5510不仅具有高速的A/D转换功能,而且还带有内部采样保持电路,从而大大简化了外围电路的设计;同时,由于其内部带有了标准分压电阻,因而可以从+5V的电源获得2V满刻度的基准电压。TLC5510可应用于数字TV、医学图像、视频会议、高速数据转换以及QAM解调器等方面。

TLC5510的参考电压可由其内部的3个电阻R1、Rref、R2设定,如图2所示。按图2连接,将参考低电压设定为0.6V,参考高电压设定为2.6V,电阻Rref上的2V压降即为满足程电压。当输入电压为0.6V时,A/D转换的输出数据为0;当输出电压为2.6V时,A/D转换的输出数据为255。

TLC5510有1个转换时钟输入端(CLK)和1个片选端(OE)。CLK的下降沿启动A/D转换,1次A/D转换需要2.5个CLK周期,即第1个CLK的下降沿启动A/D转换后,要等第3个CLK的上升沿出现时,第1个A/D转换数据才会准备好。当片选信号(OE)为低电平时,A/D转换数据输出到外部数据总线上,供DSP读取。

1.3 采集电路的DSP的连接

采集电路与C5402的连接如图3所示。其中,U19是16位宽度的高速总线收发器,并具有电平转换的功能,将5V的奇偶场信号、复位同步信号和A/D转换器输出的数字信号转换为C5402能接受的3.3V信号。

仔细分析了TLC5510的工作原理和C5402的读/写时序后,没有将TLC5510作为C5402的扩展I/O口,而是将TLC5510作C5402的一个扩展的外部存储单元。用该单元的读选通信号(ADR)与TLC5510的CLK和OE相连(如图3所示),这样C5402读TLC5510时,1条读数指令完成2个操作:启动A/D转换并读取A/D转换数据。不过当前的A/D转换结果要等到第4次读该端口时才能得到,A/D转换的时序如图4所示。

1.4 同步分离电路

同步分离电路采用LM1881。该器件能接收PAL制、NTSC制和SECAM制的全电视信号,输出复合同步信号、垂直同步信号、奇偶场信号和色同步旗形脉冲信号。C5402根据奇、偶场信号找到一场图像的开始,做好采集图像数据的准备。当复合同步信号到来时,C5402响应行中断(INT0),连续采集一行图像数据。

2 图像采集

压缩卡的图像采集是由C5402直接完成的。初始化结束后,C5402按缺省模式或主机命令的求确定图像的大小和采集速率等参数,然后根据奇、偶场信号和复合同步脉冲信号来采集图像数据。

2.1 采集流程

采集流程可分为以下几个步骤:

①等待场开始。

②当场开始信号到来时,C5402进入场处理子程序,开放行中断做好采集一场数据的准备。根据奇、偶场信号可以决定是采集奇场图像还是采集偶场图像。

③当复俣同步信号到来时,C5402进入中断服务子程序,并将图像数据存入扩展的数据存储器中。当一场或一帧图像各行数据都采集完毕后,关闭中断。

2.2 行、场处理

DSP接收到场开始信号后进入场处理子程序中。在场处理子程序中,先确定将要采集的图像的大小并设置采集、编码及发送过程中要使用的参数,然后打开行采集中断INT0,延时一定数目的行周期后退出场处理子程序,进入图像采集阶段。

行采集中断要完成图像采集和其它一些任务。在每行图像采集之间应根据图像大小延时一段时间,以保证采集到的图像位于画面的中心。采集图像时,每隔140ns读取一个A/D转换数据,存入帧缓冲器。由于读取A/D转换结果与写帧缓冲器只用了80ns,因此可以先将图像数据减去128,再存入帧存储器,这样就进行了JPEG编码时就不要执行减128操作了,节约了时间。

结语

本电路成本低、容易实现、占用DSP时间少、能满足黑白电视信号的采集,在合肥工业大学DSP联合实验室研制的便携式准动视频图像压缩系统[2]中得到应用,效果良好。以本电路为基础,使用TI公司的其它高速视频A/D转换器,例如TLC5540或TLC5580,便可构成更高分辨率的视频图像采集系统。