- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

浅谈使用可定制微控制器高效开发系统级芯片

为了应对成本、尺寸、功耗和开发时间的压力,许多电子产品都建构于系统级芯片 (SoC" title="SoC">SoC )之上。这个单片集成电路集成了大多数的系统功能。然而,随着这些器件越来越复杂,要在有限的时间里经济地进行产品开发以满足产品上市时间的压力已变得越来越困难。SoC集成了一些可编程部件 (特别是微控制器" title="微控制器">微控制器 ),使得其软件开发与硬件开发同样的昂贵和耗时。

使用基于业界标准、带有片上存储器和各种标准接口的ARM" title="ARM">ARM ò处理器,再加上面向特定应用逻辑和非标接口的金属可编程模块 (MP模块),构成的可定制微控制器是切实可行的SoC开发方法,能够解决上述问题:

采用预先已经准备好的基础晶圆,仅针对定制部分添加金属层,可以缩短器件生产制造的时间。

最大限度地减少集成特定应用逻辑方面的设计耗费,并减少制备工艺中所需的光罩数,可以降低开发成本。

仿真板包括了处理器、内存、外设和标准接口,并用FPGA" title="FPGA">FPGA 来代替MP模块,实现了软/硬件全速并行测试,提高了器件生产制造和软件开发的首次成功率。

可定制微控制器架构

新一代的ARM9处理器,通过全新的设计,采用了更多的晶体管,能够达到两倍以上于ARM7处理器的处理能力。这种处理能力的提高是通过增加时钟频率和减少指令执行周期实现的。

(一) 时钟频率的提高:ARM7处理器采用3级流水线,而ARM9采用5级流水线。增加的流水线设计提高了时钟频率和并行处理能力。5级流水线能够将每一个指令处理分配到5个时钟周期内,在每一个时钟周期内同时有5个指令在执行。在同样的加工工艺下,ARM9TDMI处理器的时钟频率是ARM7TDMI的1.8~2.2倍。

(二) 指令周期的改进:指令周期的改进对于处理器性能的提高有很大的帮助。性能提高的幅度依赖于代码执行时指令的重叠,这实际上是程序本身的问题。

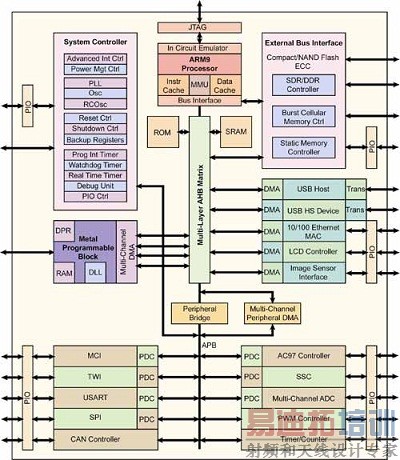

如图1所示,可定制微控制器的基础为业界标准的ARM7或ARM9处理器内核,以及连接片上SRAM和ROM、外部总线接口和系统外设的多层AHB总线矩阵,并可桥接面向系统控制器和低速外设的高能效APB。该架构的一个主要特点是分布式DMA,这种DMA加上由AHB总线矩阵提供的并行数据通道,能为器件提供极高的内部数据带宽。器件中的MP模块具有多个DMA端口,因此由其实现的专用IP也能受益于这种高速内部带宽。

图1:基于ARM9的可定制微控制器架构

基于CISC架构的微控制器除了80C51外,还包括Motorola提供的68HC系列微控制器,这也是大量应用的微控制器系列。

基于RISC架构的微控制器则包括Microchip的PIC系列8位微控制器等。在16位RISC架构的微控制器中,Maxim公司推出的MAXQ系列微控制器以其高性能、低功耗和卓越的代码执行效率,成为许多需要高精度混合信号处理以及便携式系统和电池供电系统的理想选择

该架构具有齐备的标准外设和接口,能满足大多数应用对用户接口、联网/连接和存储的要求。此外,在MP模块中还可以实现各种外设实例或其它外设/接口。

该架构实现了复杂的系统控制器,集成了所有的系统和功率管理功能,可以控制系统的启动和关闭。该控制器具有多个时钟源和外设开关控制线,使每个功能构件都能以支持应用的最小时钟频率运行,也可在不需要时进入闲置模式。因此能最大限度地降低器件的功耗。

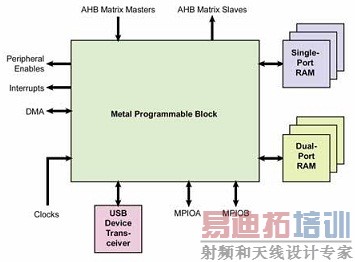

金属可编程模块

如图2所示,金属可编程模块 (MP模块) 的门密度与实现器件固定功能部分的标准单元密度接近。MP模块需要足够的容量来实现第二个ARM处理器核、一个数字信号处理器 (DSP)、额外的接口以及复杂逻辑模块,如GPS相关器。它还需要一些内部功能和专门的外部连接,以提高其实现特定应用逻辑的效率。MP模块还需要多个分布式单端口及双端口RAM,并与需要他们的逻辑单元紧密耦合。

图2:金属可编程模块

数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。数字信号处理是一种通过使用数学技巧执行转换或提取信息,来处理现实信号的方法,这些信号由数字序列表示。在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。德州仪器、Freescale等半导体厂商在这一领域拥有很强的实力。

可定制微控制器设计/制备流程

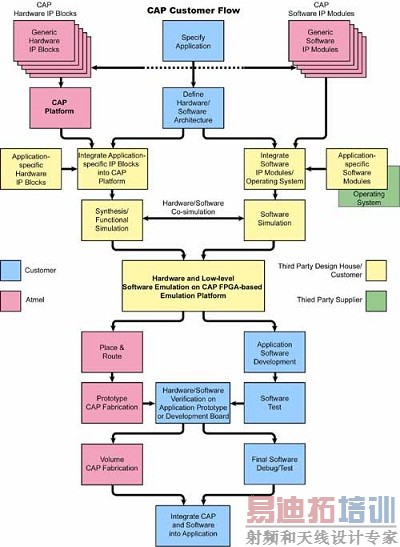

如图3所示,可定制微控制器设计流程的目标是要在最短时间内,以合理的成本和极高的首次硅和软件成功率,开发面向特定应用的系统级芯片 (SoC),并包含软件和硬件。

图3:可定制微控制器设计流程

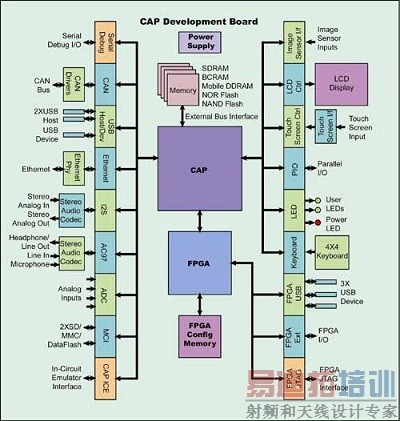

设计流程的一个关键步骤是在仿真板 (见图4) 对硬件以及至少底层软件进行仿真。该仿真板包括完整的内存、标准接口和网络连接,以及可按应用要求配置的其它附加连接。具体包括:

图4:可定制微控制器的仿真板架构

这种MCU/FPGA组合可以接近最终器件的工作频率运行。这样就能完成器件的即时性测试,包括平台中的MCU和各种标准接口、MP模块中实现的各种功能,以及到目前为止已开发的所有软件。这种测试至少涵盖了如下测试对象:设备驱动程序、操作系统端口,以及用于控制MP模块各种功能的应用代码模块。而更改器件的软/硬件单元无需任何额外成本。

结论

可定制微控制器是特定应用系统级芯片的高效开发平台。其设计流程能够解决系统级芯片设计的大多数问题,而且开发成本较低、风险较小,并能提高硬件制备和软件开发的首次成功率。而本文所描述的架构和设计流程由爱特梅尔的CAP 可定制微控制器系列所实现。

- 软/硬件并行开发。设计流程调整为适合软/硬件并行开发,克服了系统级芯片开发的主要障碍之一。

- 面向特定应用的软件/操作系统与接口/外设驱动程序的快速集成。平台上所有接口/外设均有驱动程序。已经有很多业界领先的操作系统被移植到微控制器架构上。将这些软件模块与应用代码模块和用户接口集成起来的工作可与硬件开发一同进行。

- 快速完成布线布局,只需针对金属层。采用成熟的布局方案快速完成MP模块的金属层布线布局。

- 高效、低成本的掩模光刻。只需要对器件金属层进行掩模。

- 快速的生产制造过程,只需针对金属层。各特定应用器件的光刻制备以预制的微控制器平台为起点,只需添加金属层。

- 以FPGA为基础的仿真板

-

- 器件固定功能部分用带外接FPGA接口的单芯片来实现。

- 使用高密度的FPGA仿真MP模块,包括内嵌存储器和外部I/O。

- 采用FPGA配置存储器为MP模块保存编译好的HDL代码。

- 外部总线接口 (EBI) 和FPGA的外接I/O连接到扩展板上不同类型的内存,如SDRAM、移动DDRAM、猝发Cellular RAM、NOR闪存、NAND闪存等。这些存储器将加载应用软件和应用数据集。

- 所有标准接口 (CAN、USB、Ethernet、I2S、AC97、ADC、MCI等) 都通过收发器/物理层/编解码协议层与外部连接,因此可以对器件的外部接口和联网/通信链路进行全方位的测试和调试。

- 图形用户界面 (GUI) 的所有部件都连接到相应的板上器件或接口,比如LCD、键盘、触摸屏接口等。这样就可在板上完成GUI基本接口的测试。

- 仿真板提供外部并行I/O (PIO) 和FPGA I/O,用于连接特定应用的外接器件,以及实现非标接口。剩余的FPGA I/O也可用于验证。

- 仿真板配有JTAG仿真器 (ICE) 端口;通过该端口可用带有JTAG-to-USB的接口和标准开发工具对ARM核及其外设进行验证。

- 仿真板还配有FPGA JTAG端口;通过该端口可用FPGA厂家提供的工具对FPGA的内部信号进行跟踪和分析。

上一篇:PXI平台在电子制造业的应用方案

下一篇:半导体式光纤温度传感器的建模、仿真与实验