- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于AD7266的多路同步采样AD模块的设计

摘要:AD公司的AD7266提供了先进的功能和特性。AD7266是一款差分/单端输入、双核2 MSPS、12位、3通道SAR A/D转换器,为业界遥遥领先的同步采样ADC。AD7266共有6个模拟输入通道,能够直接与光电编码器连接,无需外部元器件,减化了设计并且降低了成本。这里主要对AD7266和基于AD7266的模块设计进行介绍。

关键词:AD7266;12bib 2Msps;模数转换

0 引言

数据采集系统广泛应用于雷达、通讯、图像、军工以及医疗、化工等领域,具有重要的应用价值。近年来,高速数据采集芯片(ADC)的快速发展,为用户设计带来了方便。选用AD公司的数据采集芯片AD7266,设计出一个具有四路一组的高速同步采样及多组2Msps的采样率的数据采集系统。

1 AD7266芯片介绍

1.1 AD7266概述

AD7266芯片集成有两个独立的高速12位连续逼近A/D转换单元、吞吐量为2Msps、低功耗,单电源工作2.7~5.25V。在每个D/A前有三复用开关可组成三路差分或六路单端信号输入;采样保持放大器为带宽10MHz的低噪声电路。

应用先进技术设计的AD7266在吞吐量时功耗非常低,电源5V吞吐量2MSPS时最大电流4mA。当工作在休眠模式下芯片提供有电源/吞吐量节能管理功能,为电池供电提供了节能方案。模拟信号输入范围可选择0~Vref或2Vref,输出码为二进制原码或补码。芯片内有2.5V参考源亦可外接100mV~2.5V的参考信号。AD7266的封装有LFCSP和TQFP两种。

1.2 AD7266的技术特性

AD7266为双12位3通道ADC芯片;其最高吞吐量为2Msps;供电电源为2.7~5.25V;低功耗:在1.5Msps吞吐量电源3v时最大12mW;在2Msps吞吐量电源5V时最大30mW:宽输入带宽10MHz;100kHz输入信号时70dB的SNR;片内参考2.5V;工作温度-40~+125℃;灵活的电源/吞吐量管理;同步转换/读;无管道延时;高速串行接口兼容SPI/QSPI/MICROWIRE/DSP;关闭模式最大电流1 μA。其芯片内部组成见图1。

1.3 AD7266引脚说明

AD7266芯片的引脚说明

2 设计原理

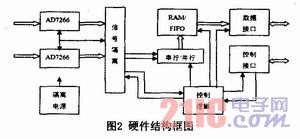

模块主要实现多路数据采样功能,主要用两片AD7266构成24路单端或12路差分输入,其中有四路可同时采样。外围逻辑及接口控制由CPLD、DSP或单片机构成,A/D输出的串行数据变为并行后送入RAM或FIFO缓存。硬件结构框图如图2所示。

3 实现方法

3.1 输入模拟信号预处理

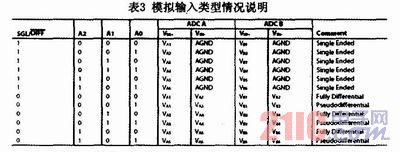

输入模拟信号主要有以下几种:0~5V、0~10V、0~±5V、0~±10V、0~20mA、4~20mA等。AD7266的最大输入电压范围为0~2×VREF即0~5V,电压信号0~5V可用,其它信号需调理变换为0~5V。电流信号用250 Ω电阻取样变为电压信号后供AD7266转换用。电路中两片AD72 66可根据输入信号是单端或差分分别进行设置,设置过程见图3。

图3中通过单端/差分控制信号SGL/DIFF*来实现对单端或差分输入方式的控制,其中SGL/DIFF*高电平为单端输入,SGIdDIFF*低电平为差分输入;CS*下降沿有效。设计中通过控制单端/差分控制信号SGL/DIFF*实现不同输入方式与不同输入范围,具体实现输出二进制码情

况见表2所示。

设计中通过单端/差分控制信号(SGL/DIFF*)与通道选择控制信号(A0~A2)实现模拟输入类型的不同,具体模拟输入类型与通道选择情况见表3所示。

3.2 数据采集、传送及缓存

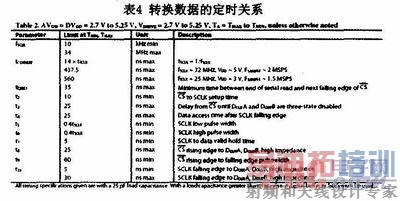

设计中转换数据的定时关系如表4所示。

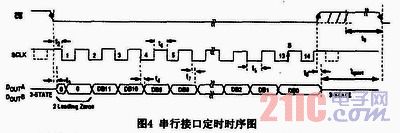

最大转换时间TCONVERT为14×TSCLK,在电源5V、时钟32MHz条件下转换时间为437.5ns。精确控制CS*与SCLK的时序,从串行数字接口获得转换后的数据,时序见图4。

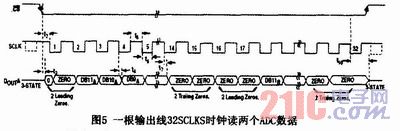

设计中用一根输出线读取两个ADC数据。共需32个时钟脉冲:其中A通道2个零标记头、12位数据、2个零尾标记(计16位);B通道2个零标记头、数据12位、2个零尾标记(计16位)。一根输出线读取两个ADC数据时序的见图5。

3.3 数据接口设计

串行数据在时序控制下输出转换为并行数据送存储器缓存,数据接口为兼容的高速串行接口SPI/QSPI/MICROWIRE/DSP或由CPLD构成的接口。如图2所示,本设计中采用CPLD实现接口的设计。串行数据经串行/并行转换后输出到FIFO进行缓存。

模块的接口为PCI总线,由接口桥电路PCI9052实现。数据可用中断或查询方式进行单组或批传送。PCI9052采用非复用、单周期读/写模式。

3.4 抗干扰设计

为减少高频干扰,在制作电路板时应尽量采用多层板,在中间加上地线层和电源层。另外,由于采样时钟的相位抖动会对AD产生相当于模拟输入正弦波所产生的影响,而时钟输入对AD7266来说相当于一个模拟输入,因此应当尽量选择低抖动晶体振荡器。采用高频时钟经分频后获得需要的时钟信号效果较好,并将时钟电路与系统模拟电路、数字电路相隔离,以防止其产生噪声。数字端电源、模拟端电源、数字端电源地和模拟端电源地增加电容网络,该电容网的作用有三个:其一是与内部参考放大器一起在大频率范围下提供一个低阻抗源以驱动A/D内部电路;其二是提供运放动态需要的补偿;其三是限制由参考电源产生的噪声干扰。

采用直流耦合差分输入的电路。在这种模式下,直流输入将上升到相对参考电压对称摆动的点上。电路把两个放大器配置为一个对称单元以形成差分放大器。放大器的差分驱动电路可以把一个以地为参考电压的单端信号转换为一个以AD的VREF管脚电压为中心的二倍的差分信号。单端输入信号接到不同放大器的两个相反的输入端上可以驱动差分放大器,放大器可选用双通道放大器AD8056。通常为保护AD7266不受过电压的影响,应当在放大器的输出端和AD的输入之间加一个接地二极管。如果放大器和AD7266用同样的正电源,AD就不会受到过电压的影响。这种电路应当是最佳选择,为信号稳定变换提供保障。

4 结束语

本设计充分体现A/D采集模块的特点,整个设计结构紧凑、性能稳定、抗干扰能力强,并且适用于各种工业控制场合。设计上此模块可实现四路一组的高速同步采样及多组2Msps的采样吞吐量。应用DSP高速处理器进行数据处理,可以很容易地实现实时谐波分析功能,且系统运行稳定性和所能达到的精确度均优于传统的以微控制器为核心所构成的系统。

上一篇:安捷伦新型模块化功能测试系统具有无与伦比的汽车电子测试覆盖范围与测试速度

下一篇:风力发电机在线监测与诊断系统中用到的传感器