- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于嵌入式系统的桩基础检测仪的研制

1 引言

近年来,以波动应力理论为基础的桩动测技术已获得广泛应用。它的基本原理是桩顶受到桩锤冲击后,根据桩顶实测力和加速度数据分析桩的完整性。基于此种方法的测桩仪设备轻便、灵活,运输和现场安装的工作量小,测量效率高,耗时短,不易发生安全事故。

本设计利用嵌入式系统技术开发出具有实时采集数据、分析数据、本地给出处理报告功能的测桩仪。仪器具有自动调节信号增益、数据采样速度高、数据自动存储及整机自动化程度高等特点。

2 系统问题分析

2.1 现有测桩仪

测桩仪完成数据采集" title="数据采集">数据采集

与处理的工作现场环境一般较为恶劣,弥漫着各种干扰(来自系统内部和外部),当被测信号很微弱时,有效数据就会被噪声“淹没”,导致数据采集与处理误差很大,可靠性降低。

有些测桩仪配备的采集系统的频响范围过窄,桩多处断裂时动测曲线无法反映,超浅部的桩身缺陷会导致测试盲区。

现有的一些仪器大多采用基于软件的程控放大方式,降低了数据采集系统的采样速率,对于快速的小信号无法准确反映。

2.2 解决方法

针对干扰信号,本系统在数据采样前的硬件上首先将信号接入模拟低通滤波器,滤除高频噪声;在数据处理" title="数据处理">数据处理

前期使用软件数字滤波" title="数字滤波">数字滤波

器对引入的特定频率噪声进行带阻滤波。具体设计时,在A/D采样前增加模拟有源滤波器进行预滤波以限制信号带宽,去掉高于1/2抽样频率以上的高频分量,防止频谱混叠。

传感器、采样/保持器、模/数转换器的参数指标对系统的频响范围有较大影响,选型时应从整体上权衡各部件的性能,寻求成本和速率的最佳值。

为了既提升测量精度又减小对测量速度的影响,系统采用全硬件的高速动态放大方式。

3 系统结构与关键技术

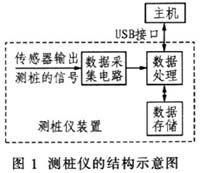

首先进行功能分析,规划出系统的体系结构,列出各构件模块,然后进行底层的具体设计,最后完成系统的整合。测桩仪的结构示意图如图1所示。

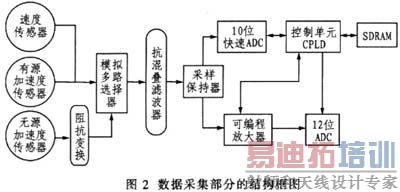

测桩仪设备包含的功能模块有数据采集、数据处理(含数字滤波、分析处理、图形显示及报表打印)、数据存储,外部还需配备击锤及传感器。测桩仪的信号输入接口有3个,分别为速度传感器" title="速度传感器">速度传感器

、有源和无源加速度传感器" title="加速度传感器">加速度传感器

,它们通过模拟多路选择器选定一路有效信号进入模拟低通滤波器。滤波后的信号通过采样保持器后分为二路,一路进入低精度的模/数转换比较器,实时监测信号的幅值范围并报告给控制单元" title="控制单元">控制单元

,由其产生出相应的放大系数,对可编程放大器进行设置。另一路首先通过可编程放大器进行放大,然后进入高精度模/数转换比较器,最后由控制单元设定放大系数并与放大信号同步存储。数据采集部分的结构框图如图2所示。

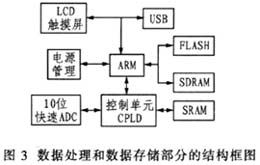

一个采样周期后,控制单元向处理器ARM申请中断,处理器读取数据信息后完成数据的预处理分析和图形显示,通过USB接口向上位机传输数据,以获得完整的数据分析和报表打印服务。数据处理和数据存储部分的结构框图如图3所示。

采样过程中,数据的放大倍数与测量结果的同步时序控制是硬件需要解决的关键问题。数字滤波、数据分析计算和指数放大显示是软件需要解决的关键问题。

3.1 硬件相关

整个系统的结构包括数据采集、数据处理和数据存储,下面仅对部分关键技术进行讨论,随后描述控制单元的实现。

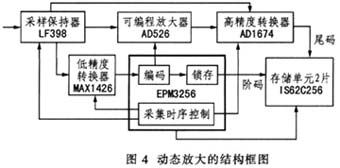

3.1.1 动态放大技术

由于反射波幅值变化范围大,为了使小信号也有较高分辨率,采用硬件自动实时选择信号的放大倍数,增加系统的动态范围。在最大量程下,进行一次低精度A/D转换,控制单元CPLD(复杂可编程逻辑器件)读取转换值,编码存储进16位SRAM(2个IS62C256级联),并给放大器送出当前信号的增益系数。由于设计中采用二个可编程放大器AD526串接,增益为1、2、4、8、16、32、64、128、256九种,所以对于双极性信号,低精度ADC必须采用10位以上的模/数转换器才能满足所有增益的放大。选用MAXl426型10位模/数转换器作为低精度ADC,AD1674型12位模/数转换器作为高精度ADC,以降低开发成本。动态放大的结构框图如图4所示。

利用CPLD的硬件可编程特性,将数据的采样放大与模/数转换时序设定为流水线方式,高精度ADC转换数据时,浮点放大电路同步放大下一级信号。

后级12位ADC进行模/数转换时,前级的10位ADC又开始了下一轮数据的转换。在本设计中,12位高精度ADC转换的时间长于前级放大环节的时间,流水线的耗时主要在后一级上。

3.1.2 超前触发技术

为了保证采样波形的完整性,系统设计中利用CPLD与SRAM实现超前触发,即在触发前预存定长的信号转换数据。将触发电平编码以数字形式锁存在CPLD内部,与经过低精度ADC转换的数字信号进行比较。当满足触发条件后CPLD能记录下SRAM内当前数据的地址,同时启动定时计数器,计数器满后停止向SRAM内填充数据,一次采样操作完成。

3.1.3 NandFlash的启动过程

处理器选用带有丰富控制器ARM9内核的S3C2410。结合处理器上运行嵌入式操作系统的特点,选用64MB的Nand Flash K9F1208UOM存储程序代码和受掉电保护的数据,2个16位的HY57V561632级联组成64 MB的SDRAM存储运行程序代码和数据。系统的多阶段启动过程(Bootloader)如下所述:在第一阶段,处理器首先进行硬件设备初始化并加载第二阶段的运行代码至SDRAM,设置好堆栈后转入第二阶段的入口;第二阶段首先初始化所要使用的硬件设备,然后检测系统内存映射关系,把操作系统的内核映像和根文件系统从NandFlash加载数据到SDRAM的内存空间中,再为内核设置启动参数,最后调用系统内核,完成操作系统的启动过程。

3.2 相关软件

3.2.1 嵌入式操作系统的移植

该系统平台基于嵌入式Iinux操作系统设计,充分利用其强实时性和可移植性的特点。移植操作系统以适应于本硬件平台需要编写二部分代码:一是前文所述的启动代码Bootloader;二是内核代码与硬件密切相关的部分。内核代码与硬件密切关联的代码大部分位于arch子目录中,而附加设备的驱动程序通常位于drivers子目录内。

3.2.2 数字滤波方式

系统对速度传感器与加速度传感器的二种输入信号采用不同的滤波过程以适应其各自的特点。对于速度传感器的安装谐振场振荡器而言,恰当的数字滤波可以与之互补,从而拓展传感器的使用频率范围。因此这种信号的数字滤波方式是在频域分析的基础上,以恰好滤去安装谐振场振荡器为原则。可通过比较滤波前后幅值谱曲线的方式来验证滤波是否恰当,选择安装谐振峰左侧第一谷处频率作为低通截止频率;用于加速度传感器的数字滤波,其使用原则与速度传感器一样,但它的滤波过程是在积分之后进行。

3.2.3 显示处理与分析和测试程序

系统首先提供测试结果的原始曲线,用来反映现场测试时的原始记录状态。但是原始曲线未经任何处理,常常不能清晰地反映桩身完整性特征。因此,为了准确地分析测量结果,单一的原始曲线是不够的,还需要经过具有物理意义的处理手段进行处理。这些处理手段包括旋转、指数放大和平滑等。

另一点值得一提的是,为了提高时域分析结果的准确性与可靠性,以及分析所用处理手段的合理程度,提交曲线可以引入频域曲线与频域分析结果。对速度传感器而言,它为原始的幅值谱,对加速度传感器而言,它应是积分谱。

4 结束语

本文提出的设计方案具有低成本和宽频响的特点。由于实验条件限制,数据采集的速度瓶颈是2个模/数转换器的转换速率,如果选用高速率的模/数转换器,并将高精度模/数转换器选为16位,系统的性能将得到大幅度提高。

上一篇:亚洲地区最大的测试测量年度盛会

下一篇:CMOS

像传感器解决方案解决测距技术难题