- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

工程师用电子侦探Chipworks寻找专利漏洞

想知道一部iPad里有什么东西吗?更明确地说,你是否想知道iPad的芯片里都有什么?Chipworks工程师们的工作就是尽力去寻找真相。他们会拆解手机这类电子装置,对IC作反向工程,获得完整的逻辑图,以发展竞争性智能。有了Chipworks团队的辅助,客户可以跟踪自己竞争对手的发展,寻找专利的漏洞。

苹果之前发布了iPad,Chipworks对iPad的研究部分体现了该公司的能力。例如,仅在iPad上市的一天后(今年4月4日下午),Chipworks的伙计们就推测出:苹果采用了保守和低成本的技术,其重点在于工业设计和可用性。

Chipworks发现的一些细节是:苹果没有采用iPhone 3G上采用的德州仪器公司全能触摸屏控制器,而是使用了iPhone 2G上的三芯片方案;两片三星K9LCG08U1M 8GBMLC NAND闪存芯片提供了16GB存储器;苹果A4处理器的封装与前代苹果iPhone处理器相同,采用了层叠式封装技术(两个DRAM片芯已确认是三星的128MB器件);还使用了意法半导体公司的加速度计设计。

就此而言,iPad似乎更像一个大号的iPod,而不是小型笔记本。正如Chipworks高级技术分析师Dick James所言:“基本上,iPad是一台增强了显示屏和有更长电池寿命的iPod Touch。iPhone 2GB的触摸屏结构也许反映出了设计启动的日期,我们可能会看到TI进入下一代iPad设计,尤其是我们看到同样的TI芯片出现在了最新iPhone、iPod Touch和Magic Mouse中。”

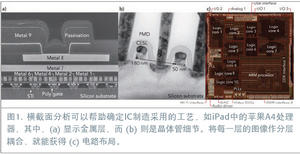

当然,很多组织都在做拆解工作,也包括兄弟杂志《EDN》“真相”栏目的编辑。而Chipworks对产品中IC的研究工作与众不同。例如,图1表示出了iPad中所用苹果A4处理器的细节:图1a是器件的一个横截面,图1b是晶体管细节,图1c是版面布局。

从MEMS到RF功率放大器

Chipworks决定拆解A4并作反向工程的部分原因是苹果围绕iPad的大肆宣传,也有对该产品的好奇心。但Chipworks兴趣与能力远远超出了对热门消费产品的简单拆解,而是要对多个IC作反向工程。Chipworks为《EDN》“IC内幕”专栏撰稿的工程师已经阐述了很多IC的反向工程,包括电池充电器IC、自供电RFID器件、LED驱动器、CMOS RF功率放大器、采用MEMS的惯性传感器,以及DDR SDRAM等。

为最新一期“IC内幕”专栏撰稿的是Dick James与Randy Torrance,他们领导着Chipworks技术智能集团下专长于反向工程的电路分析团队:“在半导体行业,RE长期以来就被公认且被用做竞争智能的一部分。通常它广泛用于产品基准,以及支持专利许可活动….半导体技术的进步,尤其是大量器件与功能在单个元件中的集成,已使RE从故障分析实验室中的苦差事,发展成为一种专门的工程专业类别。”(参考文献1)

无损伤地显露片芯

为了更多地了解Chipworks,我与Torrance以及Chipworks的工程师Sinjin Dixon-Warren、Neal Stansby和Darko Veselinovic作了交谈。Stansby说反向工程一般开始于一个“前端”工作。

Stansby是Chipworks的研发集团经理,他解释说:“一个封装里可能有一只或多只硅片,我们要使它们显露出来,而不造成损坏。”他描述了多种实现技术:“如果是塑料封装,我们会将其投入一杯酸性液体中,就搞定了。如果是陶瓷封装或金属封装,就更具挑战性,也更耗时。我们有一本秘技,使用不同类型的设备,能使实际片芯从封装中露出,而不损坏它。”

片芯露出封装后,电路反向工程就要顺序地暴露出互连层、器件层以及基层。Stansby说:“我们顺序地暴露出互连层,最终是器件层,采用的方法是暴露特征而不损坏它们。我们面临的挑战是特征尺度越来越小,因此也日益脆弱。大多数情况下,芯片尺寸也越来越大。如果我们要暴露一只有12个金属层芯片的整个第7金属层,去层工作就要极端平整,否则,我们就会在一个区域看到第7层,而在其它部分看到第6层和第8层。”他解释说,Chipworks会根据芯片结构所使用的材料,如是铜互连还是铝互连,以及是普通的电介质还是低k电介质,采用机械抛光与干、湿式腐蚀相结合的方法。

对于新制造厂生产的器件,或采用了Chipworks工程师以前从未处理过的工艺节点的器件,要获得正确的去层方法可能非常困难。Stansby补充说,即使有过类似器件的经验也不能保证工作的快速成功,他指出:“也许你认为,如果上周刚做了一个0.13μm的TS MC芯片,这周又有另一颗,那么它的去层过程也许没什么区别,但实际上不是这样。某一层上走线密度这类特性都可能影响到腐蚀或抛光的速度。或者,也许这周的芯片在制造时为了满足某种特殊设计目的而放弃了某些设计规则。”所幸,Chipworks的工艺分析团队可以提供帮助。

工艺分析

工艺分析是Sinjin Dixon-Warren的专长,他是Chipworks技术智能业务部门的工艺分析小组经理,他通过截面分析来研究工艺的细节。Torrance说:“我们开玩笑说,Sinjin的工作是看横截面,我的工作是看各层平不平。”他补充说,事实上,大多数工艺工作要采用截面分析,而Torrance的工作中心则是对各层的照像和分析。

Dixon-Warren称,他的小组主要是做CTI(竞争性技术智能)分析,另外也支持智能产权小组,做寻找相关专利漏洞的工作,例如一个过孔连接到一根金属线的方式,或晶体管构造方式等结构特征。该小组还可以查找描述某些东西制造方法的相关工艺专利。这类专利漏洞可能很难证实,因为相近的最终结构可能源于完全不同的制造工艺。然而,Dixon-Warren称Chipworks的研究专注于CTI,可以推动进一步的协商或诉讼。

Dixon-Warren小组工作还有另外一个作用,即它收集的信息有助于确定最佳的去层方法。例如,Stansby称工艺分析小组可以确定出最上面两个金属层为3μm厚,余下一层厚度是1μm,这个信息可以帮助Chipworks工程师计算出最佳的腐蚀时间和抛光时间。

显微镜是Chipworks工程师的关键工具。Stansby说:“你可以认为我们随时会用到任何类型的显微镜。”优质显微镜可以帮助确定出感兴趣的特征,从而对截面作进一步研究。SEM(电子扫描显微镜)提供了更高的放大倍率,并且Stansby称TEM(透射电子显微镜)“可把你带到原子层级,提供也许是最高的放大倍率。”Chipworks还采用了扫描电容显微镜,这是一种原子力显微镜,它对硅掺杂的类型尤为灵敏。

Stansby指出:“这是一种相当强大的反向工程技术,我们能够以相当好的三维分辨率,看到硅片的掺杂区。”

图像的拼图

当承担一只芯片的反向工程时,Chipworks会试图给每层提供一个样本。Stansby说:“对一个5金属层的器件,我们会得到7个层,即5个金属层,加上我们看到实际晶体管的多晶扩散层,以及可以区分出p和n器件的基层。”

一旦分层工作成功地暴露出了一个层,下一步就是为它照像,这步有两个难点。Stansby说,首先,由于特征变得越来越小,放大倍率必须越来越大,才能解析出有用的特征。

Stansby说:“对于我们按照需要倍率购买的任何显微镜,视场都是有用区域中的一个太小、太小的部分。所以,我们解决问题的办法是以略微重叠的方式,为每层拍摄一个二维的马赛克图,然后再将它们拼到一起,获得一个等效的大图。”他说,为了研究一个3层 13层的器件,要为每层拍照6万张照片,这种事情并不罕见。

获得全部图像可能非常耗时。Stansby说,SEM通常是设计用于分析实验室,而Chipworks则要将它们用于大批量的生产。他说,公司采用的是商用SEM,但它们经过大量修改,以满足Chipworks对吞吐量的要求。

Stansby解释说,精度与准确度也很关键。“假设我们要为金属层6做一幅很好的综合图像;我们打算将其与金属层5的图像重叠,我们希望重叠有足够的精度,这样才能通过两层之间的一个过孔去追踪一根连线。”他补充说:“在200nm或300nm的走线间距下,在一个可能为5mm、6mm或10mm宽的区域中,对误差的容限大约为100 nm。从百分比看,它们必须极端精确,完全没有失真,这样才能准确地追踪连线。”所以,除了需要提高吞吐率以外,他说,“SEM还必须经过优化而有极高的精度,才能使一切都处于一个非常可靠的坐标系内。”

简化了工作的软件

Chipworks的软件将所有图像组合到一起,并使用所有层对齐,这个软件名为ICWorks。通过ICWorks,用户可以在一台CAD工作站上检查所有层,放大或缩小,在各层之间上下切换,查看全部过孔。Torrance说,图象非常类似于设计工程师或布局工程师所见到的那样,不过ICWorks用户看到的是实际图像,而不是一个CAD布局工具上经过美化的方块图。

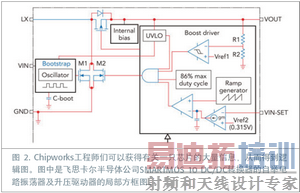

此时,Chipworks工程师们要在图像上作标注,确定所有器件与接线。标注工作完成时,ICWorks工具会自动输出一份逻辑图(图2)。Torrance说:“不幸的是,它输出的逻辑图是一个尺寸大得惊人的平板式逻辑图”,一般的芯片设计者几乎无法看懂。不过他补充说,Chipworks有这样一些工程师,“他们可以创建 分层图,做出一组逻辑图,这样其它工程师就可以阅读和理解了。”

对于Chipworks的客户,Torrance说:“现在,我们送您ICWorks工具,有了这个工具,你可获得所有图像,你可获得我们做的全部标注,你还可以获得我们做的全部逻辑图。ICWorks使你能够在所有这些之间作交叉定位,这样可以在逻辑图中选择一只器件,然后通过快速交叉定位,在所有不同层中看到它的图像,以及它的制造方式。”

系统级的显微术

显微镜是工艺分析与逻辑图提取的关键工具,用系统级的非破坏式拆解就可以作电子测试。系统工程师Darko Veselinovic解释说:“在某些项目上,我们会将拆解工作与对一只仍运行的片芯的显微术相结合,”探查那些通过分层图像获取以及逻辑图提取过程而定位的感兴趣信号。被监测的片芯可能在其原来的PCB(印刷电路板)上,或在一个专门制造的测试夹具上。

Veselinovic指出了捕获一个待查系统信号的一些挑战:“以一个汽车应用为例。如果我们能够有某种方式,以固定方法操作汽车,而不必须开动它,那么就简单些了。我们可以做一些延伸电缆,这样就能将一个控制盒放在便于获得有用信号的地方。”

不过,在其它情况下,控制器与汽车之间的机械链接也许会使这种方式不可行。Veselinovic表示,在这种情况下,“我们会试图在什么也不损坏的前提下打开盒子,然后可能在盒子的一个地方钻个孔,这样就可以把探头放进去。然后,我们会尝试将一切组装起来,让它正常工作,而盒子并不比原来大,我们会试图把它放到原来的位置。”

当系统工作时,可以用外接测试测量设备监控信号的工作。Veselinovic称,有时候,这种监控需要他的小组建立一个FPGA前端,用于将信号传输通过一个高噪环境,或长距离传输大量信息。他指出,Chipworks会充分利用原设计者提供的任何接入法,如一个JTAG端口。

反向工程的哲学

Torrance称他曾有机会在一系列场合谈论反向工程,包括本地IEEE分会的会议,他提到一个经常被谈及的问题,“这合法吗?”实际上答案是正面的。Torrance解释说,在美国,《半导体芯片保护法案》对反向工程做了保护,允许该技术“用于遮罩产品或电路所包含技术的教学、分析或评估。”他说,日本、欧盟和其它管辖区域也存在着类似的法规。

Torrance说他还发现“很多人似乎并不知道这是可能的,即可以每次从一只芯片上获得一个层,对它作实际的拍摄,看清一切。我想,很多设计人员可能认为他们对芯片作了封装,没有人能够看到里面的内容,而这不是真的。”

阻挠反向工程小组研究的力量是一直存在的。Stansby说:“如果你浏览一下专利世界,就会发现各种人都在申请一些试图增加反向工程难度的制造技术专利,例如,看上去像过孔而并不做连接的结构。但实际情况是,我发现公司有史以来从未在实际芯片中看到这些,至少商用芯片中没有。”

Torramce补充“偶尔我们会发现一个有金属板的层,它似乎完全没有功能作用,下面有一些电路。我们可以想到的唯一理由是设计者试图将电路隐藏起来,不想让人看到,但这对我们根本没有妨碍。”

参考文献

1. Torrance, Randy, and Dick James, "IC reverse engineering-a design team perspective," EDN, March 11, 2010. www.edn.com/icinsider.

上一篇:并购&

创新Fluke领跑计量校准仪器市场

下一篇:EMC的EM仿真:控制干扰