- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

PXI总线数字输入/输出模块的设计与实现

摘 要: 描述了基于PXI总线的数字输入/输出模块的特点和原理,以及用PCI9030接口芯片和FPGA器件实现的PXI总线接口电路,提出了数字输入/输出电路及高精度延时补偿电路的实现方法。实践证明系统原理和硬件设计是成功的。

关键词: PXI总线 数字输入/输出 PCI9030 FPGA器件

PXI总线是PCI总线的一种扩展总线;PXI总线是设计用户测试系统的标准选择,可以灵活地组建自动测试系统。PXI总线具有标准、开放、结构紧凑、数据吞吐能力强、模块可重复使用、众多仪器厂家支持等优点,其应用领域越来越广泛。

基于PXI总线的数字输入/输出模块用来接收和发送来自被测器件的图形数据,通过与预期的正确结果进行比较,完成被测电路的功能测试。用它组建的测试系统,具有测试速率快、可靠性高和诊断精度高等特点,能够满足不同电子产品测试的要求,可广泛应用于数字系统的在线故障诊断、总线仿真、微处理器仿真以及电子装备故障诊断等。

1 数字输入/输出模块的工作原理

数字输入/输出模块采用PXI总线测试平台,具有四通道32路,每个通道存储深度为64K,可独立编程为输入或输出通道,时钟频率最高可达20MHz,存储的图形数据支持单次、循环和跳转三种输出方式,输出电平兼容COMS/TTL电平,输出摆率不超过±5ns,输出电平脉冲宽度可编程调节,其范围为6.25ns×4~409.6μs×1024,测试图形的装载速率,可以达到10MByte/s,能够在很短的几秒钟内完成图形数据的装载及数据的输入/输出。

数字输入/输出模块用于数字测试的基本方法是:从输入端施加若干测试激励,记录并观察其相应的输出响应,并与预期的正确数据进行比较。如果两者不一致,则可能有故障存在。同时对有故障的电路板进行进一步的诊断,找出故障发生的原因,进行维修,这就是通常所说的功能测试。对于一个具有n个输入/输出端口的电路板来说,完全测试需2n条测试激励,如果n较小,可以用2n条测试激励进行完全测试;但当n较大时,则需要有多路的测试激励同时进行工作,这就需要数字输入/输出模块能够提供尽可能多的输出通道,满足故障测试的要求。

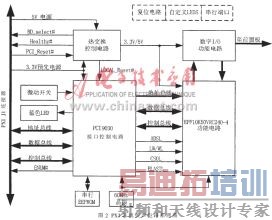

数字输入/输出模块的工作原理如图1所示,整个电路的实现由PXI总线接口电路和功能电路两部分组成,PXI总线接口电路采用可编程器件及PCI9030接口芯片来实现接口功能;功能电路部分含有四个通道,每个通道都可以指定为输出激励模式或记录响应模式。输出激励模式的作用是:在主控计算机上生成激励图形数据,根据图形的宽度、长度、输出方式确定所需端口个数;对所用端口生成相应控制信息,通过PXI控制器将图形数据和控制数据传给图形I/O" title="I/O">I/O

模块,并存入各个端口的图形存储器中;设置起始地址,选择激励时钟,设置图形存储器的工作方式" title="工作方式">工作方式

为输出方式;最后由上位机发送“运行”命令,图形I/O输出激励图形数据到DUT端口。记录响应模式的作用是:根据所要记录的响应图形的宽度、长度确定所需端口个数,对所用端口生成相应控制信息,通过PXI控制器将控制数据传给图形I/O模块,并存入各个端口的图形存储器中;设置起始地址,选择响应时钟,设置图形存储器的工作方式为记录方式;最后由上位机发送“运行”命令,使图形I/O接收来自DUT端口的响应图形数据并存储在图形存储器内。记录结束后上位机从模块读取响应图形数据,以供分析研究使用。

存储器通过PXI总线从上位机下载激励图形数据,单次或循环输出激励图形数据,接收来自DUT端口的响应图形数据并保存到图形存储器中。地址发生器为PXI总线读写图形存储器时提供地址,在输出或记录时实现图形I/O从任意地址进行任意长度的单次或循环输出数据。激励图形数据从图形存储器输出后经触发器进行同步直接输出。所有的控制切换都由控制逻辑完成,这些逻辑在FPGA上实现。

每个端口的控制寄存器包括图形存储器地址、转移目标地址、端口数据总线、配置和状态/时钟源等寄存器。图形存储器地址寄存器用于设置图形存储器的当前地址;转移目标地址寄存器用于循环执行;端口数据总线寄存器负责PXI总线和图形存储器的通讯,用于激励图形数据加载" title="加载">加载

、校验和响应图形数据的转储;配置寄存器用于图形存储器的工作方式设定;状态/时钟源寄存器控制图形发生器的起停,选择图形发生器的时钟。

2 PXI总线接口电路

PXI总线接口电路是采用PCI9030接口芯片来实现的,PXI总线接口电路主要由热交换控制电路、PCI9030接口控制电路、FPGA控制电路和数字输入/输出功能电路等组成。采用

Altera

公司的FLEX系列的EPF10K50VRC240-4 FPGA实现部分PCI接口逻辑电路及功能电路,采用PCI9030实现PCI总线的接口逻辑电路。PCI9030 具有最灵活的局域总线,允许各种存储和I/O 设备选择多种接口。PCI9030以PLX在Compact PCI上的经验为基础,是首个支持Compact PCI热交换的目标设备。它符合PCI V2.2规范的32位33MHz 目标接口芯片,使PCI 突发传输速度高达132兆字节/秒;具有高达60MHz的局域总线操作,使突发传输速度高达240兆字节/秒的特点;可编程局域总线操作,支持非多路复用和多路复用32 位地址/数据协议,并支持动态局域总线宽度控制,以通过从属访问方式访问8位、16位或 32位设备;其9个可编程的通用I/O,可用于对功能电路进行控制。PXI总线接口电路原理图如图2所示。为了减小单板上的PCI总线的信号线分支对总线的影响,必须对总线信号进行串联电阻匹配。PCB的布线特征阻抗应设计为65Ω±10%,匹配电阻阻值为10Ω。这里仅用到J1连接器,需要加串联匹配电阻的信号为:AD0~AD31、C/BE0#~C/BE3#、PAR、FRAME#、IRDY#、TRDY3、STOP#、LOCK#、IDSEL、DEVSEL#、PERR#、SERR#、RST#、INTA#、INTB#、INTC#、INTD#。PXI总线的信号线长度,必须符合Compact PCI规范的要求,串联电阻的Stub(短线)长度应进行限制,Stub长度越短,Compact PCI对总线的冲击越小。PXI总线的信号线长度限制如图3所示。在单板上,对预充电的信号,从接插件J1(或J2)插针到PCI9030接口器件引脚,总的信号线长度应小于38.1mm,其中,从接插件插针到串联电阻的PCB连线长度应小于15.2mm,预充电电阻的Stub长度最好是零,最长不能超过2.5mm。

PXI总线及FPGA控制电路具有如下功能:①内部集成了功能电路所需的各种寄存器,分别为状态/控制寄存器、校准ROM寄存器、序列地址寄存器、跳转地址寄存器、功能配置寄存器、输入输出控制寄存器、状态/时钟源寄存器、时钟校准寄存器。②利用PXI总线提供的星形触发总线及局部总线,完成时钟信号" title="时钟信号">时钟信号

的传递,减少了时钟信号到达各个模块的传输延迟" title="传输延迟">传输延迟

,传输的时钟信号电平为ECL/TTL电平;③具有16位数据线的传送能力,通过对某一地址的读、写操作,完成图形文件数据的加载、记录存储器存储的响应图形数据;④监视功能电路的中断请求,可通过软件设置和外部跳线来设置中断级别,向PXI总线发中断请求信号,完成中断菊花链的传递,并将逻辑地址放到数据线上;⑤根据各个通道对应寄存器的配置,译码实现各个通道的控制信号,并确定其工作方式。

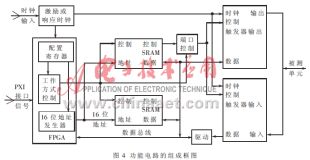

3 功能电路的实现

数字输入/输出模块的功能电路的组成框图如图4所示,它能实现如下六种工作状态:①图形文件的加载。通过对数据总线寄存器的写操作,在16位地址发生器的作用下,将8位的图形数据和4位的控制数据装进容量为64K×4的三片静态存储器中。②图形文件的读取。在对响应图形数据记录完成后,通过对数据总线寄存器的读操作,可以获取某一地址段或全部地址的图形数据,读入到指定的文件中,并与预期正确的图形文件相比较,判断被测单元的性能状态。③图形数据的激励。图形文件加载完成后,在激励时钟的作用下,同步16位地址发生器和输出触发器,输出某一地址段或全部地址的图形数据,或跳转到某一指定地址的数据,在输出端口输出高电平、低电平或高阻状态。④图形数据的响应。当激励时钟加在输出端时,精确计算图形数据经往返的通道和被测单元所产生的延迟T,使激励时钟延迟相同的时间T,形成响应时钟,加到数据输入端,同步记录激励所产生的响应数据,在16位地址发生器的作用下,存储在64K×4的静态存储器中,完成图形数据的记录。⑤PXI总线数据直接输出。PXI总线数据通过软件的写操作直接加到输出触发器,而不经过静态存储器存储。⑥PXI总线数据直接输入。PXI总线数据通过软件的读操作。直接访问输入触发器,而不是读取静态存储器存储的响应数据。

数字输入/输出模块使用的激励或响应时钟经PXI局部总线加到时钟选择单元。当通道定义为输出时,通过多路选择器选择六路时钟信号中的一个,加到输出通道上;当通道定义为输入时,则选择响应时钟。激励时钟和响应时钟由时钟模块产生,响应时钟是激励时钟经N×6.25ns的延时所得,以补偿激励信号经被测电路和往返通道所产生的延迟。同时,同一时钟信号加到同一模块的不同输出端,也会产生传输延迟,采用可编程延时器AD9500产生精确延迟时间,补偿不同通道间的传输延迟。延迟补偿电路采用MOTOROLA公司的MC10H系统的ECL电路,具有速度快、逻辑功能强、扇出能力高、噪声低、引线串扰小和自带基准源等优点。先将时钟信号由TTL电平转换为ECL电平,由于AD9500具有2.5ns~10μs的可编程延迟范围,它由8位数码编程产生所需要的延迟信号,补偿不同通道间的传输延迟,补偿后的时钟信号再由ECL电平变换为TTL电平,加到各个输出通道,记录或响应图形数据。

基于PXI总线的数字输入/输出模块采用了可编程器件和ECL电路,实现了图形数据的输入和输出,基本上达到了HPE1451/1452输入/输出模块所具有的功能。该模块具有可靠性好、精度高、功耗小的特点,适用于要求高质量数字激励/响应测试并保持一定时序关系的应用场合。它能模拟信号图形,也可以通过编程产生DUT正常工作所需要的数字图形、控制、应答及时钟等信号,可广泛应用于数字系统的在线故障诊断、总线仿真、微处理器仿真以及电子装备故障诊断中。

参考文献

1 奚文骏,冯玉光. PXI数字I/O的工作模式及软件实现[J]. 电子产品世界, 2002(12): 32~35

2 万世豪. PXI技术发展与近况[J]. 今日电子, 2003(6): 53~55

3 PCI9030 Data Book.PLX Technology Inc. 2000.4

4 王建永,李德华. PCI9030及其应用[J]. 计算机与数字工 程,2003;(1): 22~27