- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

基于NI LabVIEW 2010和NI RIO构建精确定时的嵌入式系统

1、介绍

在构建嵌入式系统时,不论是为了确保控制循环能够可靠的执行,还是保证I/O信号能够被及时响应,或是让处理速度达到系统应用的要求,定时都是其中的关键。构建一套可以满足定时要求的系统,首先从硬件开始进行选择,必须在尺寸、功耗、处理能力和延迟等方面进行很好的平衡。另外,嵌入式系统的软件在执行调节、中断响应和计算任务之间的时间平衡几个方面扮演着重要的角色。

在考虑定时性能的前提下进行嵌入式软硬件集成将是一件极其耗时的挑战。但是,在NI LAbVIEW 2010软件平台和RIO硬件平台的帮助下,构建一套可以满足绝大部分系统应用需求的可靠的精确定时系统所需要付出的代价将极大降低。继续深入下去,了解集成了实时CPU和FPGA的NI RIO硬件系统,以及定时特性是如何与LabVIEW 2010无缝集成的,可以帮助工程师、科学家和嵌入式设计人员们利用这套硬件系统构建出健壮的实时响应系统。

2、集成实时CPU和高性能FPGA的NI RIO硬件

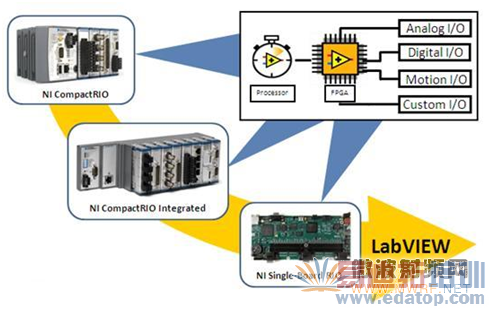

NI嵌入式硬件的目标系统是基于RIO架构的,包括了一个一般用于运行实时操作系统的CPU和一套或多套FPGA。在这样的集成架构下,用户可以在FPGA上完成那些需要纳秒级定时精度或者大量并行的任务;在CPU上完成诸如浮点计算等密集计算任务。FPGA和CPU之间通过PCI总线进行通信,通过NI-RIO驱动模块提供的直接明了、功能强大的数据传输接口, 使用LabVIEW或C可以很容易的进行相关开发。

最终的结论是:NI-RIO是可以适用于范围广泛的嵌入式原型设计,并且具有很高灵活性的平台。同时,由于NI-RIO框架是很多不同NI硬件目标系统的标准架构,例如NI Single-Board RIO和NI CompactRIO,用户在部署软件时,不论是坚固型系统还是经济型系统,都可以最大限度地实现代码的复用。

图1. NI-RIO嵌入式设备均基于集成了CPU、FPGA和模块化I/O的统一架构

例如,Ventura市航空中心使用LabVIEW和NI Single-Board RIO开发了一套火情监控系统,用于在联邦快递公司的运输机上防控火灾。在这套系统中,实时CPU负责运行确定性控制算法、网络通讯和数据记录,FPGA硬件上则执行其他的关键任务。

3、LabVIEW 2010和内置的定时特性简化了确定性可靠系统的编程

LabVIEW不单可以使用图形化的编程界面来编写目标CPU(包括了运行实时操作系统的CPU)和FPGA(包括RIO目标硬件上的FPGA)程序,同时LabVIEW图形化编程语言本身也是基于定时和同步概念而设计的。下面的一些例子将说明,LabVIEW结合Real-Time模块和FPGA模块是如何让嵌入式系统的定时变得简洁明了的。

4、LabVIEW Real-Time模块集成的定时特性

使用Real-Time模块和Timed Loop进行确定性的闭环系统编程

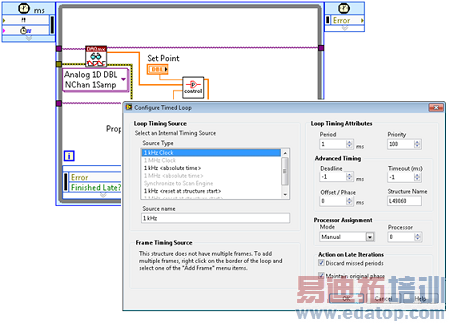

LabVIEW 2010 Real-Time模块把LabVIEW图形化编程扩展到了NI实时硬件系统(包括RIO设备)特定的第三方PC上。根据使用的目标硬件不同,LabVIEW Real-Time模块会自动在目标硬件上部署与标准的VxWorks或ETS实时操作系统相对应的组件,以保证确定性和精确的实时性。

当使用LabVIEW Real-Time模块进行闭环控制系统的编程时,通过使用Timed Loop,只需要轻点几下鼠标,就可以实现周期性执行代码,硬件控制循环速率同步,定义多种循环执行优先级,甚至可以指定某一循环在某一个CPU内核上执行。另外,用户还可以选择KHz、MHz或者自定义的外部时钟来作为循环定时的基准时钟。

图2. LabVIEW Timed Loop可以让用户通过简洁明了的方式实现配置循环定时、通过硬件I/O进行同步、控制实时代码执行优先级、指定代码执行CPU内核等

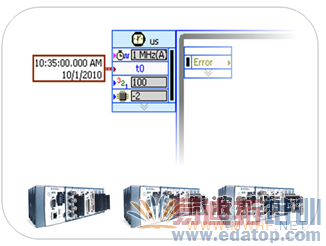

在多系统间实现Timed Loop的同步

在使用LabVIEW Real-Time模块编程的嵌入式硬件设备上,用户可以使用IEEE 1588同步协议进行多系统间的同步,以保证给定的任务在多系统上是同步执行的。根据用户使用的硬件设备不同,IEEE 1588同步协议可以通过软件、硬件或者软硬结合这几种不同方式来实现。

使用LabVIEW Real-Time模块实现多硬件设备间的软件同步,将Timed Loop设置为使用绝对时间源即可。在设置好Timed-Loop后,只需要再连接一个起始时间戳,然后选择运行,就可以在多硬件设备间同时开始循环的执行。

图3. 用户可以使用LabVIEW Timed-Loop来实现IEEE 1588同步协议,在多个分布式的嵌入式设备中实现同步控制(上图为NI CompactRIO)

使用NI Real-Time执行跟踪工具包进行定时的细节分析

在LabVIEW Real-Time模块下使用Real-Time执行跟踪工具包,可以获取线程和子VI的执行时间、优先级、继承关系等多种详细信息。通过这套工具包,不但可以帮助用户优化实时程序的执行情况,更可以帮助用户发现诸如优先级设置不当、资源竞争等潜在的不稳定因素。

在实时硬件上确定性的运行m文件

如果已经有了现成的m文件,用户可以通过LabVIEW MathScript RT模块,在使用LabVIEW Real-Time模块编程的嵌入式系统中使用这些代码。这种方式从根本上改变了以往从m文件到实时硬件代码的复杂而繁琐的迁移过程,使其变得简洁而迅速。只需要将用户的m文件通过MathScript节点嵌入到LabVIEW图形代码中,再在LabVIEW项目中将其拖放到实时硬件上,整个迁移过程就完成了。

5、LabVIEW FPGA模块内置的定时特性

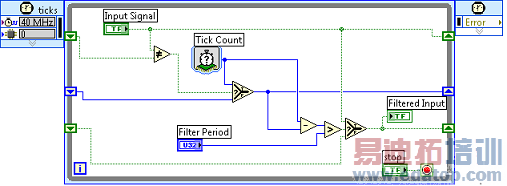

使用单周期定时循环优化FPGA程序

LabVIEW 2010 FPGA模块中的单周期定时循环移除了循环内部的寄存器,用户可以在其中最优化地运行与之相兼容的代码。这项措施可以使那些需要在硬件上可靠运行的关键操作达到最高40MHz的循环速率。另外,在单周期定时循环内执行的代码占用的FPGA资源更少,从而可以节省出更多的资源给其他的任务。

图4. LabVIEW FPGA模块中的单周期定时循环可以让用户的这部分代码达到最高40MHz的循环速率

使用循环定时器来调整FPGA代码的执行

想要在FPGA上周期性地执行操作其实很简单,只需要在LabVIEW FPGA的代码框图里添加一个循环,然后在其中放置一个循环定时器就可以了。循环定时器的定时控制可以根据需要选择循环周期为纳秒级、微秒级或者毫秒级的不同硬件时钟作为定时基准。在默认的40MHz时钟速率下,循环定时器可以实现25ns整数倍的定时周期。

通过中断对实时程序和FPGA程序的定时进行同步

在FPGA硬件系统中,用户可以在FPGA程序中产生中断,通知实时程序各种事件的发生,例如数据采集完毕,发生错误,任务已经完成等等。使用LabVIEW FPGA模块中的相关中断函数结合LabVIEW Real-Time模块中的Wait on Interrupt方法,用户可以实现整个嵌入式系统中CPU和FPGA之间的同步。一个系统中最多能够使用32个中断。

使用关键路径高亮帮助确定系统瓶颈。

在开发过程中,确定和修正时序错误的FPGA代码是一件耗时费力的事情。为了简化这一过程,可以使用LabVIEW FPGA模块的关键路径高亮功能来突出关键路径上的每一步操作,迅速跳转到出现瓶颈的代码部分,编写更高效的代码或者流水线来对瓶颈进行修正。

图5. LabVIEW FPGA模块的关键路径高亮功能可以帮助用户迅速确定FPGA程序中的瓶颈所在

6、在您的下一次嵌入式原型或设计中使用LabVIEW和NI RIO

NI RIO硬件设备和LabVIEW由于其短周期高可靠的开发特性,已经在数以千计的嵌入式原型或工程产品中得到成功应用。当您在计划下一次的嵌入式设计时,请考虑这样一套功能强大、扩展性强的成熟系统为您所带来的时间和金钱成本上的节省,以及LabVIEW的图形化编程、内置的定时特性以及数以百计的IP内核帮助您缩短的开发周期。