- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

用实时跟踪方法调试嵌入式软件

开发新型嵌入式数字处理系统或者在对其进行故障排除时,不论它属于高速服务器还是通讯系统,都需要牵涉到三方面技术,即硬件、底层操作系统和软件设计。

硬件设计人员利用逻辑分析仪分析总线和处理器的二进制时序波形,由于它显示的是最底层硬件每个时钟周期的变化,即数字器件与总线的二进制转换情况,所以通常也称为实时硬件跟踪。

底层操作系统设计工程师也经常使用逻辑分析仪,但他们更加注重观察那些和二进制转换类似的存储指令,也就是通常所说的实时指令跟踪。如今逻辑分析仪配有一种称为反汇编的工具可完成这项任务,反汇编工具专门针对处理器或总线设计,它可以从一系列二进制信息中提取特定的处理器存储内容。

软件设计人员通常都不太熟悉硬件工具,所以他们总是避免使用这些工具。软件设计人员在电脑或工作站上用C++、VB及类似的语言编写程序源代码,并希望使用这些平台完成整个设计、调试和评估过程。他们用软件工具(仿真器和调试器)运行新的目标器件,而硬件工具如逻辑分析仪对许多软件设计人员来说总是显得格格不入。但由于现在系统日趋复杂,相互之间影响也越来越大,这种状况正在渐渐改变。

目前用得最广泛的是一种所谓在线仿真器(ICE)的工具,它可以追踪目标器件并提取出源代码。ICE是软件设计工作站中运行控制工具的一个集成组件,它监测目标器件总线的活动情况,给出源代码运行结果信息。有了ICE后,软件工程师不需要使用逻辑分析仪调试就可以完成整个项目。

然而对软件工程师来说,不幸的是ICE在有些方面的性能已落后于新一代高速处理器、存储器件和总线,速度和连接性局限使它无法独立观测现代高速总线的复杂活动,软件工程师必须使用逻辑分析仪这一测量工具来验证他们源代码的日子已经到来。

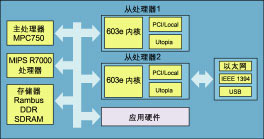

现代数字设计人员经常要与高速复杂多处理器系统打交道,如像图1所示的一个用于通讯系统的基本嵌入式多处理器系统。上述三个领域的工程师都需要能有一种工具获取长期相关数据,可从图1系统中得到数以百万计的运行周期信息,该工具要能够从主处理器及其它从处理器、存储总线和外围总线获得信息,重要的是这些信息还要和时间联系起来,以便用户可以清楚地知道所有不同的处理器和总线之间是怎样相互作用的。只有逻辑分析仪才能即刻满足所有要求。

用集成工具完成软件分析调试

软件设计人员都很理想地希望其软件评估工作两头好处都能占到,既可以在熟悉的工作站控制终端上运行逻辑分析仪的采样、显示和分析,又不需要接触到真正的逻辑分析仪。如今仪器生产厂商已开发出能满足这种要求的解决方案,可以把功能强大的逻辑分析仪(如Tektronix TLA700系列)和经验证的控制/仿真/调试工具(如Wind River的VisionClick)集成在一起。

这两种功能结合起来的性能远大于各部分功能的简单相加。如果没有执行控制工具,逻辑分析仪尽管能得到被测系统(SUT)的实时相关数据,但却不能修改CPU的状态,也不能单步执行程序,或者控制所监测的数据转换;而如果没有逻辑分析仪,执行控制工具虽然可以控制程序的每步执行情况,但是得不到满意的次纳秒级时序数据,或与时间对应的结果。

将两种性能集成在一起的开发系统能采集实时信号、存储状况及源代码,所有这一切都可以在易于操作的仿真(执行控制)工具环境下获得。有了这种工具,软件工程师就能够得到长期高精度跟踪数据,即使总线速度很高也不怕,有些逻辑分析仪的存储能力甚至达到64M。

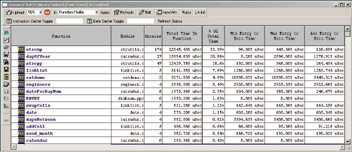

这样一来,逻辑分析仪看起来就像是控制工具的一部分,得到的数据以软件开发人员能看懂的形式显示在仿真工作站屏幕上,它可以显示出不同级别的数据,从存储器到高级源代码,还包括带有清楚时间显示的每一运行周期的功能(图2)。

值得一提的是很多逻辑分析仪没有提供足够的分辨率,无法将多个总线得到的结果正确联系起来,尤其是那些老式仪器。如有些仪器声称可以显示时序调整的波形和存储内容,但调整图形却是以多个被测系统周期显示的,当试图在一个复杂系统中追索一项数据转换时,它根本就不可能跟踪出每个周期最后将连接到什么位置,有问题出现时也难以分辨出原因和结果之间的关系。虽然从技术上说,得到的波形和存储的内容是实时追踪结果,但它太不精确了,对硬件和操作系统的故障判断没有多大帮助。

要想使显示的多种形式时序总线数据有意义,关键在于每次采样的时间信息,并要有足够的分辨率。如果每次采集的数据都带有时间信息(分辨率500皮秒),就能够把主处理器总线指令与系统外设总线的结果等同起来。

数据采样工具必须既要“宽”(有很多输入通道)又要“深”(有很大的存储容量储存得到的数据),带有扩展内存的组合式逻辑分析仪可满足这些要求,特别是当扩展内存可以从64K到64M时,能胜任ICE环境下的任何要求。

要注意逻辑分析仪产生的每一个画面都是从二进制波形信息得来的,所获得的信息及其高分辨率和时间精度都是一些基本单元,通过反汇编器和支持处理器转换成存储内容和源代码显示出来,这些都是自动按时间调整的,在多总线测试点上会导致执行延迟。

高性能逻辑分析仪和仿真器真正结合在一起后,可以为更快、更有效的代码验证和除错创造条件,例如对每一个采样点都用不同的窗口进行显示就很有用,有些用存储内容或者代码格式,而另一些则用时序格式。对于屏幕上的这些显示,每个窗口的光标都处于程序执行的同一点上,如果软件工程师在执行某一步程序时遇到问题,只需要把光标指向那一步,此时带有光标的硬件周期波形就会在另一窗口中自动显示出来,这样软件和硬件设计人员就能很容易地一起合作解决问题。

综合式仿真/逻辑分析仪对代码优化也很有帮助。软件设计师要在预定的时间内使程序运行完毕,利用仿真器屏幕上可显示实际时间值的特性(如图2),可以很方便地看出程序是否能在规定的时间内完成,其它代码优化工具如直方图还能对软件工程师提供进一步帮助。

使用集成逻辑分析仪还增加了很多其它仿真器功能,如功能概括工具可得到单个指令的最小、最大和平均完成时间,这得益于改进后逻辑分析仪所提供的时间分辨率,条件追踪工具和代码器也能进一步提高时间分辨率和采样深度。

最重要的是,综合型仿真/逻辑分析仪能使对硬件不感兴趣的软件工程师不需要触摸它就可以控制这一功能强大的采样仪器。工程师可以对分析仪进行全面控制,不管什么时候,只要按下仿真器上的“运行”按钮,仿真应用程序和逻辑分析功能都会立即执行,仿真器运行代码,逻辑分析仪则进行全面追踪,把描述目标器件活动的所有数据都存起来。逻辑分析仪的高分辨率和高精度可把每一个处理器和总线周期都记录下来,同时也有赖于这两个工具的结合,使得软件工程师仍然可以在熟悉的环境下更有效地工作。

作者:Davis Chen

区域销售经理

泰克公司

Email:davis.chen@exgate.tek.com

上一篇:利用冗余处理器提高系统可靠性

下一篇:用IC调谐器实现高性能家用网关