- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

通用控制器功能验证中的仿真应用

系统级芯片(SoC)设计服务供应商正面临越来越大的压力,需要不断增强其设计和服务的灵活性。随着灵活性的增加又要求供应商更加仔细地验证整个系统,而仿真则是验证的核心。本文以通用控制器为例,讨论仿真在功能验证中的作用。

在讨论SoC设计时,功能验证是最具争议性话题之一,可编程通用控制器也不例外。SoC主要针对便携式消费电器市场,如MP3播放器和移动电话等产品,我们对此花费大量时间进行可行性研究,力图使最先提出的要求得到优化。一个结构完整、计划周密的功能验证要占整个项目预算的40%,这样做的结果可使客户在拿到原始样品的一周内就可在器件上完成MP3音乐处理。

这类器件有几个关键要求。首先顾名思义,可编程通用控制器必须灵活才能保证能在尽可能多的便携式应用中得到支持;此外,由于它定位于便携式应用,功耗是主要考虑因素,这就要求有多种功率管理模式和功能强大且复杂的时钟方案;对很多该类器件来说,数据安全是另一个主要考虑因素,因此要用大量时间来保证存储在嵌入式存储器里的数据受到仔细的划分和保护。

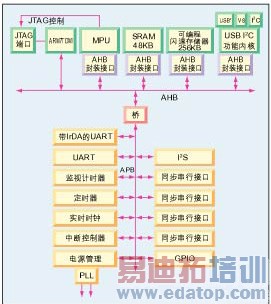

器件分为三个区:处理器子系统、通信接口和管理模块,整个结构建立在ARM7TDMI系统处理器上(图1),并有一些嵌入式存储器和外设支持处理器的工作,包括UART、定时器、实时时钟(RTC)、监视计时器和中断控制器,另外还有专用通信外设包括USB功能内核、GPIO(通用输入输出)、UART和同步串行接口(SSP)等,以便于与外部器件的连接。专用管理电路则有电源、存储器保护、安全电路、复位以及时钟管理模块等设计。

高带宽外设置于Amba高性能总线(AHB)上,包括USB内核和存储器模块。AHB最高时钟频率为64MHz,为保证AHB外设符合ARM Amba标准,可由客户提供USB,由芯片供应商与IP库供应商提供存储器模块,这就是说需要设计特殊的封装接口。另外还要设计存储器保护单元,管理存储器分区。

从上可以看出,一项很大且必须要认真对待的问题就是要从多个不同来源得到众多不同的IP,因为不可能也没必要在一个SoC(如本文所述的例子)设计中完全验证所有功能模块,毕竟采取IP复用方法的主要原因是为了缩短面市时间。

如前所述,设计既包括几种来源不同的IP,也有原始逻辑。虽然新逻辑必须要作全面测试(这非常重要),但对于已有的硅片模块,集成时只需验证其接口保证集成正确即可,这就是控制器设计方法。

综合测试

我们建立一组回归模拟模型,全面测试所有器件接口和新逻辑。但在某些时候,回归模型会因为时间运行太长而不能控制,而且结果会消失,因为被测区域经常有大量重复。由于总担心还有缺陷存在,所以很难判断何时应停止测试。

对这类设计进行模拟时通常的做法是采用分段方式。虽然在开发含有嵌入式处理器的SoC时采取这种分段模拟方式很重要,但并不能保证加上软件后该器件功能就正确,因此 人们普遍认为光靠模拟还不行。和模拟环境相比,把软件放在芯片上运行可以使芯片以更多种方式工作,并且更加彻底。

人们普遍认为光靠模拟还不行。和模拟环境相比,把软件放在芯片上运行可以使芯片以更多种方式工作,并且更加彻底。

对于可编程通用控制器之类的器件,含有嵌入式处理器所带来的好处经常会被忽略。我们在模拟环境中采取的方法是以汇编程序为主的测试,针对特定的要求,它包括用存储器映射基准测试模块,使验证过程的各方面(配置、合格/不合格检验和性能)通过汇编代码本身进行控制。

这也是我们所采纳的一个经过考验的方法,尽管用这些不同水平的模拟和增加代码范围来保证试验已经足够,但也不能忽视在器件上运行的软件,它毕竟是系统的一个有机组成部分。

在控制器开发中采用的另一个功能强大的验证技术是仿真,我们使用一个含有ARM处理器的现成仿真板。这是一种低成本高效率方案,其主要优点是便携性好,能让客户进行初始软件开发,而且还让我们对设计的RTL代码进行更详尽的试验,其数据输出能力明显高于仿真环境所能实现的程度。

从客户观点看,应用仿真环境背后的主要动力是客户以及客户的客户都能方便地开发应用代码,这种方式很成功。一旦开发出与仿真有关的测试和软件,问题的数量将会下降,但是发现的问题其复杂性和严重程度却增加了。最复杂的问题一般只能通过应用仿真之类的技术才能发现,使用仿真的主要目的是在RTL用到芯片之前更彻底地预先运行,因此先要把未修改的RTL用到FPGA中。

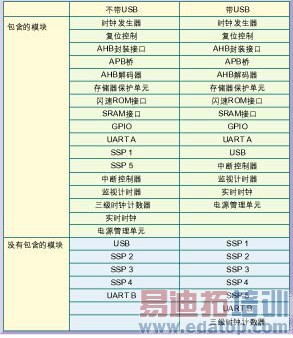

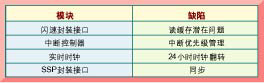

对于任何仿真方法,无论大小还是成本高低,都需要做一些折衷。系统速度必须可以按比例变化,就像我们的仿真方法一样,还必须考虑构建方案,因为一个Altera FPGA的容量是有限的。 HSPACE=12>器件内的SSP模块样式有重复,所以不需要所有的都做仿真。可考虑两种配置情况,详见表1。可以证明,对控制器进行仿真具有很大价值,表2列出了发现的一些问题。

时钟速度

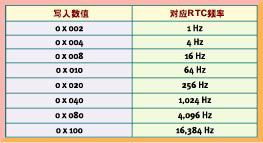

现在来看看与RTC有关的问题,我们设法通过提高时钟速度来检验。这可以让我们在数分钟内检验实时时钟的各方面,而不用等待实际那么长的时间。RTC时钟有个1Hz缺省值,此时RTC工作正常,把数据写入PMU中的RTC时钟分配器后将提高时钟频率。表3列出写入数值与对应的频率,其它所有数值都产生1Hz时钟频率。因此通过加速RTC模块以及在FPGA内调整UART设置输出以小时、分和秒表示的时间,就能观察RTC整个范围的周期情况。但显然,时钟范围为19小时59分59秒。

如果你认为这样的问题在仿真期间就应该发现而不应再在开发过程中传播就错了。不过我们确实忽略了这个问题,只有用更广泛的仿真试验才能发现缺陷。当一个客户将几千万美元投入到IC掩模和原型样片上最后却因为这样一个小问题而归为废品,用一句不恰当的比喻,就像事后诸葛亮一样没有任何意义。所以我们在时间和预算允许条件下,必须把测试做得更加彻底。

虽然我们有一个经过认可的流程,但并不是不会出错,有时它还会过于自信地认为永远都对。所以我们必须要不断地审核并使流程得到增强,以保持始终走在不断增加的验证挑战的前面。

本文结论

对于所有SoC来讲,有意思的地方经常是最具挑战性的地方,本文只谈到控制器设计的一个方面,还有其它许多挑战,包括:

?可测性设计问题,如嵌入式存储器测试

?STA问题,如现有的许多异步接口

?物理实现问题,如多结合方案

由于客户期望从其SoC设计上获得越来越多功能,这些都是他们需要解决的问题,必须与客户及硅片供应商密切合作,即使不能实现所有初始目标,也要尽量实现更多。这种做法的结果就是客户能够在收到初始样品的一周内做出最终应用产品,而且器件马上就可以推出并进入全面生产。

作者:

David Morrison

ASIC设计师

Tality Design Services

上一篇:利用自动测量提高线路板微通孔成品率

下一篇:利用成像技术进行测量