- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用以太网硬件在环路实现高带宽DSP仿真

System Generator for DSP提供适用于多种FPGA开发平台的硬件在环路接口,这些平台所提供的供PC机与FPGA硬件通讯的物理接口往往不同。例如,一个JTAG协同仿真接口就允许任何带JTAG接头的FPGA与赛灵思的FPGA在System Generator for DSP中进行协同仿真。有些其它板卡(例如XtremeDSP开发套件)则通过PCI总线与计算机进行通讯。到目前为止,仍然只有那些直接通过PCI或PCMCIA接口与PC机连接的开发板,能够进行存储带宽和数据吞吐量要求较高(例如视频和图像处理)的系统协同仿真。

通过以太网进行协同仿真

System Generator for DSP 8.1中包含一个新的以太网协同仿真接口,这个接口首次使赛灵思的ML402开发平台具备了高带宽协同仿真能力。ML402开发板可通过一根标准以太网电缆直接与PC机连接,或通过网络与PC机远程连接。

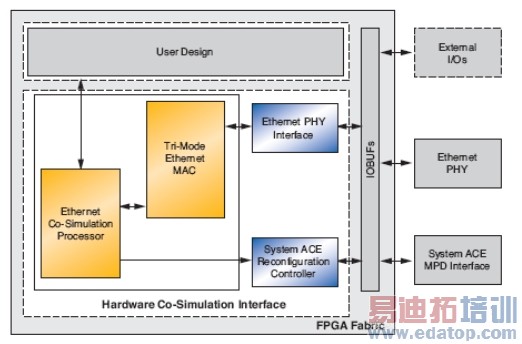

该接口的核心是赛灵思的三模以太网MAC核,支持10/100/1,000Mbps的半双工和全双工工作模式。当设计人员通过使用以太网硬件协同仿真接口生成一个设计时,System Generator for DSP将自动在设计周围建立必要的逻辑,从而在仿真的过程中通过以太网连接与FPGA进行通信(如图1所示)。

你还可以双击任意一个设计的System Generator模块打开它的参数配置对话框,从而生成一个用于以太网硬件协同仿真的设计。在编译菜单下,选择硬件协同仿真菜单下的ML402/以太网编译选项。此时,我们可以在以太网协同仿真的两种模式中选择一种。

图1:采用以太网硬件协同仿真接口的FPGA结构框图。

上一篇:浅谈ARM仿真器中的断点资源

下一篇:破除“万能总线”的神话,达成理想的测试系统!