- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

IBIS 4.1可以增强信号完整性建模功能

高速电路板设计过程中,需要对器件的I/O进行建模,传统的基于Spice的建模方法存在可移植性、速度、复杂性和开放性等问题。本文中介绍了IBIS建模方法,它以表格形式提供了表征和描述I/O行为的方法。在实际例子中,作者说明了基于IBIS4.1建模的具体步骤及其在缩短高速器件建模时间上的优越性。

|

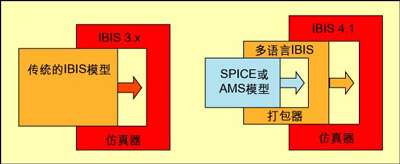

图1:传统的IBIS与具有 |

早期的器件采用的是TTL逻辑,那时上升和下降时间还很缓慢,因此不存在信号完整性问题。这种情况持续了不少年,直到20世纪90年代初,随着信号边沿速率达到了一个临界点,互连以及驱动器和接收器特性开始对PCB的正常工作造成严重影响。

那时,IC供应商提供足够详细的驱动器和接收器特征参数的方法就是从他们的IC设计中提取I/O电路,并将I/O电路网表以Spice模型表示,然后对Spice网表和潜在晶体管模型加密以保护他们的知识产权(IP)。不幸的是,这种解决方案存在下列问题:

1. 缺乏可移植性:每个Spice厂商都用自己的加密技术;

2. 速度慢:因为晶体管级设计所含的细节比SI分析所需的信息多得多;

3. 复杂:要求PCB设计师理解晦涩的Spice语法;

4. 不对外开放:还没有设立统一的Spice标准。

幸运的是,硅片与PCB供应商联盟认识到了这个问题,并设立了IBIS开放论坛委员会专门解决这些问题。最终形成的IBIS标准以表格形式提供了表征和描述I/O行为的方法。这种格式解决了加密Spice所引起的问题,因为IBIS标准是非私有的,不仅快速简单,而且具有可移植性。

|

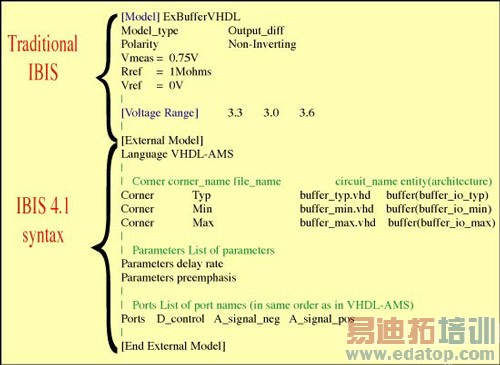

图2:显示了最新IBIS 4.1语 |

IBIS4.1的提出

随着技术的不断发展,IBIS标准能够很好地适应新技术的发展。然而,随着吉比特源同步(MGT)等复杂技术的出现,增加已有技术的复杂性很明显已经不能解决问题,这需要一种新的机制。

对IC供应商来说,最容易的短期解决方案是回到IBIS之前的状态,即建立并加密I/O网表,利用私有Spice进行仿真。幸运的是,IBIS委员会及时认识到了这一发展趋势,并开始增强IBIS功能以解决这一问题。最终于2003年批准了BIRD-75,并于2004年正式推荐为IBIS 4.1标准。这一改进为解决复杂MGT等带来的问题提供了渐进解决方法。

IBIS 4.1以较高的层次提供了在传统IBIS环境中使用Berkeley Spice 3F5、Accellera标准Verilog-AMS和IEEE标准VHDL-AMS的途径。此时,由IBIS文件提供互连性、门限值、差分引脚对和极限案例组织等高层信息,同时由Spice或AMS提供切换和量化特性等低层信息。

对于高速MGT器件来说,利用IBIS 4.1重新获得传统IBIS好处的第一步是简单的打包传统的加密Spice模型,这是使Spice模型更容易使用的一种非常有效的方法,但不能满足速度和私有加密要求,并且无法改变大多数Spice模型不能兼容IBIS 4.1允许的Berkeley Spice标准这一事实。

第二步是用Spice宏模型代替加密过的Spice晶体管模型。Spice提供了一些受控源和受控开关等可以用于组装基础行为模型的器件,宏建模时要将这些器件一块连接起来才能创建驱动器模型。

|

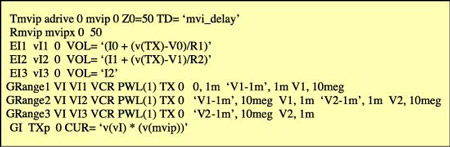

图3:延时三阻抗区电流源的Spice宏模型。 |

Spice宏建模有点类似于通过组合一系列UNIX或DOS命令快速实现某类自动操作的UNIX脚本或DOS中的批处理文件。但就象任何脚本那样,对于较大的任务宏建模将变得非常复杂,而且当遇到无法实现的命令时建模将无法进行。

当采用宏建模技术的工程师发现有必要使用非IBIS 4.1标准功能创建合适的模型时就会出现上述情况,因此,采用IBIS 4.1的宏模型可以解决速度和可用性问题,但不能解决Spice固有的非标准问题。

最后一步是用AMS模型替换加密过的Spice或宏模型。与传统的IBIS表式模型非常相似,可以对AMS模型加以修改完善,使其只保留源自驱动器或接收器的关键信息,而删除所有不必要的晶体管级详细信息。正是基于这样的原因,AMS模型的运行速度要比Spice晶体管级模型快数百倍,并且不需要加密。另外,由于AMS标准是公开的,因此任何SI工具供应商都可以获得该标准并在工具开发中加以应用。

同样,由于AMS是一种编程语言,它可以为建模者对当今器件以及未来技术和应用建模提供很大的灵活性。采用AMS语言后可以摆脱某些传统需求,如在IBIS标准中需要为新技术增加某些额外功能,然后等待标准被批准,再等待工具开发人员采纳这些新功能。

由于AMS仿真器既采用传统的模拟解算机,也采用事件驱动的解算机,因此用户还能获得更大的好处。事件驱动解算器可以将模型的逻辑和控制部分的仿真速度提高几个数量级。总之,AMS语言为IBIS的速度和开放带来了Spice独具的灵活性和精确度性,堪称完美之作。

|

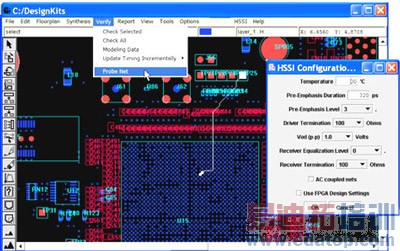

图4:具有可变上升下降时间的延时 |

IBIS 4.1

图1示出了与传统的IBIS 3.x相比之下的IBIS 4.1打包器工作原理。虽然乍一看IBIS 4.1多语言IBIS打包器似乎不是很必要,但事实上非常管用,是Spice或AMS模型的极好补充。

虽然该模型提供的是传统的电气仿真信息,但IBIS打包器可以提供原始模型用户无法提供的所有物理信息。这些物理信息可以极大地简化器件与整体仿真的集成工作,并为自动测试提供测量标准,同时提供其它一些能令模型更易使用的信息。

IBIS 4.1模型的内容行如图2所示,从中可以看出与传统IBIS 3.x模型的不同。关键词“external model”表示这是一个多语言模型。“Language VHDL-AMS”语句指出所用模型采用的是IEEE 1076.1 VHDL-AMS语法。IBIS“corner”语句功能已经得到增强,包含了VHDL-AMS源代码所在的文件名称以及实体-结构体对使用的名字。

参数行对PCI Express等可配置器件来说是非常有用的。用户可以利用这些参数快速修改驱动器配置,例如电压摆幅、预加重或接收器量化等,从而为他们的特殊PCB性能特征找到最佳的配置组合。

图3和图4给出了部分PCI Express驱动器的Spice宏模型样本和IEEE 1076.1 AMS语法,并给出了具有三个阻抗区的简单电流源模型。AMS模型规定上升和下降沿速率独立于触发器。Spice模型的上升和下降时间锁定于输入信号的上升下降时间。由于Spice没有提供if-then-else功能,因此利用了压控电阻来实现这个功能。

|

图5:采用IBIS 4.1模型分析U15的典型版图。 |

需要注意的是Spice宏模型是利用符合Berkeley Spice 3F5的器件编写的,但采用的不是Berkeley Spice语法,因为作者不能访问Berkeley Spice兼容仿真器,而Berkeley Spice仿真器都不具有AMS功能,因此不可能实现真正的测试基准。

用于SI分析的IBIS 4.1实例

不管是加密过的Spice、Spice宏模型还是AMS,一旦模型采用了IBIS 4.1格式,使用起来就非常简单。就拿本文作者最拿手的工具来说,仿真由IBIS4.1驱动器驱动的线径只需六个简单步骤:

1) 输入IBIS 4.1模型

2) 输入版图(或放置用于版图预分析的模块)

3) 将IBIS 4.1模型指配到一个部分

4) 选择网络进行仿真

5) 选择“探查网络”

6) 观察结果

图5给出了采用IBIS 4.1模型分析U15上的数吉比特输出的典型版图,该图同时示出了使用IBIS 4.1参数性能可达到的定制性。图中所示的HSSI配置菜单允许用户快速修改IBIS

|

图6:采用Spice晶体管级模型和 |

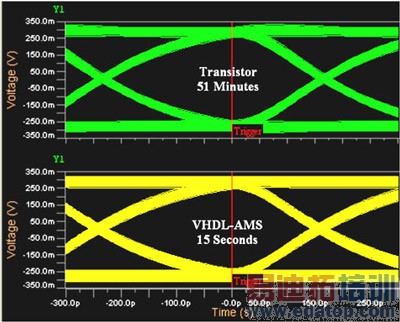

当然,根据所用模型的类型不同,步骤5和步骤6之间的时间会有很大的变化。对PCI Express驱动和接收器(互连走线长度为15英寸)的最近测试结果如图6所示。

值得注意的是,AMS模型的仿真速度要比Spice晶体管模型快200多倍,而得到的结果是一致的。Spice宏模型也产生相似的结果,但速度比AMS模型要慢一些。

结论

IBIS 4.1标准的新功能可以为当今和未来的技术提供创建工业标准SI模型所需的工具。有关IBIS 4.1标准的更多信息详见www.eigroup.org/ibis/default.htm网站介绍,有关支持IBIS 4.1和AMS的工具信息请登录www.mentor.com/ics。

作者:Gary Pratt

系统设计事业部高速技术经理

美国明导咨讯公司

上一篇:利用信号源预测串行器/解串器的抖动行为

下一篇:快速、准确、经济的浮动测量新方法