- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

利用信号源预测串行器/解串器的抖动行为

每个串行器/解串器(SerDes)都存在与频率相关的抖动特性。被抖动调制过的激励信号可以帮助设计师特征化SerDes的抖动行为,并避免由于选择了性能不兼容的器件而发生的设计问题。本文将讨论作为当今串行通信设备核心的串行/解串器在抖动测试方面存在的一些挑战和解决方案。

|

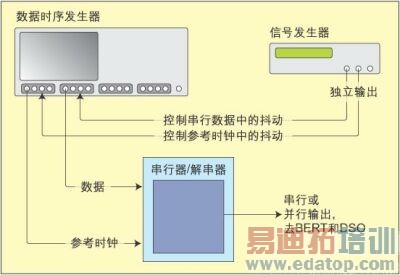

图1:典型的抖动测试配置中所连接的信号源。 |

信号抖动是串行器件设计师在兼容性问题方面面临的最大困难之一。由于现代串行器件的数据速率高,采用的又是嵌入式时钟,因此很容易受抖动的影响而降低比特误码率。被业界广泛接受的抖动容限定义已无法查明特定类型的故障,特别是与频率相关的抖动。

严格的测试对全面理解器件的抖动行为是非常必要的。通过测试和特征化一系列的抖动响应曲线就能预期抖动频率的敏感性。本文将讨论作为当今串行通信设备核心的串行/解串器在抖动测试方面存在的一些挑战和解决方案。

目标器件:串行-解串器(SerDes)

串行器-解串器是一个整体器件,它的名称通常被缩写为SerDes。串行器部分接收并行数据并将它转换成串行比特流。输入信号一般是8位并行数据,通常在上串行输出链路传输时还会利用某种编码方案将8位数据转换成10位数据。

解串器则是一个相反的过程。它接收串行数据,必要时进行解码,再转换为并行格式的数据。解串器还要恢复数据时钟,并把时钟和数据一起转发给后续的元件。SerDes中这2个互补的元件提供了一种将原始并行数据转换成串行数据从而进行高效传输的有效方式。

在SerDes中还有一个锁相环(PLL)模块,它接收系统参考时钟,并将它倍频到相应的数据速率。独立的取样器模块将使用这个倍频过的时钟锁定输入的串行数据。

SerDes抖动规范不全面

大多数SerDes器件规范都定义了确定和随机抖动容限。确定抖动与环境中发生的重复性事件有关,比如开关型电源供给晶体振荡器的工作。随机抖动则来自于系统内外非相关的事件。

值得注意的是这些规范省略了所有与频率相关的抖动行为方面的参考内容。随着抖动频率的提高,大多数SerDes器件更倾向于发生确定性抖动。另外,这些规范还忽略了时钟抖动效应,事实上时钟抖动的幅度和频率对抖动容限也有相当大的影响。

大多数情况下,在工作范围内正常工作的SerDes可能对系统设计中使用的频率具有抖动敏感性,很明显这将导致可靠性问题。

在有问题的频率点附近工作的可能性非常大,因此需要避免像开关型供电电源这样的设备工作于这些速率,但这样做意味着要降低其它重要的系统设计指标。最好的方法是预先刻划对频率敏感的行为特征,并选择抖动性能符合较大设计目标的SerDes元件。

抖动覆盖整个频谱

时钟抖动和数据抖动都会影响SerDes的比特误码率。PLL如何处理系统时钟中的抖动是问题的关键。PLL会将输入抖动传送到输出,输入输出之间的变化则取决于抖动频率。

|

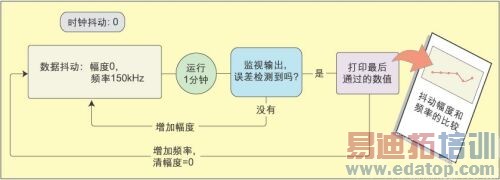

图2:抖动容限测量过程。 |

对目前典型的商用SerDes器件的响应作一总结可以更好地阐述上述问题。时钟抖动频率在直流到100kHz之间时,SerDes的响应是“平直的”,非常正常,输入时钟抖动线性地从输入传到输出。但在100kHz到1.9MHz时,PLL实际上会放时钟的抖动值。在大约1.9MHz时,抖动达到峰值,与线性区域相比大约高出33%,然后再急剧下降。时钟抖动效应实质上跨越了三个频段:低频、中频和高频。

1. 低频行为

抖动会引起个别取样数据偏离理想的取样时间位置。在示波器眼图中反应为眼睛的“关闭”;也就是说,眼图中应该张开的区域被那些错误比特污染了。然而,在低频情况下许多SerDes器件可以调整取样点以确保良好的数据捕获。在某些情况下这样做可以帮助它们跟踪等效于许多比特时间的抖动幅度。

现有的公式可以计算眼睛移动(关闭)的速率,抖动的频率和幅度是公式中的两个参数。但特定SerDes器件的实际值必须通过实验才能得到。

2. 中频行为

中频范围内的行为比较复杂。在该范围内时钟抖动和数据抖动都会起作用。PLL会把一些时钟抖动传递给取样器,而抖动的数据也会进入取样器。

时钟抖动和数据抖动将产生结构性或破坏性的干扰,取决于当时的具体频率值。如果时钟和数据分量同相,SerDes就能容忍较大的抖动,如果时钟和数据分量不同相,那么SerDes能够容忍的抖动值就比较小。优秀的设计师会考虑最坏的组合情况,并在数据抖动上增加调整过的参考时钟抖动。

3. 高频行为

由于时钟抖动在高频时影响很小,当时钟上的抖动频率一旦超过PLL抖动响应曲线下降部分时,就应该注重对数据抖动内容的分析。在这个抖动频率范围内取样器不再跟踪眼图的移动。

另外,眼图的整体完整性是决定性因素,只要眼睛睁得足够大,取样器就能正确捕捉到数据。

抖动测试

抖动测试取决于输入被测SerDes器件的数据和时钟信号的调制方式。抖动的一个重要特征是它的“包络”。这也是调制波形的包络,在抖动测试时它会影响结果柱状图的形状。包络有高斯、正弦、方形、三角形、随机等许多类型。在眼睛开度一定时,抖动包络对比特误码率(BER)有较大的影响。

正弦和三角形是抖动容限测试时使用的主要形状。与其它包络有更多尖峰不同,这两种柱状图在曲线下面都有一个相对矩形的区域。SerDes取样器寻找矩形区域的中间部分,并试图将锁存取样窗口放置在离中间0.5UI的位置。

正弦型抖动测试

业界广泛使用的正弦包络是一个很好的讨论例子。抖动测试过程是,先将各个正弦调制过的抖动源连接到SerDes的参考时钟和串行数据输入端,并针对抖动幅度和频率对两个源进行独立调整,同时监视输出的比特误码率。图1显示了典型的抖动测试配置中所连接的信号源。

抖动测试工具套件

抖动的发生需要使用良好集成的兼容性工具。信号的要求比较严格,数据/时序源的带宽和精度必须与目前的串行器件中使用的吉比特数据速率相兼容。时钟和数据信号上的抖动源应该独立于产生实际时钟和数据信号的振荡器。

另外,时钟和数据上的抖动应该相互独立(不锁相),同时两个信号应该独立进行控制。抖动的幅度和频率变化范围应比较大。

正弦波发生器(调制源)

正弦波发生器提供两个独立的输出,或者也可以使用两个发生器。正弦波的频率将决定被调信号上的抖动频率,它的幅度将决定信号上的抖动幅度。

|

图3:抖动容限测绘样例。红线表示时钟 |

数据时序发生器(时钟和数据源)

与正弦波发生器协同工作的是数字信号源,比如泰克DTG5000系列数据时序发生器系统。安装了DTGM31抖动发生器模块后,该系统就能接受两个调制输入信号,并对串行模式数据施加影响。模块的两个独立输出以与输入正弦波成比例地幅度提供抖动调制过的信号。

比特误码检测

在捕获侧,SerDes的比特误码可以用逻辑分析仪或比特误码率测试仪(BERT)进行检测。逻辑分析仪在误码时触发并捕获来自SerDes的并行数据,而BERT则捕获来自SerDes的串行数据。BERT再将捕获到的数据与来自数据发生器的参考模式数据进行比较。

数字存储示波器(DSO)

一旦确定比特误码发生后,示波器就开始测试实际的抖动幅度峰峰值,还能显示非常重要的眼图。一些示波器还有选装集成的抖动分析软件工具,从而极大地简化这些任务。

反复测试过程

图2给出了简化的测量和归档SerDes中抖动行为的过程示意图。图中给出了“典型”值,但个别用户可以根据被测器件特征选择不同的参数。虽然该图只提供了测试的数据抖动部分,但数据抖动值保持不变情况下的时钟抖动过程将遵循相同的步骤。

执行这一过程时需要考虑几个问题。首先,测试需要在无任何误码的条件下运行一段时间,这段时间最好足够长以致于能得到一个有实际意义的BER值。但通常长期误码是靠外推法推断出来的。

另外,测试模式数据必须要充分发挥SerDes的性能。工业标准样本是PCI Express 1.0a规范中定义的PCI Express兼容模式。

测试结果

最好的结果描述是一系列的曲线,每条曲线代表某个时钟抖动值下SerDes能够容忍的数据抖动值,每条曲线的时钟抖动(幅度和频率)保持在一个固定值。x轴代表时钟抖动频率,y轴代表抖动幅度。

曲线的产生过程是这样的:逐步增加数据抖动幅度并确定器件能够通过的最大值,通过的条件是指定时间段内不产生比特误码。不同的图形轨迹表示不同的时钟抖动频率和/或幅度。图3给出了以这种方式生成的二条曲线例子。

作者:Christopher Skach

应用工程师

Tektronix公司