- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

背板PTH压接孔的建模与验证

为了在背板信道中实现更高的数据传输速率,系统设计师要认真挑选系统所用的有源和无源器件。有源器件是在芯片上实现的电路技术,可以减轻信道上的一些有害效应。

为了使更高数据速率成为可能,无源器件供应商、封装、PCB和连接器供应商正在努力提供更低损耗、更好阻抗匹配性能和更低串扰的器件。通常集成电路芯片是组装在封装内的,因此自然会使芯片和封装供应商紧密合作从而尽可能提高封装器件的吞吐量。PCB供应商则通过沉孔(counter-boring)技术减小PTH过孔引线(via stubs)的长度,采用更低损耗的电介质材料来减少PCB走线损耗,并采用埋孔技术消除表贴连接器用的过孔引线。连接器供应商在设计背板连接器时除了需要考虑机械鲁棒性、热性能和可靠性外,还必须考虑引脚密度、板卡间距、易布线性、信号完整性等其它众多因素。

表面或压接(press-fit)安装的背板连接器的电气性能比要求较大电镀通孔(PTH)的传统压接连接器强,但它们的机械强度和可靠性较低。此外,这些连接器无法现场修理,由于需要克服较高的热能进行表面贴装连接器的回流焊,而可能无法达到背板的平整要求。

基于这些理由,系统供应商至今仍宁愿选用那些能够满足系统带宽要求的压接连接器。也正因为这个原因,连接器供应商仍在继续为12.5Gbps数据速率的设备开发合适的压接背板连接器。然而,即使连接器形状对压接、电镀通孔(PTH)的阻抗和串扰有严重的影响,但大多数连接器供应商的研发重点仍放在改进连接器本身的损耗、阻抗、串扰和偏移特性上。

某种程度上讲,过孔阻抗和串扰也取决于电路板设计中信号过孔所用的反焊盘横截面、电介质材料及尺寸。许多业界人士都认为PTH过孔的阻抗和串扰是背板信道性能的重要瓶颈。系统供应商被迫处理这个问题,因为是他们选择了所用的特殊背板连接器类型,并设计了过孔的特殊背板横截面和反焊盘尺寸。事实上,背板连接器的选择需要着重考虑的是连接器出现在实际系统中时的背板过孔阻抗和串扰。

基于以上考虑,为各种连接器形状创建精确的过孔模型是非常重要的,只有这样才能给信道仿真提供正确的过孔阻抗、串扰和损耗。一旦针对特定背板横截面建立了不同元件的过孔S参数模型,并与相应的连接器S参数进行了整合,从信号完整性角度看,就可以根据整合了所有系统元件精确模型的系统仿真结果作出连接器选用决定。

分散参数包含过孔的反射、传送、近端串扰和远端串扰,需要使用三维仿真工具CST Microwave Studio进行建模。具有不同反焊盘尺寸的各种连接器的背板过孔形状被制作于300mil厚背板上,并提取特征。这些模型也被转换成SPICE兼容的W单元模型。创建的模型S参数与测得的S参数相比较。过孔模型可以被包含进信道仿真内,并能在接收器输入端产生眼图。

消除PTH过孔引线

与厚背板上半部分中的走线层相连的过孔会有相当长的引线。这些过孔引线可以建模为一端开路的传输线。当引线长度等于四分之一波长的奇数倍(或双程时延等于半周期的倍数)时,一端开路的传输线输入端在该频率点就会发生问题。在这些频率点,所有入射功能全部被反射回发送端(Tx),接收端(Rx)收到的功率为零。

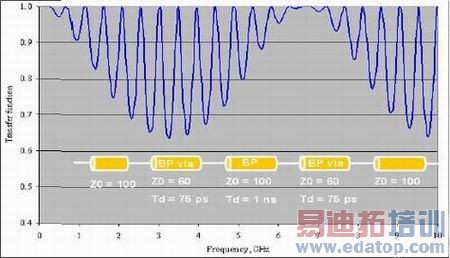

上述这种现象同样也会限制更小钻孔孔径、非压接孔的性能。为了更好地描述这种效应,将一端开路、时延为50ps的无损传输线附属于另外一条连接于发送到接收之间具有50欧姆特征阻抗(Z0)的无损传输线中间。这时的引线传输线具有二个Z0值,一个是30欧姆,代表具有较大钻孔孔径的压接过孔,另外一个是50欧姆,代表具有较小钻孔孔径的非压接过孔。在没有引线的情况下,Tx端信号将全部发送到Rx,中间不会有任何损耗,也即传输函数对于所有频率点都是一致的。

然而,传输线引线存在时传输函数就不同了。如图1所示,此时传输函数的谐振拐点将发生在5GHz处。数据速度为10Gbps的NRZ信号的奈奎斯特频率为5GHz。这就意味着即使链接传输线是无损的,其链接带宽也远小于10Gbps。这种情况下采用更好电介质材料或更小钻孔孔径都无济于事。更小孔径的过孔只能使谐振拐点变窄,从而获得比压接过孔更高的带宽。后钻孔是消除过孔引线导致的性能瓶颈的有效方法之一。后钻孔已被证明具有较高的可靠性和性价比,它能使引线长度缩短至5mil。消除非压接过孔引线的另外一种技术是埋孔,它常见于表面安装的连接器。压接过孔的一个缺点是,最顶层的走线层过孔为了配合压接连接器引脚及提供可靠连接,仍具有最长至80mil的引线。但由80mil引线引起的传输函数谐振拐点将发生在10GHz以外,因此不会对12.5Gbps数据速率的信号产生实质性的影响。

利用TRL对连接器和过孔组合进行建模

1. 校准方法

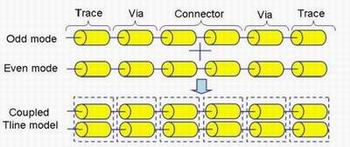

带穿透反射线(TRL)校准结构的测试板设计用于抽取连接器和过孔组合的模型。TRL校准可以去除发射寄生效应,并消除连接至压接PTH孔和连接器的一部分插头侧和插座侧走线。测得的S参数用于优化多段W单元传输线,而该传输线是连接器每边的剩余走线和PTH过孔以及图2中间的连接器的模型。这种模型对于连接器每边的通孔和引线孔这样的特殊组合是非常有效的。然而,这些建模技术的缺点是可能不适合过孔和引线过孔的其它组合情况。

2. 过孔测试结构特征

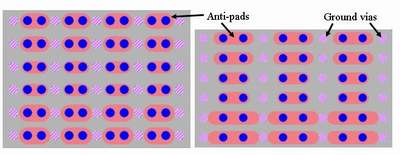

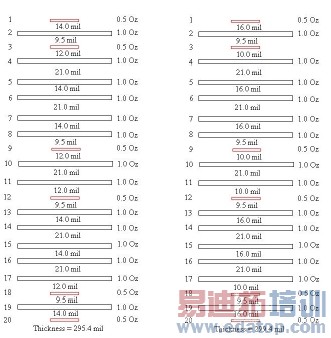

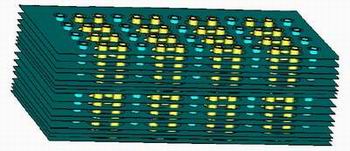

压接过孔测试结构特别针对300mil厚度、FR4和Nelco 6000(N6K)电介材料背板上的大量背板连接器插头形状而设计。图3所示是为HM-Z?/ERmet Z?和Metral 4000(M4K)连接器插头设计的过孔测试结构。这些过孔没有任何走线连接。HM-Z?/ERmet Z?形状的反焊盘尺寸是54.0 nil×59.1mil、67.0mil×59.1mil和74.0mil×61.1mil,Metral 4000形状的反焊盘尺寸是78.8 mil×48.0mil、110.0mil×48.0mil和150.0mil×78.8mil。背板的堆叠如图4所示。为了模拟厚背板的堆叠,即使在20层背板中只有4层实际的信号层,信号层的有效数量和总层数也将分别是13和28。

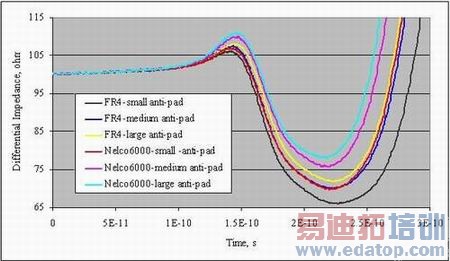

使用可直接放置于过孔焊盘上的差分TDR和微波探头可以提取差分过孔对的特征阻抗。过孔的另一边可以是开路的。为不同反焊盘尺寸、FR-4和N6K电介质条件下的HM-Zd/ERmet Z?连接器形状绘制的TDR图如图5所示。Y轴被转换成了阻抗。

较大的反焊盘尺寸和较低的介电常数材料可以减少电容负载,从而可以提高过孔阻抗,减小传播延时。可以在图中看到这些结果。GbX连接器具有相似的阻抗特性,而M4K和VHDM-HSD连接器的阻抗特性要稍好些,因为它们的信号与地引脚之间的间距较大些。从TDR波形可以看出,由于谷底非常窄,实际的过孔阻抗要比指示的还要低。

3. PTH过孔阻抗失配引起性能劣化

从测得的TDR波形看,最小的椭圆形反焊盘的PTH过孔阻抗最小为60欧姆。当然,如果使用小的圆形反焊盘,那些阻抗可以会更低。由60欧姆差分过孔阻抗和零引线长度引起的潜在性能损失如图6所示,而图6只考虑了背板插头孔引起的阻抗失配。无损信道被假定为完美导体和电介材料的模拟。这些过孔在时间上相距1ns,大约相当于6英寸长的背板尺寸。

PTH过孔建模

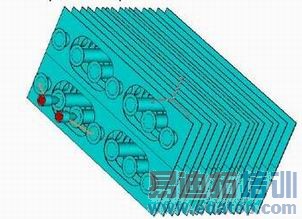

通过输入过孔尺寸、PCB横截面和推荐的电源和地层反焊盘,建模工具(3D)就能够有效地用于过孔建模。端口只存在于顶层和底层,在过孔旁边没有走线连接。建模的S参数适用于W单元传输线。当在信道仿真中实现过孔模型时,过孔传输线能被分割成二个部分,一部分代表信号通过部分,一部分代表引线部分。

三维时域仿真器“CST Microwave Studio”可用于过孔形状的建模。图7显示了为FR-4电介质材料小型反焊盘建模所创建的HM-Zd连接器形状。图8显示了采用大型反焊盘的相同连接器形状所用的端口激励。针对采用FR-4电介材料的大型反焊盘,一端开路的差分过孔对的建模单端反射和内部孔对耦合系数如图9所示。S12谐振拐点频率同步于6.2GHz,但在其它频率点仍有一些区别。

精确互连建模不仅需要精确的工具,而且需要正确的材料参数,如相对介电常数、介电损耗角正切值、高效的导体传导率和过孔钻孔直径的实际物理尺寸、钻孔角度、反焊盘形状以及电介质高度。另外,电介材料本身可能是分散的(依赖于频率的介电常数和损耗角正切值)。为了尽可能缩短仿真时间,模型省略了过孔或板边等其它周边结构,因此不能代表来自那些结构的耦合或反射。模型、波导或离散端口中使用的激励类型也会影响到仿真的结果。测试误差包含:校准误差(在校准基底上必须使用多个标准)、发送点误差(模型中的激励点和测试点可能不一致)以及探测误差(所用的探头超出目标频率范围)。这样使模型和测试相关性成为一个复杂和困难的过程。

本文小结

模型有助于预测损耗、反射、串扰和偏移等影响系统响应的电气性能。系统供应商为了作出设计权衡、系统预算、余量研究以及器件参数敏感度分析,需要使用高效的系统有源和无源器件模型。选用PTH过孔的系统供应商都愿意使用压接连接器,但压接连接器被认为是系统性能的重要瓶颈。PTH过孔可用测试结构特征化,并使用三维仿真工具建模。本例建模和测试时考虑了2个连接器形状和3个反焊盘尺寸。

需要设法尽量减小数据速率在5Gbps以上的压接PTH过孔的影响。好消息是在典型的背板环境中不是所有链路都易受反射和串扰的侵害。通过仔细选择背板的引脚输出也可以减小易受侵害链路上的串扰。更低的介电常数材料、更大的反焊盘、更薄的背板以及使用宽耦合的走线(可减少背板中地层的总数量)都有助于减小压接过孔的有害效应。如果我们能正确地使用这些技术,那么压接连接器就能成功地通过高达12.5Gbps的数据速率。

作者:Ravi Kollipara

Rambus公司