- 易迪拓培训,专注于微波、射频、天线设计工程师的培养

Post-layout分析应对纳米设计挑战

在当今竞争日益激烈的国际市场,设计高端IC面临着前所未有的压力:既要能够发布一次投片成功的设计,又要面临十分严酷的既定日程。虽然工艺技术快速发展到130纳米甚至更小,但设计者们却发现他们面临的设计挑战严重影响他们成功发布一次投片成功的设计。在纳米尺寸,微妙的电学和物理效应超越传统的分析能力,导致这些设计虽然通过了Sign-off却不能实际工作。重复投片导致显著增加的附加费用和错过创造最佳市场价值的时机。终于,设计者们发现,详细的post-layout分析是纳米设计中揭示潜在的毁灭性缺陷的最有效手段。然而,传统的分析工具无法处理超大规模纳米设计中如此巨大的设计数据量。结果,导致设计者们在设计验证高端纳米设计时面临一个严酷的危机,即在明知有很多潜在的纳米相关的问题还没有克服的情况下就去投片生产。幸运的是,越来越多的post-layout分析方法,诸如本篇所描述的那样,使得详细的晶体管级验证和分析成为可能,帮助纳米设计能尽快投片成功。

先进的工艺技术高度发展,使得设计者能实现复杂Mix-signal的SoC(系统级芯片),能把数以千万计的晶体管包含到设计中并在芯片内部以GHz运行。当他们的设计变得更大却更密时,他们的电路表现出于一系列的、主要是与内部互连线相关的纳米效应:比如由于耦合电容导致的互耦以及电感效应,这些将导致窜扰噪声和其他信号完整性问题;与日益增大的市场压力一起,先进的纳米工艺技术给现存的设计流程以巨大压力。

而往日的经验已不能应对当今纳米领域的挑战,超过一半的高端设计需要超过一次的重复投片,这导致巨大的费用和上市时间的推迟。

同时,设计者们发现,他们必须在确保设计安全运行和获得较高性能之间进行权衡,必须留出足够的margin,这种牺牲设计性能的权衡使他们十分痛苦。

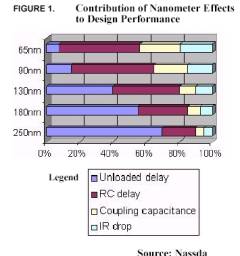

现有的设计流程是以传统的主要是关注pre-layout门级设计,这首先就缺乏纳米级设计所要求的精度,其次没有可供分析纳米效应的数据基础。事实上,高端设计公司正在发现门级描述中忽略了能用于辨识解决纳米效应的细节。其他一些基于静态时序分析的方法,不管是否是晶体管级的,都不足以分析纳米效应中的动态现象,因为像耦合噪声,IR Drop等都是与时间相关的,这都需要动态的分析手段。随着工艺技术的进步,这些主要由互

连线效应占主导的纳米效应正主导着纳米设计的性能。如图1所示:

0.25um工艺时,由互连线效应导致的延时为+30%;

0.18um工艺时,由互连线效应导致的延时为+50%;

0.09um工艺时,由互连线效应导致的延时超过80%.

晶体管级分析

为了揭示潜在的纳米设计问题,设计者需要在晶体管级分析他们的设计,因为在晶体管级才是这些纳米现象发生的地方(当然,必须拥有从post-layout中提取的寄生参数)。纳米设计中出现的问题是由于在细小的、高密度的设计单元之间的产生的物理和电学效应,而日益先进的工艺技术使得这些效应日益凸现;同时,把从物理设计中提取的实际寄生参数值准确地反标回去对精确分析这些现象至关重要的;那些试图依靠把估算的缺乏精度的寄生参数值简单得插入pre-layout分析流程仅仅能提供最基本的帮助,在大型、高速的纳米设计中,没有准确的寄生参数值,设计者将陷入痛苦并且昂贵的设计迭代中。

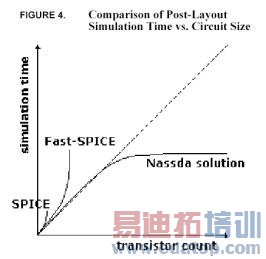

尽管晶体管级分析对于纳米设计至关重要,但是EDA工业界没能及时提供应对的合适工具。传统的晶体管级SPICE仿真器不能处理超过2万最多不超过5万元件的处理能力,包括晶体管、电阻和电容;而且由于要求解复杂的矩阵方程,常常化去数小时甚至数天去完成仿真运算。在80年代中期,第二代的电路仿真器,或称之为FAST-SPICE的工具诞生,能够解决更大的容量和速度需求,这其中采用了许多革新的关键技术,包括:

电路可以被划分成一些相对独立的,互相通过沟道相连接的子电路单元。

每一个独立的子电路单元可以被一些“事件”所触发而动作,如加在端口上电压、电流的变化。仿真器只对被“激活”的子电路单元计算其结果。

“事件”驱动的FAST-SPICE方法在以近似、甚至完全忽略子电路单元之间的相互耦合的前提下,假设信号在每一个“事件”到来后,接受这些“事件”的子电路单元可以触发一些相连接的子电路单元进入“激活”状态(仿真器会计算其结果)。在这种简化和假设条件下,事件驱动的FAST-SPICE仿真器最多可以处理2-3百万个晶体管的前仿真。在这样的前提下,“事件”驱动的FAST-SPICE仿真器的速度和容量远远的超过了传统SPICE仿真器。

对于Post-layout仿真,由于寄生参数的引入而破坏了事件驱动的FAST-SPICE仿真器对电路进行仿真的前提----每个划分开的子电路单元保持独立且互不耦合!无论这些子电路单元是否处于“激活”状态,通过信号网络,寄生耦合电容把不同的子电路单元连接起来,在这种状况下,子电路单元的规模迅速扩大。更加严重的是,与电源网络相关的寄生电容把整个电路都耦合在一起了。此时,“事件”驱动的快速SPICE仿真器所面临的是一个规模空前巨大(是pre-layout的几百倍甚至上千倍),而且又永远处于“激活”状态的子电路单元,要用“事件”驱动的快速SPICE仿真器对这种大的电路单元进行仿真是不可能的,要么是仿真速度极慢,要么是基本就不能仿真!

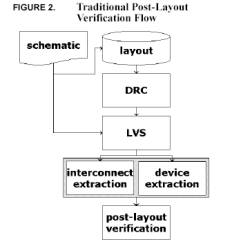

传统的post-layout流程

虽然post-layout设计流程在验证纳米设计中扮演重要的角色,然而这套流程却远不如pre-layout流程那般成熟。直到最近,流程中的一些瓶颈工具才得以实现,能够较为完整的串起整套流程。图2是传统的Post-layout验证流程。

物理验证:在版图设计完成之后,设计者要进行基本的版图验证阶段包括DRC(设计规则检查)、LVS(版图原理图一致性检查)。在这一阶段,设计者也进行一些二维或是2.5维的参数提取来做一些早期的post-layout分析,虽然这样的提取不够准确,但设计者仍能从这些初步分析中获得对最终设计的较为完整理解。

网表提取:设计者提取一张打平的SPICE网表,这个过程称之为LPE(版图参数提取);整个过程从版图中获取正确的晶体管几何尺寸和连接关系。

参数提取:在这个阶段,设计者提取互连线主要是信号网络的寄生参数。往往一个全芯片的完整提取要花费数天甚至数周的时间,由于传统工具的处理能力有限,提取的参数中仅有一部分能被用于分析,所以这个过程的效率非常低。由于这些原因,在过去,设计者们被局限于只做一些关键路径的post-layout分析,这种方式从根本上讲是向精确度做的一种妥协。当验证工作只能被局限于一系列的子电路时,一些类似竞争冒险和其他时序问题就无法被发现。例如,关键路径分析仅仅对信号网络的耦合效应进行建模分析,而对相关的电源网络的电压降(IR Drop)无从着手。结果,设计者常常面临一些不可能完成的任务,即必须谨慎的评估数值或凭着不完整的或不确定范围的分析结果来做重大的设计决策。提取的巨大的寄生参数使原本复杂的post-layout流程更加艰巨,当今数百万晶体管的设计所提取的平坦的网表会比层次化的pre-layout网表大一个数量级。

传统的针对信号网络的提取方式,每条网络仅仅产生数百个寄生电阻和电容,即使是时钟网络可能也只产生数万个寄生元件;相对而言,全芯片的、包括耦合电容和电源网络寄生参数提取结果将包含数百万个寄生元件——超过传统SPICE和FAST-SPICE工具的能力范围。结果,设计者们发现面对着越来越复杂的验证要求,他们的分析手段被严重束缚。举个例子,2M的SRAM进行全芯片的平坦提取会产生1,300万个晶体管和5,000万个寄生电阻和电容,而文件规模将达到5G。而今日的高端设计中,面临的往往是更大,几何级数增长的寄生参数提取文件。为了解决数据量激增的情况,先进的post-layout工具应用了一系列的算法和试探方法以减少寄生元件的数量但却可以足以揭示潜在的纳米效应。例如,新的RC约减工具可以将一个5G的DSPF文件精简到几十兆,这使设计者能够在保持精度的前提下在允许的时间里运行仿真验证。

层次化反标

使用高效的参数精简技术,全芯片的SPICE精度晶体管级分析方法能够识别出今天设计中的纳米效应。今天先进的post-layout工具能够把寄生参数反标到pre-layout层次化网表中,这种方法在保持SPICE精度的同时显著得增加了验证的能力和减少了验证的时间。其他的复杂技术,像Nassda专利的的同构匹配技术,能极大得提高仿真性能。使用这种技术,仿真器对于重复的电路元件不再进行重复计算,这极大得提高了运行速度和计算容量。这种高性能、大容量的仿真能力帮助设计队伍能进行高效的纳米设计验证。全新的post-layout流程包括:

全芯片的pre-layout仿真:在设计的早期阶段,设计者们把预估的参数值加入pre-layout仿真中做全芯片的仿真,来获得对最终设计的时序有比较准确的预估。全芯片的仿真要比仅仅分析关键路径要可靠的多;通过这种方法,设计者能在设计的早期阶段揭示潜在的纳米效应,使得在接下来的物理设计过程中减少不良影响和减少设计迭代次数。

物理设计(Physical Design):物理设计阶段与通常类似,进行版图设计和物理验证,只是经过验证的数据使前一阶段的设计更为高效。

参数提取(Parasitic Extraction):设计者提取,精简以及把提取的RC参数反标到pre-layout的层次化网表中,以提取的精确值替代预估的pre-layout参数值。由于这种方法即保留了pre-layout的设计层次,使设计者能体验一种从pre-layout到post-layout无缝的过渡,且能迅速的识别、寻找和解决由于窜扰或电压降等纳米效应带来的设计问题。

Post-Layout验证:设计者使用精确的post-layout参数,进行全芯片的晶体管级验证来解决的设计中的纳米问题。与其他传统验证方法一起,来识别和验证那些将导致流片失败的问题。

Sign-Off: 在tape-out阶段,有了前面全芯片的晶体管级验证过程,设计者能对设计的sign-off充满信心,相信最终的流片结果会与预测性能相接近。

事实上,成熟的IC设计公司逐渐意识到全芯片的post-layout晶体管级仿真可以减少设计上的风险和财务上的不利。他们的设计队伍已经完成了纳米设计sign-off流程,拥有了全芯片的晶体管级post-layout验证手段,设计者们不仅可以辨识和纠正潜在的纳米问题,而且可以对时序和功耗特性进行可能的最大程度的优化;因为所有的决定都是基于layout完成后比较精确和全面的关键特性分析的基础上做出的。这样,设计者能更容易的对付最关键的post-layout问题,包括窜扰(涉及噪声和延时)和IR Drop对电路特性的影响,以及由电感效应引起的地弹,甚至包括热噪声和电迁移分析。有了这样精确的分析后,设计者们只需在需要的地方加入gardband,其他地方可以设置较为宽松的环境以提高设计性能和减少芯片面积。带来的好处也显而易见:缩短设计验证的周期,缩短time-to-market的时间并最快最大的创造市场价值。

Nassda的Post-Layout分析解决方案

当今,post-layout分析工具,诸如Nassda的HSIM和LEXSIM,能够提供解决纳米设计post-layout验证和分析的能力。1999面世的HSIM是工业界第一个商业的层次化的电路仿真器。基于Nassda专有的技术,HSIM结合了全芯片晶体管级验证所需的特殊技术,包括:

层次化存储技术:以减少工作站内存和磁盘空间占用,能为当今高端的数百万晶体管级电路提供一个高效率的层次化数据处理机制;

层次化的RC精简算法:用以在层次化电路数据结构中压缩寄生电阻电容的个数同时保持很高的精度;

高效的层次化的矩阵方程求解器:使得电路仿真能在实现层次化的同时保持SPICE精度;

由于拥有些独特的专有技术,HSIM拥有能够处理全芯片的几乎没电路规模限制的能力。Nassda的专利的同构匹配技术和层次化矩阵求解技术使得仿真速度显著提高,而且不需使用降低仿真精度的诸如使用简化的仿真模型和裁减算法的妥协方法。事实上,通过组合这些算法,HSIM能够完成全芯片数百万晶体管级设计的SPICE精度的仿真,但使用的时间却是传统方法的数百分之一甚至数万分子一,而精度却能逼近SPICE的精度。

2002年面市的LEXSIM,使用和HSIM相同的算法基础之上,拥有了更为优化和增强的能力,包括在层次化的寄生参数反标、电源网络精简和IR Drop分析,以及高效的层次化耦合电容的处理能力。LEXSIM是第一个商业的EDA工具,能够在复杂的纳米内存设计中对IR Drop分析提供直接耦合的解决方案;而传统的方法需要做两步,这样在处理的过程中会丧失捕捉动态纳米效应的精度。LEXSIM通过进行全芯片晶体管级post-layout、包括电源网络的分析,不但能够精确分析IR Drop,而且能判断其对高性能的敏感的纳米级内存设计多产生的影响。即精确又快速的分析能力得益于Nassda专有的、对电源网络的精简和层次化反标的技术基础。

LEXSIM优化了HSIM中对信号网络的精简技术,加入了对大数量的耦合电容更高效的处理机制,在达到高速度仿真效果的同时,精度的牺牲很少。LEXSIM特有的层次化反标技术保持了pre-layout的设计层次化,使得在整个设计流程中始终如一的表达设计结构;拥有这个技术,使得LEXSIM能够处理比HSIM更为丰富的设计层次,处理更为复杂的全芯片级的仿真任务。

此外,这种能力使得设计者能够使设计者更容易的应用post-layout验证技术作为pre-layout流程的增量流程,相比之下,传统的电路分析工具使用的反标技术必须在电路处理时打平网表,对于处理电源网络那样全局耦合的网表,这种平坦化网表的过程显著得减少了最大电路的处理能力,在保持post-layout和pre-layout一致性方面也有重大的局限性。传统的SPICE或快速SPICE工具只能让你拥有容量、速度和精度的其中两项。Nassda独特的post-layout仿真技术,不但在容量和速度上有极大的提高,而且能给用户提供SPICE的精确度。

结论

面临当今的竞争压力,IC设计公司必须依赖越来越先进的工艺技术以提高其产品的竞争能力,然而,先进工艺技术在带来更高的工作频率、更高的功能密度的同时,也带来了寄生的电学和物理效应,这些给设计者获得第一投片成功带来巨大的挑战。纳米效应只有使用精确的post-layout寄生参数反标,通过详细的晶体管级验证和分析才能精确的被揭示。传统的电路仿真工具无法应对这么巨大的设计和寄生参数的数据量;其次,局限的进行关键路径分析不能提供给设计者完整的设计性能蓝图,从而在流片之前获得充分的信心。新一代的层次化的仿真工具,像Nassda的HSIM和LEXSIM提供了对纳米设计全芯片、晶体管级、SPICE精度的分析能力和处理速度。使用这样强有力的工具,使IC设计公司对更可靠的硅精确度晶体管级sign-off要求的验证手段有了依靠,使得设计公司有能力更好得控制设计的性能、可靠性和良率,能够更有信心的推动复杂设计在先进工艺线上生产。由于有了全芯片的晶体管级验证手段,设计公司虽然面临着日益增加的市场竞争压力和设计挑战,仍能够快速的发布他们优化的、充分利用先进纳米工艺技术潜力的硅产品。

作者:仲佳明

冠讯科技有限公司

jimmyzhong@acro-da.com

上一篇:体现/实现三维线内锡膏检测的优点

下一篇:通过自动测试降低宽带语音传输的运营成本